大家好,我最近自己開始進行VHDL編程。因為幾個錯誤而陷入困境。我在VHDL的結構代碼中得到3個錯誤。其中一個錯誤是“模型”和“2”在目標庫中具有不同的特征。用戶組件'和2'與庫原語'和2'沖突請幫幫我。我附上了錯誤的屏幕截圖,請檢查它們并幫助我繼續進行

2020-03-30 10:00:12

語句第7章 VHDL的描述風格7.1 行為描述7.2 數據流描述7.3 結構描述第8章 仿真8.1 VHDL仿真8.2 延時模型8.2.1 固有延時8.2.2 傳輸延時8.3 仿真Δ8.4 仿真激勵信號

2008-06-04 10:31:29

但是寫完語言后創建VHDL測試臺顯示,我的vhdl中有實體與文件名一致,這樣也就無法通過vhdl生成原理圖,我使用的是***2004

2015-04-01 21:28:34

我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解我對運放的理解

2012-09-23 15:02:07

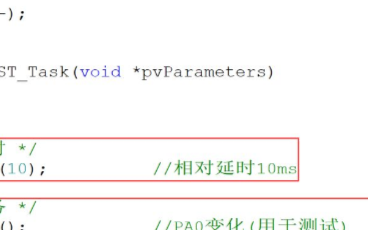

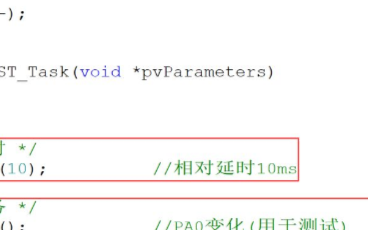

我想問一下,在STM32外部中斷中我需要用延時,我該怎么延時?

2017-09-11 18:02:30

`我是FPGA初學者 ,我想問下 ,有vhdl 的程序 ,但是沒有工程文件 ,我要添加哪些文件才能運行vhdl程序。怎么添加程序才能運行生成工程文件。`

2015-12-29 21:28:10

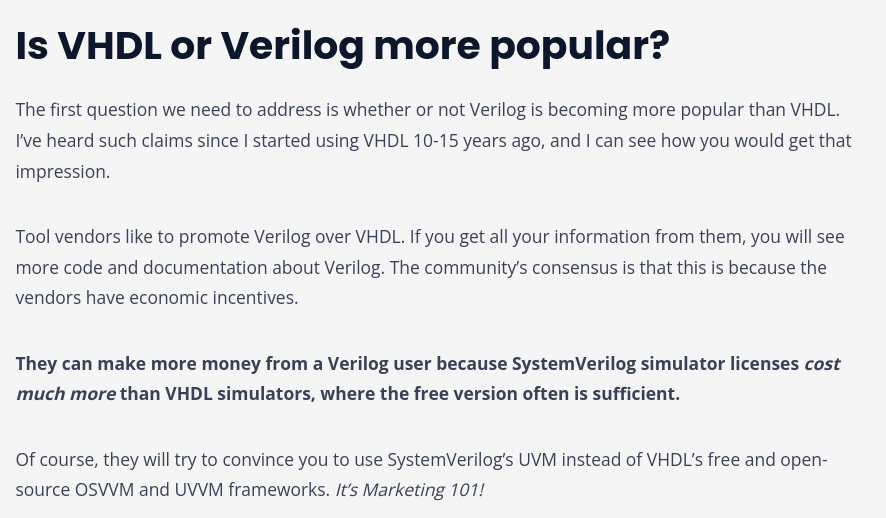

大學的一些學習材料。可是最近有點迷茫,是學VHDL呢?還是學Verilog HDL。我網上查,有的說VHDL和Verilog HDL應用情況差不多,可是又有人說現在主要是用Verilog HDL。個人

2013-09-06 15:03:08

我的altium designer 編寫好vhdl后并成功在原理圖中生成了電路,最后進行測試也就是testbeach時在生成的.VHDTEST文件中進行了少量修改是按書上寫的,應該是沒問題的,前面

2015-04-02 20:39:30

VHDL 主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL 在語言形式、描述風格和句法上與一般的計算機高級語言十分相似。VHDL 的程序結構特點是將一項

2018-09-07 09:04:45

我是UCOS初學者,以前也沒有學過任何RTOS,望大神說的仔細些。我所理解的UCOS任務調度都是在延時函數中實現的,假設我定義了三個函數:1-start_task ; 2-task1

2020-04-07 22:13:19

原子哥,你好,問下,使用OSTimeDlyHMSM()或者OSTimeDly()延時函數,會引發幾次調度?我的理解是兩次,一次是剛進入延時函數時,另一次是當延時函數結束時,不知這樣理解是否正確?

2020-04-21 04:35:55

大家好 ,我想創建一個自定義的冷杉過濾器,但我沒有足夠的知識來設計它。所以我可以訪問vivado的fir編譯器vhdl代碼,這可以幫助我理解流接口和自定義IP塊的方法。我有一個簡單的冷杉過濾器

2020-04-07 08:37:48

嗨,我試圖理解“write_vhdl”和“write_verilog”之間的差異。我有一個設計,我想從中創建一個網表。設計是用VERILOG編寫的,我用“write_verilog”命令創建了一個

2020-03-16 10:29:57

你好!我是FPGA設計的新手。我想在我的項目中使用DCM,但是,在我執行Xilinx時鐘向導之后,沒有生成響應的vhdl文件。我想知道我該怎么生成這個vhdl文件。我還有其他步驟嗎?謝謝你的考慮

2019-01-15 10:22:23

程序如下,這樣的話在num賦給n的時候,num也同時被置0吧?怎么延時執行f進程呢?想了好久,求解呀!!!g:PROCESS(en)BEGIN IF en'EVENT AND en='0'THEN n0

2012-11-22 17:55:49

” 定時器做延時 比 軟件延時 CPU利用率高 “,在我看過的一個按鍵狀態機的程序里,覺得確實是這樣的;但程序有延時的地方好像并不能都寫成 狀態機 那樣的結構啊,這時我就不能理解為什么說 ” 定時器做延時

2015-08-03 21:55:23

掛起之后。1.5ms之后就會進入節拍的中斷函數中。然后任務又會進入就緒狀態。此時目標延時應該為5ms,但實際延時只有1.5ms。這樣延時函數就會產生誤差。不知道我理解的是否正確?如果確實如我理解的這樣,那又該如何保證實時性呢?

2019-09-16 20:58:20

PLZ任何機構都可以建議我如何在vhdl代碼中編寫Expectation maximization algo。我知道理論,但無法理解編碼的方式.plzzzzz的幫助。以上來自于谷歌翻譯以下為原文

2019-01-23 07:02:02

作為我項目的一部分,我需要將ADC與7系列FPGA接口,我有一個SelectIO?接口向導的IP核。但是,我的整個項目都在VHDL中,IPi得到的是Verilog。請指出我如何在我的VHDL頂級模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

我想用DNA(XC6SLX16)加密我的設計,但我不知道怎么做,有沒有人可以提供一些VHDL參考?以上來自于谷歌翻譯以下為原文I want to encryptmy design

2019-07-24 13:19:40

大家好,我想使用IO時鐘接口對輸入中的串行信號進行過采樣。然后,該信號將由vhdl編程邏輯與全局時鐘一起使用。我希望使用IO時鐘以更高的頻率對這些輸入數據進行采樣,而不是全局時鐘提供的數據,但我

2019-08-07 09:51:55

將由自定義VHDL代碼寫入。第二個BRAM地址在Microblaze上為0x00010000。在導出BRAM的第二個端口以供自定義VHDL代碼使用之后,我對VHDL端的BRAM地址感到有些困惑

2019-03-04 12:09:00

你好我正在處理導入vhdl文件到EDK項目中的pcores-user_logic。我創建了我的系統并將vhdl輸出連接到我的EDK系統。但是當我生成比特流時,我得到的錯誤就像“無法在庫中找到。請確保

2019-03-19 06:11:26

嗨,我喜歡vhdl和fpga。有人告訴我,我們可以使用simulink生成vhdl。我想處理寄存器,查找表和累加器。我只知道simulink上的基本知識。任何人都可以建議哪種方式最好。如果

2020-03-20 06:16:39

用VHDL寫,步進延時電路的設計,電子設計大賽07年C題中關于步進延時的設計

2013-08-05 09:54:45

大家好,我對VHDL有點新意,我想在你學習數字設計的同時,對你知道對VHDL有益的書籍有所了解。那么那些真正優秀的書籍是什么?

2020-05-22 06:42:27

正在學習VHDL,有一個問題不知道咋實現,希望大家幫忙。輸入信號 I_moen 和I_boen,輸出信號 O_mo 和O_bo。要求:1.I_moen出現上升沿, O_mo轉為高電平;同樣

2019-01-25 06:35:20

你能告訴我用戶邏輯是什么嗎?我理解的是user_logic是vhdl模板的主/從ip實現的?我對嗎?無論如何,如果你能詳細說明一下,我會很高興非常感謝您的幫助!!

2019-11-11 13:54:56

The VHDL Cookbook

好東西哦。網上搜集,希望對你有用。

2006-03-25 14:37:55 19

19 VHDL硬件描述語言教學:包括fpga講義,VHDL硬件描述語言基礎,VHDL語言的層次化設計的教學幻燈片

2006-03-27 23:46:49 93

93 第1章 緒論 1.1 關于EDA 1.2 關于VHDL 1.3 關于自頂向下的系統設計方法 1.4 關于應用 VHDL的 EDA過程 1.5 關于在系統編程技術 1.6 關于FPGA/CPLD的優勢 1.7

2008-06-04 10:24:06 1682

1682

VHDL的定義和功能VHDL的發展概況程序編程語言和硬件描述語言的對比引入硬件描述語言對系統進

2008-09-03 12:58:41 39

39 A CPLD VHDL Introduction

This introduction covers the fundamentals of VHDL as applied to Complex

2009-03-28 16:14:37 25

25 VHDL基本語法實例:

2009-05-27 08:57:49 11

11 VHDL基本語法實例:

2009-05-27 10:32:19 123

123 UART 4 UART參考設計,Xilinx提供VHDL代碼 uart_vhdl

This zip file contains the following folders

2009-06-14 08:57:14 114

114 VHDL Library of Arithmetic Units fdl

A comprehensive library of arithmetic units written

2009-06-14 09:09:30 17

17 VHDL語言及其應用是在作者歷時七年為通信與信息系統、信號與信息處理專業研究生講授VHDL語言及其應用課程的教學實踐基礎上編寫而成的。全書共分15章,以教授完整的VHDL語言體

2009-07-10 17:21:44 18

18 VHDL語言及其應用的主要內容:第一章 硬件模型概述第二章 基本的VHDL編程語言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應用樣例附錄A VHDL

2009-07-20 12:06:15 0

0 VHDL語言概述:本章主要內容:硬件描述語言(HDL)VHDL語言的特點VHDL語言的開發流程

1.1 1.1 硬件描述語言( 硬件描述語言(HDL HDL)H

2009-08-09 23:13:20 47

47 1. INSTANTIATING LPM in VHDLTo promote LPM usage in VHDL design community, this section describes

2009-09-13 14:29:03 26

26 VHDL 語言程序的元素:本章主要內容:VHDL語言的對象VHDL語言的數據類型VHDL語言的運算符VHDL語言的標識符VHDL語言的詞法單元

2009-09-28 14:32:21 41

41 vhdl數字系統設計是數字電路自動化設計(EDA)入門的工具書。其內容主要包括:用VHDL語言設計的基本組合電路、時序電路、數字綜合電路、電路圖輸入法要領概述、實用VHDL語句

2009-10-08 21:54:01 0

0 VHDL基礎教程:VHDL語言及其應用目錄:第1章 VHDL基本概念 1.1 數字系統建模 1.2 建模的域和級 1.3 建模語言 1.4 VHDL建模的概念 1.5 一個VHDL設計實例 1 6

2009-10-16 18:17:58 359

359 VHDL 數位電子鐘在這個數位電子鐘我們使用可支持VHDL 格式的MAX+plusII 軟件開發工具來做設計,利用VHDL 硬件描述語言的方式,將一個復雜的電路寫成一顆IC,有錯誤也不用像以前

2009-11-22 17:50:38 174

174 VHDL深入教程

2009-12-05 16:33:18 199

199 VHDL實例大全

2010-04-19 13:58:00 240

240 電子鐘VHDL設計

電子鐘VHDL設計

標簽/分類:

1.系統設計要求 (1)具有時、分、秒計數顯示功能,小時為24進制,分鐘和

2007-08-21 15:31:05 4647

4647 vhdl是什么意思

VHDL 語言的英文全名是 Very High Speed Integrated Circuit Hardware Description Language ,即超高速集

2008-09-02 12:55:59 8815

8815 實驗六、VHDL的基本描述語句設計一? 實驗目的1掌握VHDL語言的基本結構及設計的輸入方法。2掌握VHDL語言的基本描述語句的使用方法。二? 實驗設備

2009-03-13 19:23:57 2351

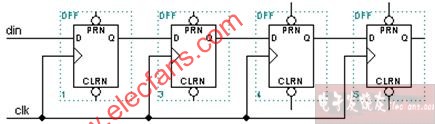

2351 實驗七、VHDL并行語句(生成語句)使用練習一? 實驗目的1掌握VHDL語言的基本描述語句的使用方法。2掌握VHDL語言的生成語句的使用方法。二? 實

2009-03-13 19:25:10 2971

2971

實驗八、VHDL語言的組合電路設計一? 實驗目的1掌握VHDL語言的基本結構及設計的輸入方法。2掌握VHDL語言的組合電路設計方法。二? 實驗設備與儀器

2009-03-13 19:26:58 2946

2946 VHDL語言應用實例指導

VHDL中的標識符可以是常數、變量、信號、端口、子程序或參數的名字。使用標識符要遵守如下法則

2009-03-20 14:15:53 2355

2355

用VHDL設計專用串行通信芯片

一種專用串行同步通信芯片(該芯片內部結構和操作方式以INS8250為參考)的VHDL設計及CPLD實現,著重介紹了用VHDL及CPLD設計專用通信芯片的

2009-10-12 19:07:48 2154

2154

數字電壓表的VHDL設計與實現

介紹數字電壓表的組成及工作原理,論述了基于VHDL語言和FPGA芯片的數字系統的設計思想和實現過程。 關鍵詞:數字電壓表;VHDL語

2009-10-12 19:14:32 2145

2145

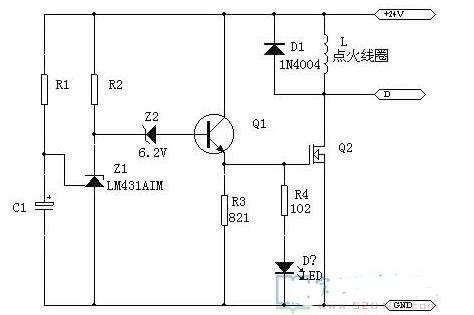

帶有延時的備份電池方案

本應用筆記介紹了主電源和備份電池通過二極管“或”邏輯電路與負載連接的方案。這一架構很容易理解,但當電池電壓

2010-01-26 16:30:46 507

507

VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準。VHDL是在1987年成為IEEE標準,Verilog HDL

2010-02-09 09:01:17 10864

10864 VHDL設計中信號與變量問題的研究

在VHDL程序設計中,可以充分利用信號或變量的系統默認值,來靈活實現設計目標。本文從應用的角度舉例說明了VHDL設計中信號與變量

2010-04-12 14:52:21 1484

1484

本文詳細討論了VHDL語句對PLD設計的影響和設計經驗,經典文章,值得仔細閱讀消化。, PLD Programming Using VHDL

2012-01-17 11:20:54 0

0 簡單介紹了VHDL的實際應用的注意事項,比較適合新手入門

2015-11-02 17:32:33 0

0 VHDL Simulation,好東西,喜歡的朋友可以下載來學習。

2016-02-17 14:38:39 8

8 本書以 VHDL 程序設計基礎與工程實踐為內容,全面介紹了 VHDL 程序設計的基礎知

識和基本技術,并結合工程實例講解電路設計的基本流程和 VHDL技術的應用。本書基本涵

2016-02-17 15:52:13 3

3 平時在寫關于時序的程序時,往往會見到while的延時函數,但是延時時間往往說法不一,這篇文章有助于對延時函數的理解。

2016-07-19 17:34:49 0

0 VHDL語言編程學習之VHDL硬件描述語言

2016-09-01 15:27:27 0

0 學好VHDL的重要性 對VHDL的 介紹

2016-09-02 16:54:40 17

17 硬件描述語言VHDL的學習文檔,詳細的介紹了VHDL

2016-09-02 17:00:53 12

12 VHDL語言要素,大學EDA課程必備資料,在實際的應用中,VHDL仿真器講INTEGER類型的數據作為有符號數處理,而綜合器將INTEGER作為無符號數處理. VHDL綜合器要求利用RANGE子句為

2016-11-21 15:40:34 0

0 VHDL實用教程,很好的一本教材,適合初學者

2016-11-11 15:51:00 23

23 Introduction to VHDL,英文資料,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 0

0 vhdl入門

2016-12-16 16:30:02 23

23 VHDL并行語句

2016-12-11 23:38:39 0

0 VHDL的入門知識

2017-05-09 08:40:11 5

5 本文檔的主要內容詳細介紹的是VHDL教程之使用VHDL進行電子設計所需的所有資料包括了:VHDL設計基礎知識,VHDL并行語句,VHDL程序實體,VHDL入門,VHDL語言要素,EDA設計流程及其工具,IA64 應用程序寄存器,LCD液晶顯示漢字字符集表,OCMJ 系列液晶顯示器控制命令集表等

2018-09-25 08:00:00 0

0 本文檔的主要內容詳細介紹的是VHDL教程之VHDL語言元素的詳細資料概述一內容包括了:1. VHDL語言的客體2 VHDL語言的數據類型3 VHDL數據類型轉換4 VHDL詞法規則與標識符

2018-11-05 08:00:00 0

0 本文檔的主要內容詳細介紹的是VHDL硬件描述語言入門教程資料免費下載包括了:1. VHDL語言基礎,2. VHDL基本結構,3. VHDL語句,4. 狀態機在VHDL中的實現,5. 常用電路VHDL程序,6. VHDL仿真,7. VHDL綜合

2019-04-08 08:00:00 54

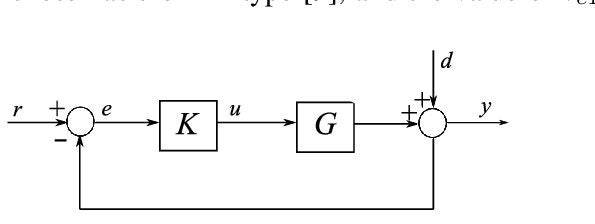

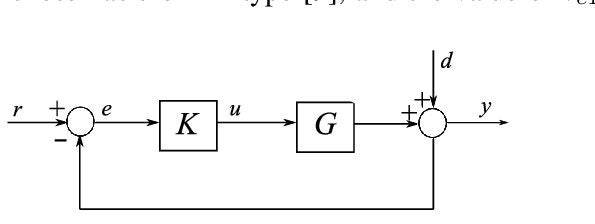

54 項目開始時我的總體項目功能符合我的預期,因此我對結果感到滿意。感謝您抽出寶貴的時間閱讀我在VHDL中開發PID控制器的嘗試。

2019-10-15 09:40:10 4090

4090

FreeRTOS中相對延時和絕對延時的區別

2020-03-12 10:32:09 9652

9652

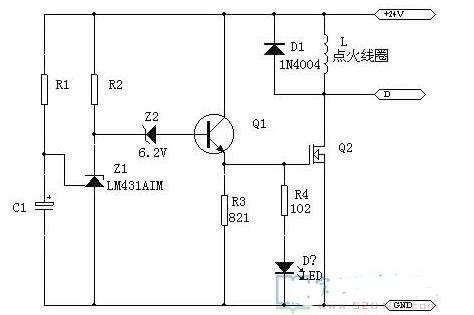

一般延時開關電路多用NE555來做,但是其最高工作電壓只能達到18伏,有客戶要求能工作在24伏的延時開關電路,用于汽車延時點火。我用LM431設計了一個延時開關電路,它可以工作在24伏,滿足了客戶的要求。

2020-03-15 16:57:00 10077

10077

在VHDL程序中,實體(ENTITY)和結構體(ARCHITECTURE)這兩個基本結構是必須的,他們可以構成最簡單的VHDL程序。通常,最簡單的VHDL程序結構中還包含另一個最重要的部分,即庫(LIBRARY)和程序包(PACKAGE)。

2020-04-23 15:43:38 5841

5841 什么是vhdl語言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語言)。VHSIC是Very High Speed

2020-04-23 15:58:49 13149

13149 本文概述了VHDL測試臺和其他相關主題。它是為一個數字設計工程師編寫的,他幾乎沒有VHDL或編程經驗,以便更好地理解VHDL的編寫和測試臺的使用。并對VHDL的發展前景進行了展望。

2021-01-20 15:17:14 19

19 本手冊討論VHDL和Synario可編程IColution。本手冊旨在補充可編程IC入門手冊中的材料本手冊中討論了以下主題HDL語言結構如何編寫可合成的VHDL如何控制VHDL設計的實現VHDL數據

2021-01-21 16:02:13 34

34 VHDL黃金參考指南是一個緊湊的快速參考指南VHDL語言,其語法,語義,綜合和應用程序的硬件設計。《VHDL黃金參考指南》并不打算取代IEEE標準VHDL語言參考手冊。與該文檔不同的是,《黃金

2021-01-21 16:30:54 36

36 本文檔的主要內容詳細介紹的是VHDL語言的詳細講解學習課件免費下載包括了:

ⅥHLD概述

VHLD的一些基本概念

VHDL的數據對象,數據類型及類型轉換,運算符等

VHDL的順序描述語句

VHDL

2021-01-22 17:52:14 36

36 在實現單片機功能的時候,經常會用到延時函數,那么延時函數的原理也是非常有必要了解的。一般我們寫延時函數的時候,默認的晶振頻率fosc=12MHZ,而機器周期T=12/fosc=1us。這里我們來寫一

2021-11-11 09:36:02 94

94 文章目錄中斷延時通過在中斷中的計數值的不斷遞減來達到精確延時,而非中斷則通過在循環里不停查詢寄存器數值來達到精確延時。前者因為中斷的存在,不利于在其他中斷中調用延時函數。在很多延時教程中,都喜歡推薦非中斷式的延時。不過對于非特殊情況,兩者的效果是一樣的。反而非中斷延時需要操作寄存器,反而更難理解。

2021-11-24 19:36:02 0

0 這是一種,直接利用for循環需要時間來實現循環缺點是不能自定義自己想要的延時時間;void Delay500ms() //這是我在stc-isp下載的延時函數 ,在我主頁會有講解{unsigned

2021-11-24 19:51:06 8

8 或者累減的方法,到一定條件后就退出。好處:好寫,用for循環或者while循環,不用去理解各種有關底層硬件的寄存器。壞處:延時不精準,誤差大,讓CPU持續空跑,大大浪費CPU資源。void delay(uint16 i){ #if 0 while(i--) {} #endif for(

2022-01-14 12:49:15 5

5 CPU頻率一般為晶振頻率,當接入外部晶振時,CPU頻率為外頻乘以內頻。延時函數通過運行一次計算CPU所用的時間來達到延時的延時的目的,延時時間為:計算次數/cpu頻率(MHZ)=延時時間(us)

2022-01-18 10:26:20 3

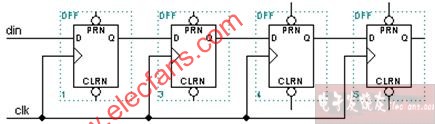

3 前段時間我臨時對一個脈沖信號延時8192個CLK就使用了這種寫法,當時有意識到可能會消耗較多的資源,但沒想到會這么多。 不同方式實現延時的資源消耗對比 還是對一個脈沖信號延時8192個CLK,為了對比不同方式的資源消耗,我新建了一個工程 平臺:

2022-06-30 17:39:52 2691

2691 嵌入式軟件代碼中延時是很常見的,只是延時種類有很多,看你用什么延時。

2022-08-12 08:48:01 2403

2403 VHDL 的 英 文 全 名 是 Very-High-Speed Integrated Circuit Hardware

DescriptionLanguage,誕生于 1982 年。

1987

2023-02-10 17:42:46 0

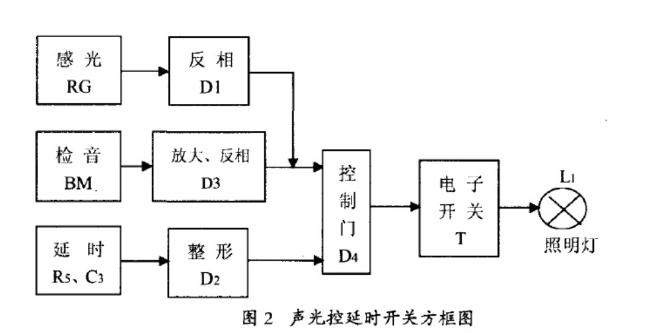

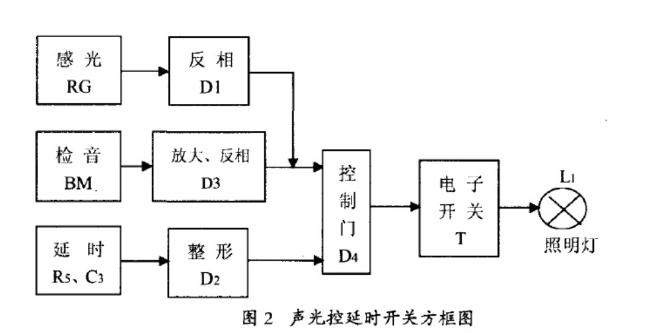

0 聲光控制延時開關主要由聲控開關、光控開關、延時電路幾部分組成。聲控是通過柱極體話筒采集聲音,并產生脈沖信號。光控電路則是由光敏電阻控制,光敏電阻在有光和無光狀態下電阻阻值差距很大,能產生高低

2023-07-05 10:34:58 4329

4329

延時開關的接線技巧與注意事項是確保延時開關正確安裝和穩定運行的關鍵。 一、延時開關接線技巧 1. 理解延時開關的基本結構 延時開關通常包含多個引腳,其中最重要的是COM(公共端)、NO(常開

2024-08-19 15:54:22 4287

4287 理解。 VHDL :VHDL 的語法更接近于 Ada 語言,它是一種更正式的語言,具有豐富的數據類型和結構。VHDL 支持數據流、行為和結構化三種描述方式。 2. 可讀性和可維護性 Verilog

2024-12-17 09:44:44 2874

2874 在群里交流提問的時候,大家總是驚訝并疑惑:為什么我要選擇 VHDL入門?因為好像 99% 搞 FPGA 開發的人都在用 Verilog。 我的選擇,是通過網上搜索的討論而做出的,為了留存,我這里水一

2025-06-25 11:18:00 1012

1012

電子發燒友App

電子發燒友App

評論