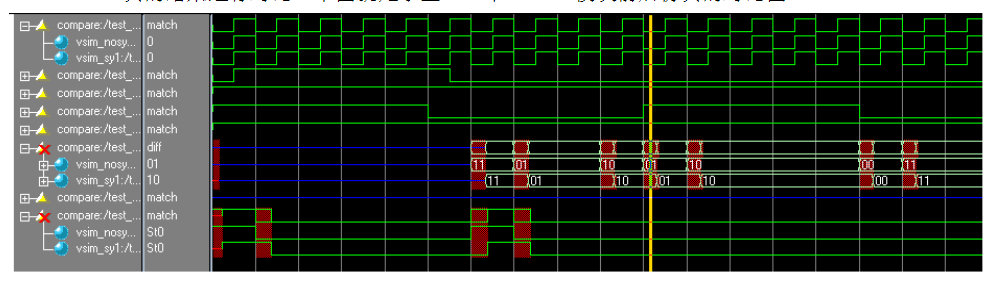

介紹如何編譯HDL必須的Xilinx庫(kù)和結(jié)構(gòu)仿真。創(chuàng)建將被編譯庫(kù)的目錄在編譯庫(kù)之前,最好先建立一個(gè)目錄(事實(shí)上必須建立一個(gè)目錄),步驟如下。(假設(shè)Modelsim的安裝目錄是“$Modeltech_6.0”,ISE的安裝目錄是“$Xilinx”)◆ 在“$Modeltech_6.0/”目錄下建立一個(gè)名為XilinxLib的文件夾;◆ 啟動(dòng)Modelsim后,從“File”菜單項(xiàng)中點(diǎn)擊“Change Directory”并指定到剛剛建立的那個(gè)文件夾“XilinxLib”;◆ 接下來(lái)要做的事情是將Xilinx庫(kù)編譯到“XilinxLib”文件夾中。有三個(gè)庫(kù)需要被編譯。它們分別是“simprims”,“unisims”和“XilinxCoreLib”;(所有這些庫(kù)文件都在“$Xilinx/verilog/src”目錄下)◆ 點(diǎn)擊Modelsim中的“Workspace”窗口,建立一個(gè)名為Xilinx_CoreLib的新庫(kù);(這個(gè)操作創(chuàng)建一個(gè)名為“Xilinx_CoreLib”的文件夾,你可以在“Workspace”窗口中看到它)◆ 現(xiàn)在開始編譯!在“Compile”菜單中點(diǎn)擊“Compile”,選擇“$Xinlinx/verilog/scr/XilinxCoreLib”目錄中所有的文件,在彈出的對(duì)話框中選中剛剛建立的“Xilinx_CoreLib”文件夾,再點(diǎn)擊“Compile”按鈕就可以了編譯了;◆ 用同樣的方式編譯其他兩個(gè)本地庫(kù)(“simprims”和“unisims”);第二章 調(diào)用Xilinx CORE-Generator當(dāng)需要在設(shè)計(jì)中生成參數(shù)化和免費(fèi)的IP內(nèi)核(黑箱子)時(shí),無(wú)論是通過(guò)原理圖方式還是HDL方式,CORE-Generator都是一個(gè)非常有用的程序。?利用CORE-Generator創(chuàng)建一個(gè)IP核?利用Xilinx提供的CORE-Generator來(lái)生成IP核是非常簡(jiǎn)單的。內(nèi)核是全參數(shù)化的,這就意味著你只需要在空白處填入幾個(gè)數(shù)字和參數(shù),然后程序就會(huì)自動(dòng)產(chǎn)生一個(gè)你所需要的?內(nèi)核。(有些內(nèi)核是全免費(fèi)的,有些則沒有這么慷慨)?利用CORE-Generator來(lái)生成IP核的步驟如下:?◆ 在“程序”中找到“Xilinx”項(xiàng),然后在“Accessories”中啟動(dòng)單獨(dú)存在的“CORE-Generator”;?◆ 在“Part”標(biāo)簽欄中選擇恰當(dāng)?shù)?a target="_blank">FPGA模型;?◆ 從“Generation”標(biāo)簽欄中選擇正確的設(shè)計(jì)流;(完成后按“OK”按鈕)?◆ 定制你的參數(shù)化內(nèi)核;?◆ 在內(nèi)核生成的同時(shí),會(huì)彈出一個(gè)“Readme File”的信息框來(lái)通知一些重要的信息;?◆ “*.v”文件是用來(lái)作仿真和綜合用的,而“*.veo”文件是用來(lái)作綜合實(shí)例用的。(調(diào)用意味著把相應(yīng)的文件加入Synplify.Pro工程中,而實(shí)例指的是可以拷貝這個(gè)文件中的某些線到HDL設(shè)計(jì)的頂層模塊中去。退出!)?第三章 使用Synplify.Pro綜合HDL和內(nèi)核綜合是將設(shè)計(jì)好的HDL代碼,圖形代碼和原理圖轉(zhuǎn)變成邏輯單元的技術(shù)。同與硬件執(zhí)行和物理布線非常接近的物理綜合相比,邏輯綜合是更高層次的綜合技術(shù)。?利用Synplify.Pro進(jìn)行邏輯綜合?Synplify.Pro對(duì)于大容量低價(jià)格的Xilinx Spartan系列FPGA而言,有著非常好的綜合能力。?具體步驟如下:?◆ 首先創(chuàng)建一個(gè)工程;?◆ 往工程中加入HDL文件(我的演示文件有三個(gè)文件,CORE-Generator生成的“async_fifo.v”和“dcm4clk”和一個(gè)Verilog頂層文件“top.v”)。在Synplify.Pro環(huán)境中設(shè)置“Implementation Option”;(如果讀者非常熟練的話,可以省略這步)?◆ 往CORE-Generator生成的兩個(gè)Verilog文件中插入Synplify.Pro能夠識(shí)別的指示這些指示告訴綜合器如何處理這兩個(gè)特殊的文件;?◆ 插入“/*synthesis syn_black_box*/”指示通知Synplify.Pro把模塊當(dāng)作黑箱子來(lái)處理,同時(shí)指示“/*synthesis syn_isclock=1*/”表示這個(gè)作為時(shí)鐘輸入端的端口不能被綜合器識(shí)別,因?yàn)樗硕丝诿鉀]有下層結(jié)構(gòu);?◆ 將工程保存在合適的地方,然后綜合這個(gè)工程;?◆ 在綜合完成后,選擇“Technology View”按鈕來(lái)觀察層次結(jié)構(gòu);(你可以發(fā)現(xiàn)內(nèi)核?◆ 不管你相信與否!Synplify.Pro已經(jīng)生成了你所希望的東西。(擁有專用Clock-Input-Buffer,IBUG連接的DCM結(jié)構(gòu),并且有一個(gè)從Global-Clock-Buffer,BUFG的反饋結(jié)構(gòu)“CLKFB”)?第四章 綜合后的項(xiàng)目執(zhí)行?執(zhí)行是將生成的位文件下載到FPGA的最后一個(gè)步驟。?同時(shí)創(chuàng)建不同的時(shí)序模型(post-translate模型,post-map模型和post-PAR模型)和時(shí)序報(bào)告。?ISE,唯一可以用來(lái)執(zhí)行的工具?ISE控制著設(shè)計(jì)流的各個(gè)方面。通過(guò)Project Navigator界面,可以進(jìn)入所有不同的設(shè)計(jì)實(shí)體和實(shí)際執(zhí)行工具。同時(shí)也可以訪問于工程有關(guān)的文件和文檔。Project Navigator包含一個(gè)平坦的目錄結(jié)構(gòu);?在演示項(xiàng)目中,ISE的一些貧乏的功能不得不讓道給其他的第三方軟件,例如ModelSim.Pro和Synplify.Pro,因此ISE一般僅僅被用作執(zhí)行工具。?◆ 啟動(dòng)ISE,用“EDIF”作為文件輸入;(“EDIF”文件由Synplify.Pro軟件生成,作為終端設(shè)計(jì)文件,可以被大多數(shù)的FPGA開發(fā)環(huán)境識(shí)別,例如ISE,Quartus,ispLevel。)?◆ 在建立了ISE工程后,可以加入其他兩個(gè)文件,一個(gè)是與內(nèi)核相關(guān)的“*.xco”文件,另一個(gè)是與DCM結(jié)構(gòu)有關(guān)的“*.xaw”;?◆ 現(xiàn)在可以生成需要仿真的所有的模塊;(點(diǎn)擊下劃紅線的選項(xiàng))?◆ 如果想仿真post-PAR模塊,最好首先定義引腳,特別是專用的外部時(shí)鐘引腳;?◆ 啟動(dòng)“map”程序中的“Floorplaner”選項(xiàng)來(lái)定義引腳;?◆ “DCMs”和“IBUFGs”應(yīng)該被放在正確的位置。?仿真是用來(lái)驗(yàn)證設(shè)計(jì)的時(shí)序和功能是否正確的調(diào)試方法之一。?在驗(yàn)證調(diào)試電路和觀察波形的過(guò)程中,應(yīng)該進(jìn)行四個(gè)不同類型的仿真。?不同的仿真類型針對(duì)的不同的平臺(tái)。功能仿真用來(lái)驗(yàn)證設(shè)計(jì)的功能是否正確;?post-translate仿真用來(lái)驗(yàn)證設(shè)計(jì)的基于原語(yǔ)延時(shí);post-map仿真用來(lái)仿真基于原語(yǔ)延時(shí)和網(wǎng)絡(luò)延時(shí);最后,post-PAR仿真在post-map仿真的基礎(chǔ)上加入了輸入輸出和布線延時(shí)。?我不會(huì)給出演示設(shè)計(jì)的全部詳細(xì)的仿真過(guò)程,但是給出了重點(diǎn)和重要的步驟。只給出了post-PAR仿真過(guò)程,列出了對(duì)于所有其他三種仿真需要的不同文件。(實(shí)際上,不同的文件是不同的參考時(shí)序模型:

FPGA設(shè)計(jì)全流程:ModelsimSynplify.ProISE

- FPGA(632043)

- FPGA設(shè)計(jì)(28066)

- Xilinx(130366)

相關(guān)推薦

熱點(diǎn)推薦

FPGA開發(fā)流程簡(jiǎn)介

FPGA開發(fā)基本流程包括:設(shè)計(jì)輸入、設(shè)計(jì)仿真、設(shè)計(jì)綜合、布局布線,它們的連接關(guān)系如圖1 所示。

2010-06-10 08:24:15 1836

1836

1836

1836玩轉(zhuǎn)Altera FPGA的關(guān)鍵與FPGA開發(fā)流程分享

如圖1.9所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行FPG

2017-10-24 10:43:09 8025

8025

8025

8025

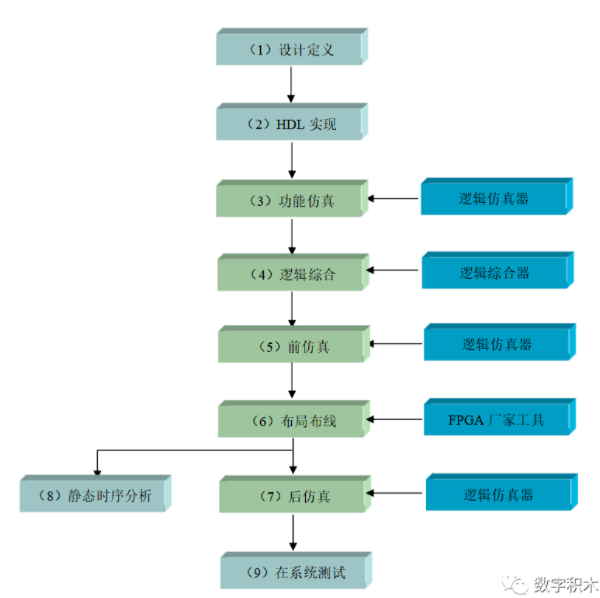

FPGA的開發(fā)流程及仿真技術(shù)解析

FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,FPGA的開發(fā)流程總體按照?qǐng)D1進(jìn)行,有些步驟可能由于其在當(dāng)前項(xiàng)目中的條件的寬度的允許,可以免去。

2023-01-06 11:19:28 2745

2745

2745

2745如何利用Tcl在Vivado中實(shí)現(xiàn)定制化的FPGA設(shè)計(jì)流程?

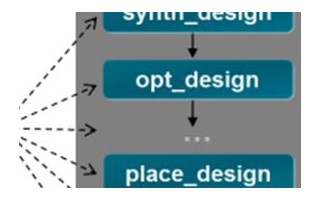

FPGA 的設(shè)計(jì)流程簡(jiǎn)單來(lái)講,就是從源代碼到比特流文件的實(shí)現(xiàn)過(guò)程。大體上跟 IC 設(shè)計(jì)流程類似,可以分為前端設(shè)計(jì)和后端設(shè)計(jì)。

2023-04-23 09:08:49 3022

3022

3022

3022

EDA全流程的重要意義,以及國(guó)內(nèi)EDA全流程進(jìn)展

的方式。如果一款工具能夠覆蓋特定芯片在上述流程中的設(shè)計(jì)任務(wù),那么我們就將其稱之為全流程EDA工具,或者是全流程EDA平臺(tái)。 在國(guó)產(chǎn)EDA發(fā)展初期,還有人質(zhì)疑,在EDA三大家提供全流程工具的情況下,國(guó)產(chǎn)EDA是否還有必要繼續(xù)重走這條路。不過(guò),隨著美國(guó)對(duì)中國(guó)科技制裁逐漸加大

2023-12-14 00:08:00 3439

3439

3439

3439FPGA入門:基本開發(fā)流程概述

FPGA入門:基本開發(fā)流程概述 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問網(wǎng)盤:http://pan.baidu.com/s

2015-02-09 20:14:21

FPGA基本開發(fā)流程概述

FPGA入門:基本開發(fā)流程概述 在第一章中,已經(jīng)給出了FPGA/CPLD的基本開發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA/CPLD器件開發(fā)流程,從項(xiàng)目

2019-01-28 02:29:05

FPGA基本開發(fā)設(shè)計(jì)流程

FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過(guò)程。FPGA的開發(fā)流程一般如圖1-10所示,包括電路功能設(shè)計(jì)、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真

2021-07-23 09:12:07

FPGA實(shí)戰(zhàn)演練邏輯篇8:FPGA開發(fā)流程

FPGA開發(fā)流程(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-31 09:27:38

FPGA開發(fā)流程

哪位大神可以發(fā)一個(gè)FPGA開發(fā)流程的文檔,用實(shí)例演示的,包括行為,功能和時(shí)序分析的,萬(wàn)分感謝!

2014-05-14 10:34:40

FPGA開發(fā)流程

如圖1.6所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行FPGA功能的需求分析,然后進(jìn)行模塊的劃分,比較復(fù)雜和龐大的設(shè)計(jì),則會(huì)通過(guò)模塊劃分把工作交給一個(gè)

2019-01-28 04:24:37

FPGA的設(shè)計(jì)流程是怎樣的

第二章 FPGA 開發(fā)流程FPGA 的設(shè)計(jì)流程就是利用 EDA 開發(fā)軟件和編程工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過(guò)程。原理圖和HDL(Hardware description language,硬件

2022-02-23 06:23:33

FPGA設(shè)計(jì)全流程

FPGA設(shè)計(jì)全流程第一章Modelsim編譯Xilinx庫(kù) 第二章調(diào)用Xilinx CORE-Generator第三章使用Synplify.Pro綜合HDL 和內(nèi)核 第四章綜合后的項(xiàng)目執(zhí)行 第五章不同類型結(jié)構(gòu)的仿真

2012-08-11 16:15:54

IC設(shè)計(jì)流程

不太對(duì),查了一下資料,那里是不太對(duì)啊,簡(jiǎn)直是一點(diǎn)都不對(duì),暴寒啊,也許是自己真是好久沒做IC方面的東西了。一般的IC設(shè)計(jì)流程可以分為兩大類:全定制和半定制,這里我換一種方式來(lái)說(shuō)明。 1.1 從RTL到

2012-01-11 13:49:27

IC設(shè)計(jì)流程介紹

FPGA廠商Altera和Xilinx自帶的QuartusⅡ和ISE開發(fā)平臺(tái)完全可以應(yīng)付與之有關(guān)的開發(fā)。 整個(gè)完整的流程可以分為前端和后端兩部分,前端的流程圖如下: 前端的主要任務(wù)是將HDL語(yǔ)言描述的電路

2018-08-16 09:14:32

【下載】《FPGA設(shè)計(jì)指南:器件、工具和流程》

`編輯推薦 《FPGA設(shè)計(jì)指南:器件、工具和流程》適用于使用FPGA進(jìn)行設(shè)計(jì)的工程師、進(jìn)行嵌入式應(yīng)用任務(wù)開發(fā)的軟件工程師以及高等院校電氣工程專業(yè)的師生。內(nèi)容簡(jiǎn)介 本書用簡(jiǎn)潔的語(yǔ)言向讀者展示了

2017-09-01 18:05:30

使用QUARTUS II做FPGA開發(fā)全流程,傻瓜式詳細(xì)教程

本帖最后由 eehome 于 2013-1-5 09:45 編輯

使用QUARTUS_II做FPGA開發(fā)全流程,傻瓜式詳細(xì)教程

2012-03-08 16:26:11

例說(shuō)FPGA連載8:FPGA開發(fā)流程

例說(shuō)FPGA連載8:FPGA開發(fā)流程特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖1.9所示。這個(gè)流程圖是一個(gè)相對(duì)

2016-07-13 17:25:34

關(guān)于“小墨同學(xué)”推出的零基礎(chǔ)FPGA“基于FIFO的串口發(fā)送機(jī)設(shè)計(jì)全流程”相關(guān)部分討論

鏈接為“小墨同學(xué)”推出的零基礎(chǔ)FPGA“基于FIFO的串口發(fā)送機(jī)設(shè)計(jì)全流程”,https://bbs.elecfans.com/jishu_475408_1_1.html其中,有幾個(gè)部分不是很明白小墨同學(xué)的設(shè)計(jì)思路,希望大家拍磚(見圖片紅色框體部分)

2017-07-27 19:34:54

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載8:FPGA開發(fā)流程

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載8:FPGA開發(fā)流程特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 如圖1.9所示。這個(gè)

2017-10-12 21:02:44

華為FPGA設(shè)計(jì)流程指南

前言 本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成風(fēng)格良好和完整的文檔

2017-12-08 14:47:15

華為FPGA設(shè)計(jì)流程指南

華為FPGA設(shè)計(jì)流程指南本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成

2017-12-18 10:45:03

基于FPGA的混合信號(hào)驗(yàn)證流程

。 智能型流程 不僅是ASIC/FPGA設(shè)計(jì)者對(duì)系統(tǒng)/模擬設(shè)計(jì)的實(shí)際經(jīng)驗(yàn)很少,大部分的系統(tǒng)設(shè)計(jì)者也同樣沒有數(shù)字邏輯的設(shè)計(jì)經(jīng)驗(yàn)。因此,日益純熟的設(shè)計(jì)內(nèi)容需要智能型的工具流程。這意味著工具有智能去組態(tài)和啟動(dòng)

2011-10-16 22:55:10

請(qǐng)問單片機(jī)設(shè)計(jì)全流程是什么?

請(qǐng)***片機(jī)設(shè)計(jì)全流程是什么?從一窮二白到實(shí)驗(yàn)成品,要經(jīng)歷些什么步驟?謝謝!

2014-04-17 21:38:03

請(qǐng)問目前FPGA設(shè)計(jì)流程還需要考慮哪些事項(xiàng)?

目前xilinx 在FPGA設(shè)計(jì)上總結(jié)出了UFDM這個(gè)名詞,也有ug949這篇經(jīng)典的文檔,將FPGA設(shè)計(jì)的流程、方法、注意事項(xiàng)都有詳細(xì)介紹,總結(jié)了很多成功的經(jīng)驗(yàn),提升到設(shè)計(jì)方法學(xué)的高度。可能很多

2019-10-11 07:04:21

通過(guò)ISE開發(fā)看懂FPGA設(shè)計(jì)全流程

1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程利用XilinxISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實(shí)現(xiàn)、布線后仿真與驗(yàn)證和下班調(diào)試等步驟。如下圖所示。1)電路設(shè)計(jì)

2021-06-24 08:00:01

華為FPGA設(shè)計(jì)流程指南

本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:

2010-11-01 17:30:26 182

182

182

182FPGA設(shè)計(jì)全流程工具FPGA Advantage培訓(xùn)班

Mentor Graphics的FPGA Advantage是享譽(yù)業(yè)界,具有FPGA設(shè)計(jì)黃金組合的全流程設(shè)計(jì)工具。本次課程將使用戶體驗(yàn)FPGA Advantage如何最大化地加速設(shè)計(jì)的實(shí)現(xiàn)以及復(fù)用。同時(shí)掌握如何利用FPGA Advantage快速實(shí)現(xiàn)設(shè)計(jì)從創(chuàng)建、理解、仿真驗(yàn)證、綜合以及布局布線的全過(guò)

2011-03-15 13:39:56 98

98

98

98Altera演示業(yè)界首款FPGA的浮點(diǎn)DSP設(shè)計(jì)流程

Altera公司日前演示了使用FPGA的浮點(diǎn)DSP新設(shè)計(jì)流程,這是業(yè)界第一款基于模型的浮點(diǎn)設(shè)計(jì)工具,支持在FPGA中實(shí)現(xiàn)復(fù)數(shù)浮點(diǎn)DSP算法。

2011-09-15 09:07:10 830

830

830

830Alter FPGA的設(shè)計(jì)流程以及DSP設(shè)計(jì)

Alter FPGA的設(shè)計(jì)流程以及DSP設(shè)計(jì).

2012-03-16 15:52:07 127

127

127

127[CPLD-FPGA]《深入淺出玩轉(zhuǎn)FPGA視頻學(xué)習(xí)課程》35講全[wmv]

[CPLD-FPGA]《深入淺出玩轉(zhuǎn)FPGA視頻學(xué)習(xí)課程》35講全[wmv] 附件比較大所以整理了視頻迅雷種子。

2013-09-04 14:51:19 519

519

519

519FPGA設(shè)計(jì)指南:器件、工具和流程_部分2

本書用簡(jiǎn)潔的語(yǔ)言向讀者展示了什么是FPGA、FPGA如何工作、如何對(duì)FPGA編程以

及FPGA設(shè)計(jì)中遇到的各種概念、器件和工具,如傳統(tǒng)的基于HDL/RTL的仿真和邏輯綜合、最新的純C/C++設(shè)計(jì)捕獲和綜合技術(shù)以及基于DSP的設(shè)計(jì)流程。另外,本書還涉及大量豐富的、工程師所需的技術(shù)細(xì)節(jié)。

2016-04-26 11:42:13 3

3

3

3FPGA設(shè)計(jì)指南:器件、工具和流程_部分1

本書用簡(jiǎn)潔的語(yǔ)言向讀者展示了什么是FPGA、FPGA如何工作、如何對(duì)FPGA編程以

及FPGA設(shè)計(jì)中遇到的各種概念、器件和工具,如傳統(tǒng)的基于HDL/RTL的仿真和邏輯綜合、最新的純C/C++設(shè)計(jì)捕獲和綜合技術(shù)以及基于DSP的設(shè)計(jì)流程。另外,本書還涉及大量豐富的、工程師所需的技術(shù)細(xì)節(jié)。

2016-04-26 11:42:13 4

4

4

4基于FPGA的全幀CCD驅(qū)動(dòng)設(shè)計(jì)

基于FPGA的全幀CCD驅(qū)動(dòng)設(shè)計(jì),有需要的下來(lái)看看

2016-08-29 23:19:11 19

19

19

19Xilinx FPGA 嵌入式系統(tǒng)程序引導(dǎo)和啟動(dòng)的流程

這篇blog想弄清楚FPGA上電配置后程序引導(dǎo)和啟動(dòng)的整個(gè)流程是怎么樣的,不是談?wù)撊绾尉帉慴ootloader。

2017-02-11 05:55:06 2768

2768

2768

2768Virtex5 FPGA在ISE + Planahead上部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)

部分可重構(gòu)技術(shù)是Xilinx FPGA的一項(xiàng)重要開發(fā)流程。本文結(jié)合Virtex5 FPGA,詳細(xì)講解在ISE + Planahead上完成部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)。

2018-07-04 02:17:00 4583

4583

4583

4583

全定制和半定制簡(jiǎn)易IC設(shè)計(jì)流程介紹

一般的IC設(shè)計(jì)流程可以分為兩大類:全定制和半定制,這里我換一種方式來(lái)說(shuō)明。 1.1 從RTL到GDSⅡ的設(shè)計(jì)流程: 這個(gè)可以理解成半定制的設(shè)計(jì)流程,一般用來(lái)設(shè)計(jì)數(shù)字電路。 整個(gè)流程如下(左側(cè)為流程

2017-10-20 11:38:20 25

25

25

25FPGA開發(fā)流程詳細(xì)解析

1. FPGA 開發(fā)流程: 電路設(shè)計(jì)與設(shè)計(jì)輸入 ;仿真驗(yàn)證:利用Xilinx集成的仿真工具足矣 ;邏輯綜合:利用XST(Xilinx Synthesis Tool)工具 ;布局布線:利用Xilinx

2018-01-12 03:59:48 10715

10715

10715

10715從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì)

不斷 從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì) 1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程 利用XilinxISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合

2018-02-20 20:32:00 16847

16847

16847

16847

針對(duì)全定制模擬和混合信號(hào)設(shè)計(jì)的全流程工具平臺(tái)

Mentor Graphics的Tanner EDA是針對(duì)全定制lC、模擬/混合信號(hào)(AMS)和MEMS設(shè)計(jì)的一套產(chǎn)品。對(duì)物聯(lián)網(wǎng)(IoT)需求的突然上升使全流程混合信號(hào)設(shè)計(jì)環(huán)境面臨獨(dú)特的要求:經(jīng)濟(jì)

2018-03-05 10:43:07 0

0

0

0FPGA設(shè)計(jì)流程“又臭又長(zhǎng)”?從eda工具理解超級(jí)簡(jiǎn)單!

對(duì)于初學(xué)者而言,FPGA的設(shè)計(jì)流程是否顯的“又臭又長(zhǎng)”呢??嗬嗬,如果真的有這樣的感覺,沒有關(guān)系,下面我就通過(guò)對(duì)軟體的使用來(lái)了解FPGA的設(shè)計(jì)流程。

2018-06-02 07:17:00 1553

1553

1553

1553

ISE設(shè)計(jì)流程簡(jiǎn)介--華清遠(yuǎn)見fpga培訓(xùn)視頻教程

本視頻教程主要主要介紹Xilinx公司開發(fā)設(shè)計(jì)流程中的各個(gè)功能模塊,包括ISE中的設(shè)計(jì)輸入,綜合,設(shè)計(jì)實(shí)現(xiàn)及驗(yàn)證等內(nèi)容,此專題將為廣大FPGA工程師深入理解EDA工具實(shí)現(xiàn)原理與FPGA開發(fā)完整流程提供幫助,從而為未來(lái)更復(fù)雜的設(shè)計(jì)打下基礎(chǔ)。

2018-06-06 13:46:00 4820

4820

4820

4820一文解讀FPGA設(shè)計(jì)者的5項(xiàng)基本功及設(shè)計(jì)流程

本文首先介紹了FPGA發(fā)展由來(lái),其次介紹了FPGA的硬件設(shè)計(jì)技巧及FPGA設(shè)計(jì)者的5項(xiàng)基本功,最后介紹了FPGA設(shè)計(jì)流程及工程師FPGA設(shè)計(jì)心得體會(huì)。

2018-05-31 09:35:06 12145

12145

12145

12145ISE設(shè)計(jì)流程簡(jiǎn)介--華清遠(yuǎn)見fpga培訓(xùn)視頻教程

本視頻教程主要主要介紹Xilinx公司開發(fā)設(shè)計(jì)流程中的各個(gè)功能模塊,包括ISE中的設(shè)計(jì)輸入,綜合,設(shè)計(jì)實(shí)現(xiàn)及驗(yàn)證等內(nèi)容,此專題將為廣大FPGA工程師深入理解EDA工具實(shí)現(xiàn)原理與FPGA開發(fā)完整流程提供幫助,從而為未來(lái)更復(fù)雜的設(shè)計(jì)打下基礎(chǔ)。

2018-06-08 02:35:00 5830

5830

5830

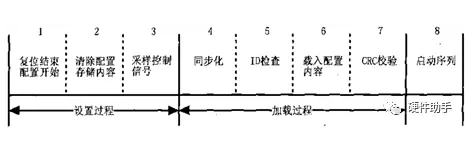

5830關(guān)于Xilinx FPGA的配置流程淺析

盡管FPGA的配置模式各不相同,但整個(gè)配置過(guò)程中FPGA的工作流程是一致的,分為三個(gè)部分:設(shè)置、加載、啟動(dòng)。

2018-08-01 15:32:54 5330

5330

5330

5330

PCB外層制作流程之全板電鍍(PPTH)

全板電鍍銅缸設(shè)計(jì)原理:全板電鍍流程:反應(yīng)原理: 鍍銅在PCB制造過(guò)程中,主要用于加厚孔內(nèi)化學(xué)銅層和線路銅層。

2018-08-04 10:37:08 13711

13711

13711

13711FPGA的設(shè)計(jì)流程是怎么樣的?FPGA設(shè)計(jì)流程指南詳細(xì)資料免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的設(shè)計(jì)流程是怎么樣的?FPGA設(shè)計(jì)流程指南詳細(xì)資料免費(fèi)下載內(nèi)容包括了:1.基于HDL 的FPGA 設(shè)計(jì)流程概述2.Verilog HDL 設(shè)計(jì)3. 邏輯仿真4. 邏輯綜合

2018-10-17 17:50:41 32

32

32

32FPGA的開發(fā)流程和物理含義和實(shí)現(xiàn)目標(biāo)詳解

FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,FPGA的開發(fā)流程總體按照?qǐng)D1進(jìn)行,有些步驟可能由于其在當(dāng)前項(xiàng)目中的條件的寬度的允許,可以免去,比如靜態(tài)仿真過(guò)程,這樣來(lái)達(dá)到項(xiàng)目

2018-11-18 09:55:45 1705

1705

1705

1705

FPGA視頻教程之FPGA開發(fā)流程的詳細(xì)資料概述

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之FPGA開發(fā)流程的詳細(xì)資料概述免費(fèi)下載。

2019-03-01 11:35:37 11

11

11

11FPGA視頻教程之NIOS II開發(fā)流程的詳細(xì)資料說(shuō)明

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之NIOS II開發(fā)流程的詳細(xì)資料說(shuō)明主要目的是:1.完整的嵌入式開發(fā)流程,2.FPGA硬件設(shè)計(jì)流程,3.Nios II處理器軟件開發(fā)流程,4.Flash編程器流程

2019-03-22 13:59:55 11

11

11

11FPGA教程之ISE設(shè)計(jì)流程簡(jiǎn)介的詳細(xì)資料說(shuō)明

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之ISE設(shè)計(jì)流程簡(jiǎn)介的詳細(xì)資料說(shuō)明。

2019-04-04 17:18:45 15

15

15

15PADS VX版如何提高全流程的設(shè)計(jì)生產(chǎn)率

參加本研討會(huì)可了解 PADS VX 版如何提高全流程的設(shè)計(jì)生產(chǎn)率。

2019-05-20 06:10:00 3569

3569

3569

3569

建立完善的硬件設(shè)計(jì)全流程解決方案

隨著汽車工業(yè)的發(fā)展,汽車電子的設(shè)計(jì)要求越來(lái)越高,不完善的硬件設(shè)計(jì)流程方法將會(huì)導(dǎo)致產(chǎn)品在激烈的市場(chǎng)競(jìng)爭(zhēng)中處于劣勢(shì),通過(guò)建立完善的硬件設(shè)計(jì)全流程解決方案,設(shè)計(jì)團(tuán)隊(duì)可以最優(yōu)化設(shè)計(jì)流程,保證設(shè)計(jì)質(zhì)量,縮短設(shè)計(jì)周期。提高產(chǎn)品競(jìng)爭(zhēng)力,幫助企業(yè)獲得更高的效益。

2019-05-16 06:12:00 4554

4554

4554

4554

Xilin ISE設(shè)計(jì)流程FPGA系統(tǒng)設(shè)計(jì)入門免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是Xilin ISE設(shè)計(jì)流程FPGA系統(tǒng)設(shè)計(jì)入門免費(fèi)下載。

2019-10-29 08:00:00 9

9

9

9關(guān)于FPGA它的開發(fā)流程是怎樣的

FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過(guò)程。FPGA的開發(fā)流程一般包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-06 15:17:28 2841

2841

2841

2841FPGA的開發(fā)流程以及它的適用場(chǎng)景

FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過(guò)程。FPGA的開發(fā)流程包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-20 15:06:28 2284

2284

2284

2284FPGA的設(shè)計(jì)流程詳細(xì)說(shuō)明

本部門所承擔(dān)的 FPGA 設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和 ASIC 的原型驗(yàn)證。編寫本流程的目的是:

2020-04-28 08:00:00 3

3

3

3帶你深入了解FPGA開發(fā)流程

FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,FPGA的開發(fā)流程總體按照下圖進(jìn)行,有些步驟可能由于其在當(dāng)前項(xiàng)目中的條件的寬度的允許,可以免去,比如靜態(tài)仿真過(guò)程,這樣來(lái)達(dá)到項(xiàng)目

2020-10-25 10:05:37 4709

4709

4709

4709

FPGA設(shè)計(jì)流程及原理

01 FPGA的設(shè)計(jì)流程 FPGA是可編程芯片,因此FPGA的設(shè)計(jì)內(nèi)容包括硬件設(shè)計(jì)和軟件設(shè)計(jì)兩部分。硬件包括FPGA芯片電路、 存儲(chǔ)器、輸入輸出接口電路以及其他設(shè)備,軟件即是相應(yīng)的HDL程序以及

2020-11-12 18:22:28 7389

7389

7389

7389芯片制造全流程及詳解

我們身邊大大小小的電子設(shè)備中都會(huì)有芯片,芯片讓生活步入了更加智慧的模式。那么芯片那么神奇的東西是怎么制造的呢?下面小編就帶大家看看芯片制造全流程及詳解。 芯片制造全流程: 沉積 光刻膠涂覆 曝光

2021-12-10 18:15:36 17965

17965

17965

17965FPGA基礎(chǔ)知識(shí)----第二章 FPGA 開發(fā)流程

第二章 FPGA 開發(fā)流程FPGA 的設(shè)計(jì)流程就是利用 EDA 開發(fā)軟件和編程工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過(guò)程。原理圖和HDL(Hardware description language,硬件

2021-12-29 19:40:15 9

9

9

9FPGA設(shè)計(jì)流程和技術(shù)規(guī)范

本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:

2022-03-15 11:19:26 4832

4832

4832

4832

概倫電子正式發(fā)布EDA全流程的平臺(tái)產(chǎn)品NanoDesigner

2022年8月1日,概倫電子(股票代碼:688206.SH)宣布其承載EDA全流程的平臺(tái)產(chǎn)品NanoDesigner正式發(fā)布,加速推進(jìn)公司以DTCO理念創(chuàng)新打造應(yīng)用驅(qū)動(dòng)的EDA全流程的戰(zhàn)略落地。

2022-08-01 11:15:21 2177

2177

2177

2177如何注冊(cè)ChatGPT 全流程分享

最近ChatGPT話題簡(jiǎn)直火熱,出于體驗(yàn)的目的,寫一篇關(guān)于在國(guó)內(nèi)如何注冊(cè)ChatGPT的全流程注冊(cè),包教包會(huì)。 ChatGPT是什么? 維基百科-ChatGPT 注冊(cè)ChatGPT 準(zhǔn)備注冊(cè) 注冊(cè)前

2023-02-13 10:19:05 6

6

6

6FPGA入門之FPGA 開發(fā)流程

FPGA 的設(shè)計(jì)流程就是利用 EDA 開發(fā)軟件和編程工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過(guò)程。原理圖和HDL(Hardware description language,硬件描述語(yǔ)言)是兩種最常用的數(shù)字

2023-03-21 10:26:50 4414

4414

4414

4414廣凌全流程采購(gòu)管理系統(tǒng):能實(shí)現(xiàn)全流程監(jiān)管留痕嗎?

廣凌全流程采購(gòu)管理系統(tǒng),可實(shí)現(xiàn)全流程監(jiān)管留痕,它作為國(guó)內(nèi)自主研發(fā)實(shí)踐最久,成功案例最多的采購(gòu)管理系統(tǒng),在廣東省內(nèi),市場(chǎng)占有率高達(dá)95%以上,目前國(guó)內(nèi)100+高校使用,用戶給予了高度評(píng)價(jià)!

2022-03-30 09:26:01 1037

1037

1037

1037

FPGA設(shè)計(jì)流程

FPGA的設(shè)計(jì)流程主要包括HDL代碼編寫、RTL綜合、布局布線、靜態(tài)時(shí)序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設(shè)計(jì)的流程圖。

2023-07-04 12:06:08 2138

2138

2138

2138

FPGA的詳細(xì)開發(fā)流程

??FPGA 的詳細(xì)開發(fā)流程就是利用 EDA 開發(fā)工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過(guò)程,所以 FPGA 芯片開發(fā)流程講的并不是芯片的制造流程,區(qū)分于 IC 設(shè)計(jì)制造流程喲(芯片制造流程多麻煩,要好

2023-07-04 14:37:17 6719

6719

6719

6719

PCB行業(yè)應(yīng)如何實(shí)現(xiàn)全流程追溯?

為了解決這些問題,PCB制造企業(yè)需要對(duì) PCB產(chǎn)品進(jìn)行全流程追溯,通過(guò)數(shù)字化系統(tǒng)確保所有流程數(shù)據(jù)都在可追溯的狀態(tài)下,從而保證產(chǎn)品品質(zhì)穩(wěn)定可靠。那么,PCB行業(yè)應(yīng)如何實(shí)現(xiàn)全流程追溯?

2023-09-12 11:40:13 1833

1833

1833

1833

fpga原型驗(yàn)證流程

FPGA原型驗(yàn)證流程是確保FPGA(現(xiàn)場(chǎng)可編程門陣列)設(shè)計(jì)正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計(jì)實(shí)現(xiàn)到功能驗(yàn)證的整個(gè)過(guò)程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 3058

3058

3058

3058 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論