如圖1.9所示。這個流程圖是一個相對比較高等級的FPGA開發(fā)流程,從項目的提上議程開始,設(shè)計者需要進行FPGA功能的需求分析,然后進行模塊的劃分,比較復(fù)雜和龐大的設(shè)計,則會通過模塊劃分把工作交給一個團隊的多人協(xié)作完成。各個模塊的具體任務(wù)和功能劃分完畢(通常各個模塊間的通信和接口方式也同時被確定),則可以著手進行詳細設(shè)計,包括代碼輸入、綜合優(yōu)化、實現(xiàn)(映射和布局布線)。

為了保證設(shè)計達到預(yù)期要求,各種設(shè)計的約束輸入以及仿真驗證也穿插其間。在EDA工具上驗證無誤后,則可以生成下載配置文件燒錄到實際器件中進行板級的調(diào)試工作。從圖中的箭頭示意不難看出,設(shè)計的迭代性是FPGA開發(fā)過程中的一個重要特點,這就要求設(shè)計者從一開始就要非常認真細致,否則后續(xù)的很多工作量可能就是不斷的返工。

圖1.7 FPGA開發(fā)流程

當然了,對于沒有實際工程經(jīng)驗的初學(xué)者而言,這個流程圖可能不是那么容易理解。不過沒有關(guān)系,我們會簡化這個過程,從實際操作角度,以一個比較簡化的順序的方式來理解這個流程。如圖1.8所示,從大的方面來看,F(xiàn)PGA開發(fā)流程不過是三個階段,第一個階段是概念階段,或者也可以稱之為架構(gòu)階段,這個階段的任務(wù)是項目前期的立項準備,如需求的定義和分析、各個設(shè)計模塊的劃分;第二個階段是設(shè)計實現(xiàn)階段,這個階段包括編寫RTL代碼、并對其進行初步的功能驗證、邏輯綜合和布局布線、時序驗證,這一階段是詳細設(shè)計階段;第三個階段是FPGA器件實現(xiàn),除了器件燒錄和板級調(diào)試外,其實這個階段也應(yīng)該包括第二個階段的布局布線和時序驗證,因為這兩個步驟都是和FPGA器件緊密相關(guān)的。我們這么粗略的三個階段劃分并沒有把FPGA整個設(shè)計流程完全的孤立開來,恰恰相反,從我們的階段劃分中,我們也看到FPGA設(shè)計的各個環(huán)節(jié)是緊密銜接、相互影響的。

圖1.8 簡化的FPGA開發(fā)流程

-

FPGA開發(fā)

+關(guān)注

關(guān)注

1文章

48瀏覽量

15843

原文標題:【精品博文】勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載8:FPGA開發(fā)流程

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

出售2套:友晶科技(Terasic)原裝正品 FPGA開發(fā)板 Terasic ALTERA DE2-115

Altera攜手合作伙伴共建FPGA創(chuàng)新未來

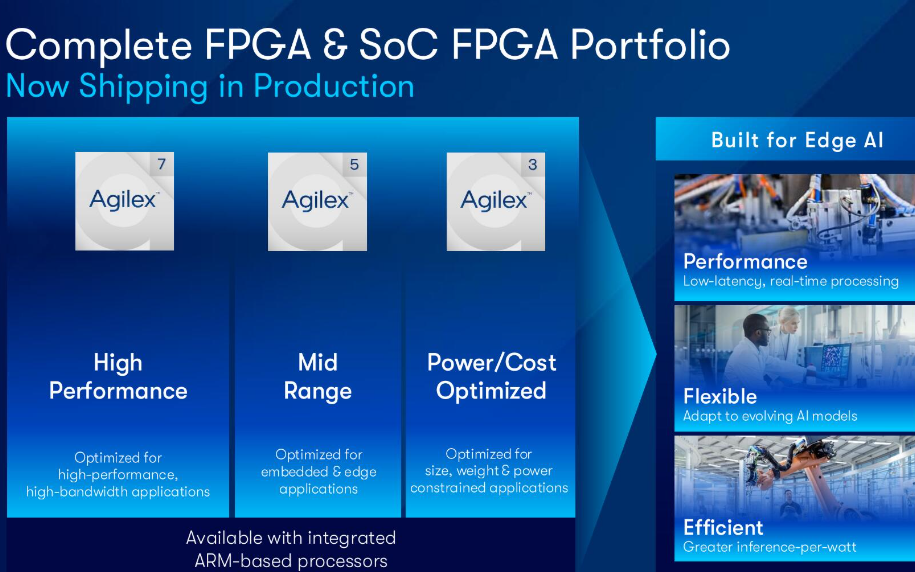

Altera Agilex 5系列FPGA與SoC產(chǎn)品榮膺2025全球電子成就獎

Altera全新推出MAX 10 FPGA封裝新選擇

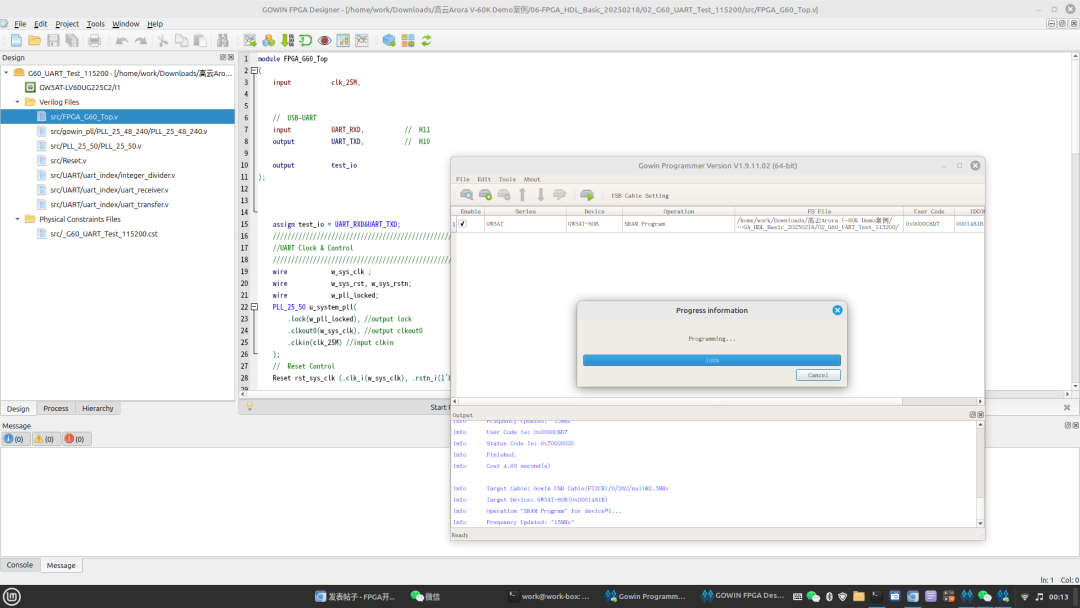

FPGA板下載調(diào)試流程

Altera進一步擴展 Agilex? FPGA 產(chǎn)品組合,全面提升開發(fā)體驗

使用Altera SoC FPGA提升AI信道估計效率

【經(jīng)驗分享】玩轉(zhuǎn)FPGA串口通信:從“幻覺調(diào)試”到代碼解析

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

適用于Versal的AMD Vivado 加快FPGA開發(fā)完成Versal自適應(yīng)SoC設(shè)計

玩轉(zhuǎn)Altera FPGA的關(guān)鍵與FPGA開發(fā)流程分享

玩轉(zhuǎn)Altera FPGA的關(guān)鍵與FPGA開發(fā)流程分享

評論