本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3467

3467

本小節通過使用XPS中的定制IP向導(ipwiz),為已經存在的ARM PS 系統添加用戶自定IP(Custom IP ),了解AXI Lite IP基本結構,并掌握AXI Lite IP的定制方法,為后續編寫復雜AXI IP打下基礎。同時本小

2012-12-23 15:39:12 19150

19150 作者:Mculover666 1.實驗目的 用HDL語言+Vivado創建一個掛載在AXI總線上的自定義IP核 2.實驗步驟 2.1.創建一個新的項目 ? ? 2.2.調用Create

2020-12-21 16:34:14 4566

4566

FPGA+ARM是ZYNQ的特點,那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個實驗是創建一個基于AXI總線的GPIO IP,利用PL的資源來擴充GPIO資源。通過這個實驗迅速入門開發

2020-12-25 14:07:02 6724

6724

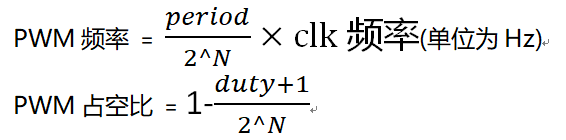

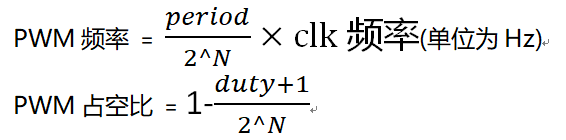

PS同PL部分的IP核連接起來。本實驗將為大家介紹如何在Vivado中構建AXI總線類型的IP核,此IP核用來產生一個PWM,用這個控制開發板上的LED,做一個呼吸燈的效果。

2021-02-01 10:13:00 6025

6025

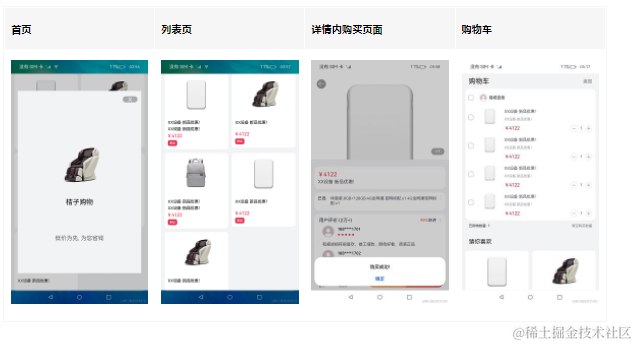

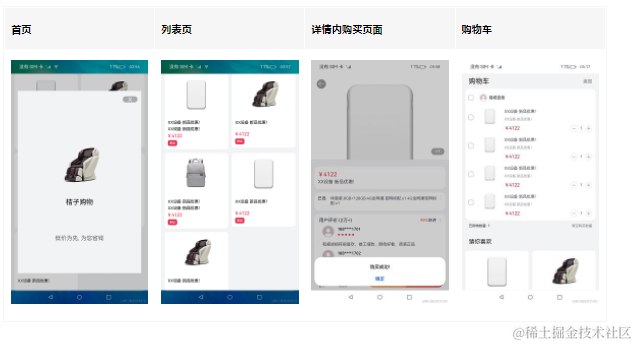

使用[Emitter]實現事件的訂閱和發布,使用[自定義彈窗]設置廣告信息。

2024-04-14 11:37:39 1661

1661

基于ArkTS的聲明式開發范式實現了三種不同的彈窗,第一種直接使用公共組件,后兩種使用CustomDialogController實現自定義彈窗

2024-05-16 18:18:05 2411

2411

自定義鍵盤是一種替換系統默認鍵盤的解決方案,可實現鍵盤個性化交互。允許用戶結合業務需求與操作習慣,對按鍵布局進行可視化重構、設置多功能組合鍵位,使輸入更加便捷和舒適。在安全防護層面,自定義鍵盤可以

2025-06-05 14:19:46 2041

2041 嗨, 當我在XPS中創建自定義AXI外設時,AXI ID(ARID,AWID)在生成的包裝器中不可用。我如何獲得這些ID?謝謝。以上來自于谷歌翻譯以下為原文Hi, When I create a

2019-03-21 09:00:19

自定義外設和自定義指令在SOPC系統中是如何運行的?怎樣去驗證?

2021-05-26 06:33:55

的fifo接口),用戶只要操作fifo接口,無需關心PCIE的內部驅動。為了便于讀者更加明白,可以深入了解PCIE,我們將會制作一個PCIE的連載系列。今天,首先說一下自定義AXI4的IP核,至于AXI

2019-12-13 17:10:42

、低功耗、易于與外設連接。

二、自定義總線協議

在RISC-V架構中,除了標準的片上總線外,還可能使用自定義總線協議來滿足特定需求。這些自定義總線協議可能根據具體的應用場景和性能要求來設計。

RIB總線

2024-12-28 17:53:16

STM32總線外設是如何分布的?

2021-09-27 06:48:55

(1個):是ARM多核架構下定義的一種接口,中文翻譯為加速器一致性端口,用來管理DMA之類的不帶緩存的AXI外設,PS端是Slave接口。我們可以雙擊查看ZYNQ的IP核的內部配置,就能發現上述的三種

2018-01-08 15:44:39

ZYNQ自定義AXI總線IP應用——PWM實現呼吸燈效果一、前言 在實時性要求較高的場合中,CPU軟件執行的方式顯然不能滿足需求,這時需要硬件邏輯實現部分功能。要想使自定義IP核被CPU訪問

2020-04-23 11:16:13

sopc builder中添加自定義ip,編寫自定義ip核的時候, avalon接口信號:clk、rst

2013-11-26 11:11:22

這學期一個半月了都在學習自定義外設,開始時做最簡單的從外設,到后來的主外設。一個接著一個做,已經完成了三個自定義外設的設計。 做了這幾個外設后,感覺學到了很多東西。在調試中遇到了很多問題,但都一一

2018-07-03 10:02:41

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:40:28

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:39:13

我寫了一個緩存模塊,里面包含有一個BlockRAM的IP核,現在想把這個緩存模塊封裝成我的一個自定義ip,但是封裝完成之后仿真的時候會報錯 ,我的步驟是這樣的:1.寫一個.v文件,里面是我的緩存控制

2018-12-11 10:25:41

zynq的PS如何向一個基于AXI4-FULL協議的自定義IP批量傳輸數據?

2017-02-22 12:05:35

小弟我是學習FPGA嵌入式的新手,最近在學習使用zedboard開發板,在研究zedboard_CTT_V14.4官方例程的時候,按照附錄的程序,一直報錯,表示添加的外設DEVICE_ID沒有定義

2015-04-22 20:54:49

是Vivado中十分常用的自定義IP核,使用AXI接口的IP,能夠方便的連接到軟核(MicroBlaze)或硬核(Zynq)的總線上,方便軟核或硬核對其進行讀寫操作。本設計的重點是使用FPGA邏輯設計獨立

2016-12-16 11:00:37

LED_IP、IIC_IP1.2搭建基本硬核、AXI接口、GPIO外設1.3自定義IP:File->NewIP Location 1.4記得要在 led_ip_v1_0.v聲明接口wire、在

2015-06-11 23:52:23

8.1.1 系統框圖框圖中的UART用于打印信息,Breath LED IP核為自定義的IP核,McroBlaze處理器通過AXI接口為LED IP模塊發送配置數據,從而來控制LED燈。8.2實驗任務

2020-10-17 11:52:28

的方式來自定義IP核,支持將當前工程、工程中的模塊或者指定文件目錄封裝成IP核,當然也可以創建一個帶有AXI4接口的IP核,用于MicroBlaze軟核處理器和可編程邏輯的數據通信。本次實驗選擇常用的方式

2020-10-19 16:04:35

Vivado軟件中,通過創建和封裝IP向導的方式來自定義IP核,支持將當前工程、工程中的模塊或者指定文件目錄封裝成IP核,當然也可以創建一個帶有AXI4接口的IP核,用于PS和PL的數據通信。本次實驗

2020-09-09 17:01:38

`附件為小梅哥SOPC公開課第二課NIOS II自定義IP的設計與使用的建隨堂工程。小梅哥SOPC公開課第二課主要講解如何使用Verilog自己編寫一個符合NIOS II Avalon MM接口總線

2016-08-13 11:04:32

)!問題是這樣的:我開發NIOS II,基本上都是自己編寫IP核的,比較省資源,自由度也高,而自定義IP核,都是要用上自定義中斷的(IRQ),更新版本后(13.1),出現下在一個問題,請看圖: 看圖

2014-05-06 13:06:30

我正在為 OTA 目的開發自定義引導加載程序。我在一個假設下成功地做到了這一點,即 .bin 文件可以被 4 整除。這意味著因為它是 32 位的,所以即使最后一部分也會在一個完整的存儲單元中。這是正確的嗎?

2023-01-06 09:02:47

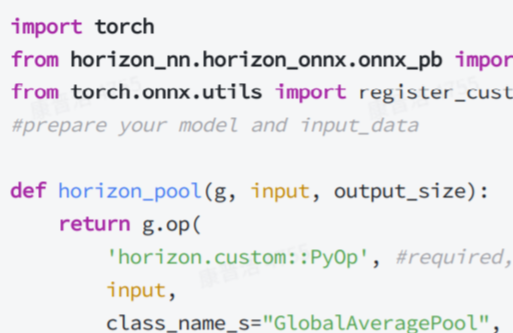

如何使用BMLang開發自定義的算子

2023-09-18 06:57:11

如何在Libero的開發環境下封裝通用的自定義的IP核?請各位大俠指點!

2019-11-13 23:09:18

我正在嘗試在 Nucleo-H743ZI2 評估板上開發自定義引導加載程序。但是引導加載程序不會跳轉到應用程序代碼。我參考了有關該主題的其他帖子,并從中采納了一些代碼。我已經將應用程序和引導加載程序的代碼閃存到 0x8020000 和 0x8000000 的相應內存位置。請指出我提供的代碼中的問題。

2023-01-29 07:02:52

斷開連接的應用程序提供支持。在這里,我的問題是如何開發自定義連接器..?我沒有 sailpoint 提供的包含“AbstractConnector”類的 jar 文件。這樣我就可以編寫自己的課程并進

2023-04-27 06:24:53

如何在E203 中添加自定義的外設,困擾已久,以下是一個從別處借鑒而來的方法:

1、設計好自定義外設的RTL后,在其中添加ICB總線的握手協議和讀寫寄存器。

2、設計一個對外接口,用來設定

2025-10-20 10:38:33

大家好,我正在使用zedboard創建一個AXI接口應用程序,以突發模式從ARM發送64字節數據到FPGA。為此,我在vivado中創建了一個自定義AXI從站,選擇它作為AXI FULL(因為AXI

2020-08-12 10:37:46

嗨,我開始使用Vivado了。我正在嘗試配置從Dram讀取數據的自定義IP,處理它們然后將結果發送到Bram控制器。我想過使用AXI主接口制作自定義IP。但是,我不知道將AXI主信號連接到我的自定義邏輯,以便我可以從Dram讀取數據并將結果發送到Bram。謝謝。

2020-05-14 06:41:47

我看到 Espressif 提供了二進制映像和 Windows 工具,以適應其產品的 WiFi 和藍牙的 FCC 測試。是否有任何支持 API 以便我可以開發自己的自定義固件以進行 FCC 測試?請注意,我們的產品中還有其他 RF 無線電,因此我們需要開發自定義固件以在多個無線電之間進行共存測試。

2023-03-02 08:11:16

1、?構建自定義AXI4-Stream FIR濾波器 AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程

2022-11-07 16:07:43

`玩轉Zynq連載24——用戶自定義IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https://pan.baidu.com/s

2019-09-15 09:55:57

`玩轉Zynq連載25——[ex04] 基于Zynq PL的自定義IP核集成更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https

2019-09-20 11:35:29

EVAL-AD7960FMCZ評估版通過LPC接口與zedboard連接,在AXI總線上自定義了一個AD采集的IP核,然后把這個IP映射到虛擬地址空間,然后讀取AD采集的數據通過以太網發送到pc機

2018-12-11 11:38:18

有意見了~今天帶大家來設計一個自定義的IP核,我們從最基本的做起,包括datasheet 的理解,設計的整體框架,AD轉換代碼的編寫,仿真,Avalon-MM總線接口的編寫,硬件系統還是基于上次的硬件

2015-02-01 12:39:08

本文主要介紹了如何開發基于TCP/IP 協議網絡編程的自定義通訊協議,在QNX,Linux 和Windows 三種不同的操作系統平臺下實現多節點間的互相通訊。測試結果表明,該協議可以方便高

2009-05-30 09:16:04 14

14 自定義函數測試學習工程

2010-07-01 16:37:44 5

5 SOPC中自定義外設和自定義指令性能分析

NiosII是一個建立在FPGA上的嵌入式軟核處理器,靈活性很強。作為體現NiosII靈活性精髓的兩個最主要方面,自

2009-03-29 15:12:49 1838

1838

本文介紹了基于Avalon總線SHT11溫濕度傳感器自定義IP核的開發流程,利用有限狀態機設計了驅動硬件邏輯,并且基于NiosII嵌入式處理器構建了一個用戶定制的嵌入式系統。在SOPC中,設計人員可以靈活添加IP核,減輕設計負擔,避免重復工作。

2013-01-28 18:41:04 12387

12387

AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 12

12 FPGA的IP核設計技術的系列資料,大家可以收集看下,這些都是我看過過濾后留下的,感覺不錯,希望對大家有幫助

2015-11-30 17:47:59 5

5 1602液晶能夠顯示自定義字符,能夠根據讀者的具體情況顯示自定義字符。

2016-01-20 15:43:51 1

1 Delphi教程自定義系統的About項,很好的Delphi資料,快來下載學習吧。

2016-03-16 14:46:37 3

3 JAVA教程之自定義光標,很好的學習資料。

2016-03-31 11:13:36 7

7 Labview之自定義錯誤,很好的Labview資料,快來下載學習吧。

2016-04-19 11:17:14 0

0 C#教程之自定義屏保,很好的C#資料,快來學習吧。

2016-04-20 09:59:37 7

7 C#教程之自定義水晶按鈕控件,很好的C#資料,快來學習吧。

2016-04-20 10:50:17 6

6 C#教程之自定義動畫鼠標,很好的C#資料,快來學習吧。

2016-04-20 14:46:25 4

4 易語言是一門以中文作為程序代碼編程語言學習例程:自定義信息框模塊

2016-06-07 10:41:41 2

2 易語言是一門以中文作為程序代碼編程語言學習例程:自定義進度復制文件

2016-06-07 10:41:41 7

7 易語言是一門以中文作為程序代碼編程語言學習例程:自定義鼠標光標

2016-06-07 10:41:41 2

2 Xilinx FPGA工程例子源碼:EDK中PS2自定義IP

2016-06-07 11:44:14 4

4 可以說zybo是mini-zedboard。Zybo全棧開發教程共分為三部分:自定義IP、移植Linux操作系統、編寫驅動模塊和應用。通過這三部分你將能夠全面熟悉Zynq AP SoC架構的開發流程,包括FPGA邏輯電路設計、軟件編程、Linux操作。

2017-11-10 14:49:02 4547

4547

對外設進行測試。以后還有一個很重要的自定義用戶Ipcore設計,下個實驗來做下這個(一開始以簡單的led和sw為例)。這個實驗就使用呢自帶外設IP。

2017-02-09 14:23:11 2496

2496

認識zedboard板子也有半個多月了,期間有不少雜事,學的也不是很認真,最近幾天在學習如何利用AXI總線進行PS和PL部分的相互通信,利用自定義的IP核實現了簡易的計算功能(只有加減),下面對實驗的過程和自己的理解進行一下記錄。

2018-07-12 03:45:00 2995

2995

本小節通過使用XPS中的定制IP向導(ipwiz),為已經存在的ARM PS 系統添加用戶自定IP(Custom IP ),了解AXI Lite IP基本結構,并掌握AXI Lite IP的定制方法,為后續編寫復雜AXI IP打下基礎。

2017-02-10 20:37:12 6312

6312 今天所討論的內容就是通過QT開發的GUI軟件來控制ZedBoard板上的硬件外設,完整的信號鏈如下:QT GUI → Linux Driver → AXI Bus → My_GPIO

2017-02-11 01:28:12 2938

2938

由于Xilinx已經為我們做了大部分的鋪墊工作,因此裸奔控制外設這一步就顯得十分簡單了,如果不用Linux和圖形界面顯示,大概我的作品早早的就完成了吧。

2017-02-11 02:02:11 1228

1228

本文先總結不同AXI IP核的實現的方法,性能的對比,性能差異的分析,可能改進的方面。使用的硬件平臺是Zedboard。 不同的AXI總線卷積加速模塊的概況 這次實現并逐漸優化了三個版本的卷積加速模塊,先簡要描述各個版本的主要內容。

2018-06-29 14:34:00 8923

8923

本工程目的是自定義一個IP,用于對OV2643攝像頭的進行配置。重點有3個,一是需要在定制板上建立系統(即我們使用的不是現有的開發板,無官方的板級支持包);二是自建IP;三是IIC總線在EDK中

2017-09-15 17:25:30 12

12 AXI總線的MicroBlaze雙核SoPC系統設計

2017-10-31 08:54:44 8

8 本文包含兩部分內容:1)AXI接口簡介;2)AXI IP核的創建流程及讀寫邏輯分析。 1AXI簡介(本部分內容參考官網資料翻譯) 自定義IP核是Zynq學習與開發中的難點,AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

Atmel小貼士 如何開發自定義應用程序

2018-07-11 00:05:00 2739

2739 萊迪思半導體公司推出7款全新的模塊化IP核,支持屢獲殊榮的CrossLink FPGA產品系列,可為消費電子、工業和汽車應用提供更高的設計靈活性。這些模塊化IP核為客戶提供創建自定義視頻橋接解決方案所需的構建模塊。

2018-07-22 12:09:00 987

987 了解如何使用Vivado的創建和封裝IP功能創建可添加自定義邏輯的AXI外設,以創建自定義IP。

2018-11-29 06:48:00 7675

7675

自定義sobel濾波IP核 IP接口遵守AXI Stream協議

2019-08-06 06:04:00 4566

4566 完成后,請執行相同的操作,但不要選擇自定義rom,而是選擇間隙。安裝間隙之前需要使用一些自定義rom,您可以從自定義rom的開發人員網頁上了解,如果他們沒有提及任何相關內容,只需在自定義rom

2019-11-05 10:48:24 6027

6027 ?? 在實際開發過程中,我們經常會遇到一些系統原有組件無法滿足的情況,而 HarmonyOS 提供了自定義組件的方式,我們使用自定義組件來滿足項目需求。 ???? 自定義組件是由開發者定義的具有一定

2021-11-10 09:27:16 3770

3770

HarmonyOS 開發自定義組件目前還不是很豐富,在開發過程中常常會有一些特殊效果的組件,這就需要我們額外花一些時間實現。

2022-01-04 13:49:30 3128

3128 自定義組件 1.自定義組件-particles(粒子效果) 2.自定義組件- pulse(脈沖button效果) 3.自定義組件-progress(progress效果) 4.自定義組件

2022-04-08 10:48:59 15

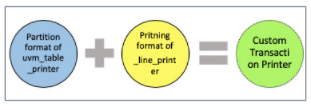

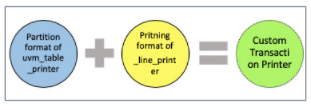

15 為了開發自定義打印機,所需的打印格式在 emit() 函數中進行了編程,該函數覆蓋了父類 (uvm_printer) 的相同函數。此處顯示了有關如何開發組件的基本思想的圖示。

2022-06-20 14:34:05 2099

2099

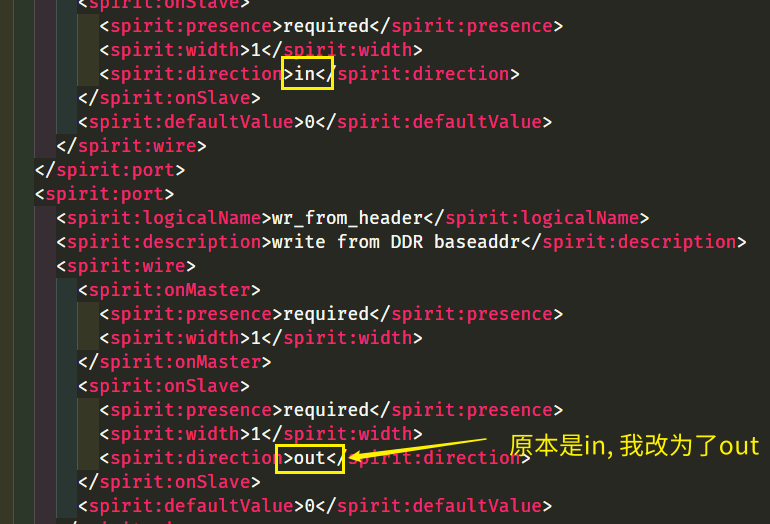

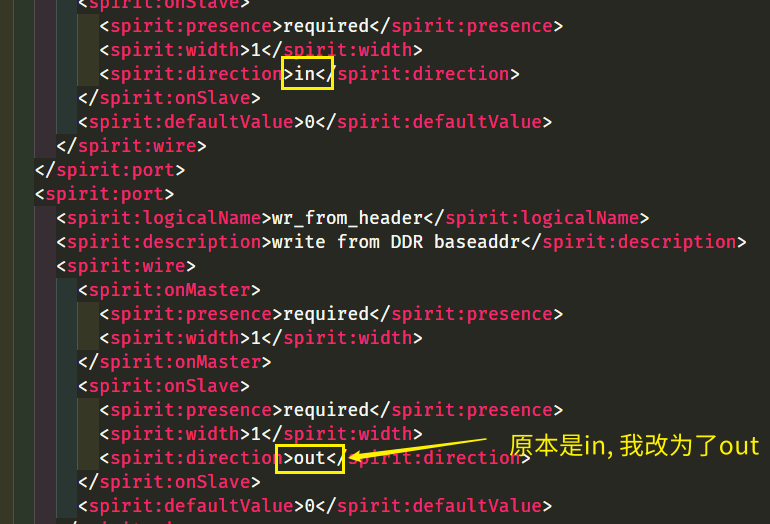

因為 BD 中連線太多,所以想自定義下 interface 簡化連線,定義好了一個 interface,但當準備在自定義 IP 中指定它時,發現我把一個信號的方向搞錯了,應該定義成 out,但實際定義成了 in,所以想簡單的改一下方向。

2022-08-02 09:49:46 3914

3914

自定義彈窗其實也是比較簡單的,通過CustomDialogController類就可以顯示自定義彈窗。

2022-08-31 08:24:36 3523

3523 AWPLC 是 ZLG 自主研發的 PLC 系統(兼容 IEC61131-3),本文用定時器為例介紹一下如何擴展自定義功能塊。

2022-10-26 11:50:01 1579

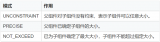

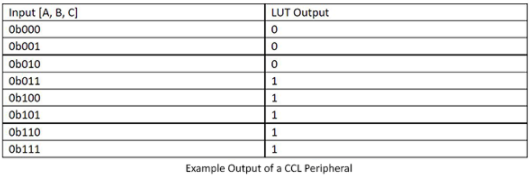

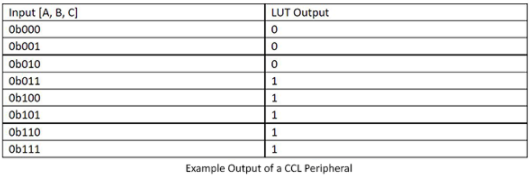

1579 PIC? 和 AVR? 微控制器 (MCU) 上的自定義邏輯外設是功能強大的工具,可用于創建獨立于 CPU 運行的分立邏輯小塊。PIC 微控制器具有可配置邏輯單元 (CLC),而 AVR 微控制器

2023-05-06 09:51:42 1744

1744

labview自定義精美控件

2023-05-15 16:46:23 22

22 最近需要用到AXI接口的模塊,xilinx的IP核很多都用到了AXI總線進行數據和指令傳輸。如果有多個設備需要使用AXI協議對AXI接口的BRAM進行讀寫,總線之間該如何進行仲裁,通信?

2023-06-19 15:45:14 14453

14453

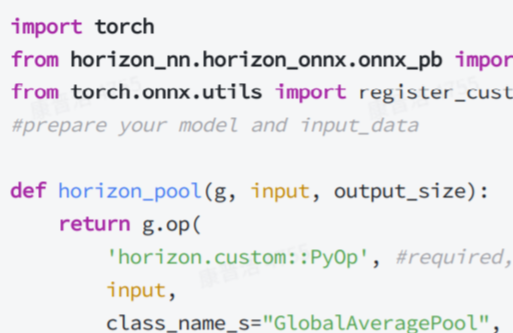

一個完整的自定義算子應用過程包括注冊算子、算子實現、含自定義算子模型轉換和運行含自定義op模型四個階段。在大多數情況下,您的模型應該可以通過使用hb_mapper工具完成轉換并順利部署到地平線芯片上……

2022-04-07 16:11:21 4952

4952

在 Vivado 中自定義 AXI4-Lite 接口的 IP,實現一個簡單的 LED 控制功能,并將其掛載到 AXI Interconnect 總線互聯結構上,通過 ZYNQ 主機控制,后面對 Xilinx 提供的整個 AXI4-Lite 源碼進行分析。

2023-06-25 16:31:25 4882

4882

labview超快自定義控件制作和普通自定義控件制作

2023-08-21 10:32:58 14

14 組件是 OpenHarmony 頁面最小顯示單元,一個頁面可由多個組件組合而成,也可只由一個組件組合而成,這些組件可以是ArkUI開發框架自帶系統組件,比如?`Text`?、?`Button`?等,也可以是自定義組件,本節筆者簡單介紹一下自定義組件的語法規范。

2024-04-08 10:17:06 1495

1495 LIN(LocalInterconnectNetwork)協議調度表是用于LIN總線通信中的消息調度的一種機制,我們收到越來越多來自不同用戶希望能夠通過接口實現自定義LIN調度表的需求。所以在

2024-05-11 08:21:05 2038

2038

電子發燒友App

電子發燒友App

評論