為了幫助大家解決FPGA開發中碰到的相關問題,電子發燒友網和FPGA資深工程師吳厚航(網名“特權同學”)進行了深入的交談,希望能為工程師群體在電子設計道路上提供參考。

2013-08-20 14:31:45 6177

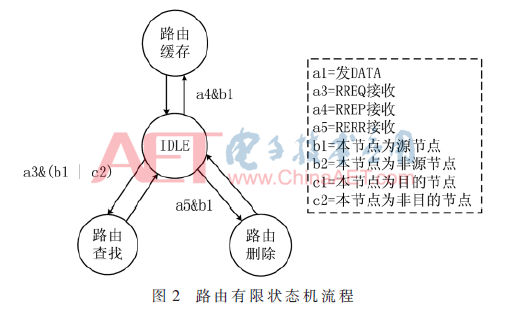

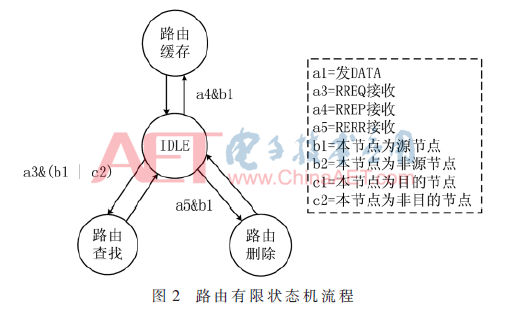

6177 本文為在FPGA中支持DSR協議的路由表項管理功能,設計一種基于有限狀態機[8]的實現方法。

2020-12-22 16:27:25 2853

2853

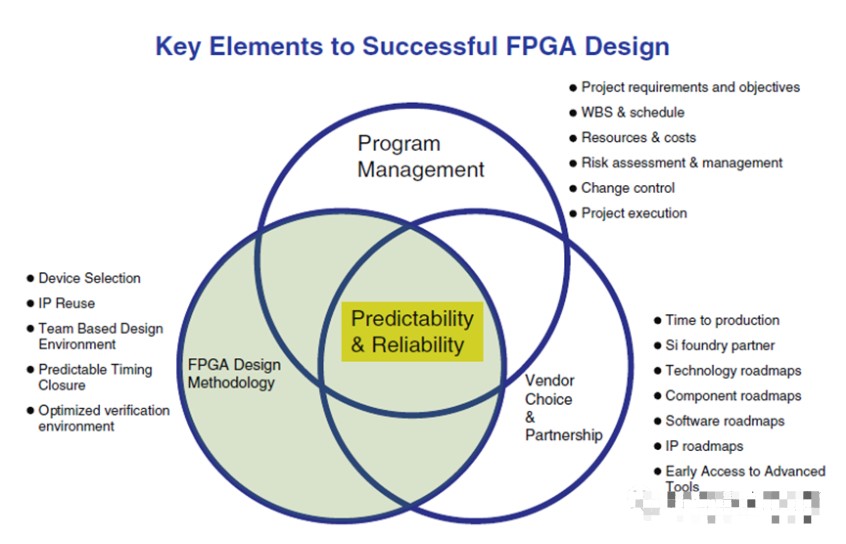

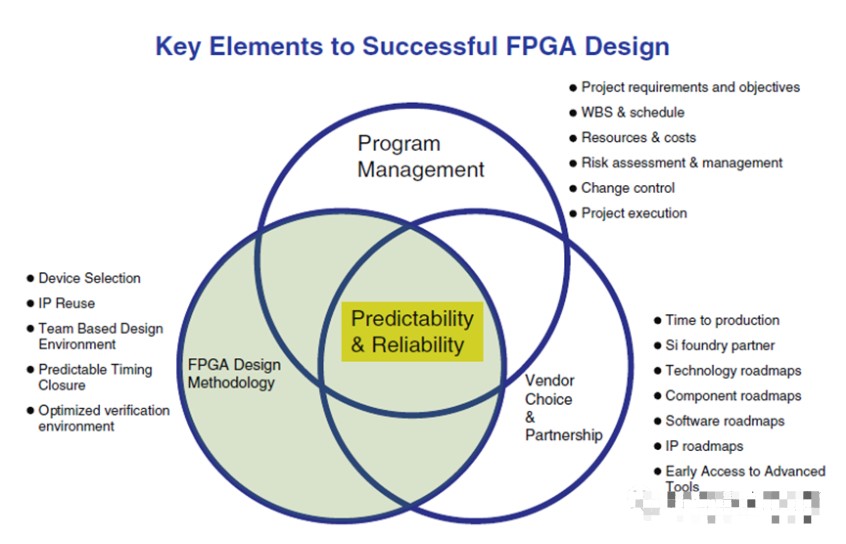

在5G無線、衛星通信、雷達探測、航天測控等復雜系統設計中,FPGA工程師扮演著重要角色。

2022-07-22 08:50:59 1547

1547 為了在越來越復雜的系統設計中,FPGA工程師之間保持高效溝通和工作推進,這就需要找到一個適合的設計方法論。目標是通過在設計團隊之間建立一個通用的方法來提高FPGA設計團隊的生產力,同時允許跨團隊交換設計模塊。

FPGA設計中的三個關鍵因素:

2022-07-22 09:02:09 1005

1005

說起 Spring 狀態機,大家很容易聯想到這個狀態機和設計模式中狀態模式的區別是啥呢?沒錯,Spring 狀態機就是狀態模式的一種實現,在介紹 Spring 狀態機之前,讓我們來看看設計模式中的狀態模式。

2023-12-26 09:39:02 3071

3071

說起Spring狀態機,大家很容易聯想到這個狀態機和設計模式中狀態模式的區別是啥呢?沒錯,Spring狀態機就是狀態模式的一種實現,在介紹Spring狀態機之前,讓我們來看看設計模式中的狀態模式

2024-06-25 14:21:02 1580

1580

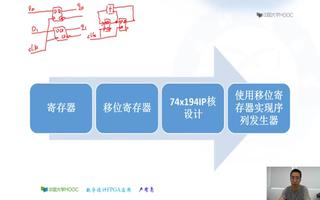

。 本書可供通信工程、電子工程、計算機、微電子等專業并有一定FPGA開發基礎的在校大學生、研究生參考,也可作為硬件工程師、FPGA工程師的工具書。40個fpga代碼練習(煉獄傳奇系列):FPGA代碼練習,包括串口、賦值、分頻、ram、流水線、鍵盤、狀態機等40篇

2020-04-22 14:47:39

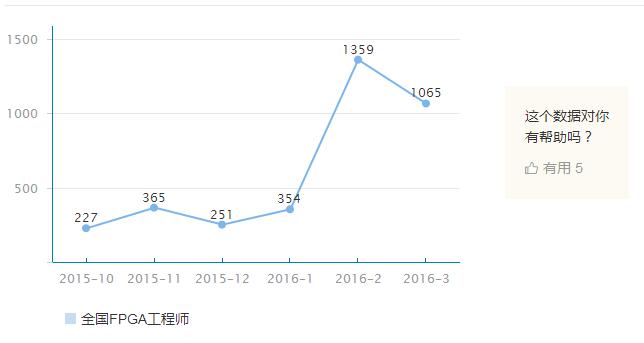

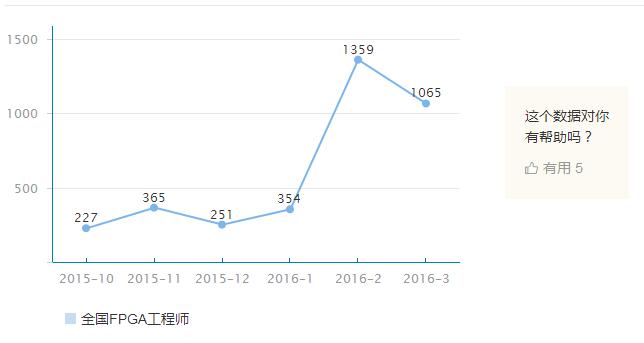

透過以下薪資待遇的數據可以看出,fpga 工程師不是青春飯,你的工作經驗越長薪資待遇越高。(來源獵聘網)

2019-08-16 15:50:26

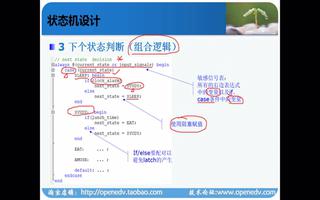

今天給大俠帶來如何寫好狀態機,狀態機是邏輯設計的重要內容,狀態機的設計水平直接反應工程師的邏輯功底,所以很多公司在硬件工程師及邏輯工程師面試中,狀態機設計幾乎是必選題目。本篇在引入狀態機設計思想

2020-09-28 10:29:23

(硬件描述語言)為工具、FPGA/CPLD器件為載體的EDA技術的應用越來越廣泛.從小型電子系統到大規模SOC(Systemonachip)設計,已經無處不在.在FPGA/CPLD設計中,狀態機是最典型

2012-01-12 10:48:26

本公司位于安徽合肥因業務需求,尋找合肥地區FPGA工程師兼職人員,若有充裕的空閑時間,有FPGA開發能力的.有意者請聯系:133-6560-7553,黃小姐

2015-07-02 16:54:59

字IC設計領域,前端驗證工作一般都是用FPGA完成的,因此FPGA工程師也是IC設計公司迫切需要的人才。FPGA/IC邏輯設計開發已經成為當前最有發展前途的行業之一,特別是熟悉硬件構架的FPGA

2018-09-26 09:58:17

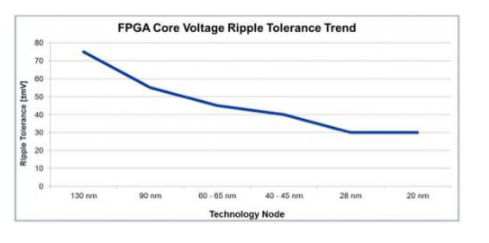

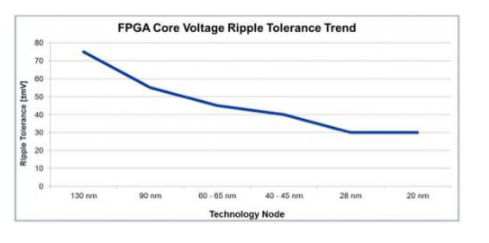

不管你是一名邏輯設計師、硬件工程師或系統工程師,甚或擁有所有這些頭銜,只要你在任何一種高速和多協議的復雜系統中使用了FPGA,你就很可能需要努力解決好器件配置、電源管理、IP集成、信號完整性和其他

2016-09-28 16:14:51

FPGA工程師的工資水平,看看你在哪一檔!這是北京地區的工程師工資水平,全國性的數據沒有找到。大家可以參考下,衡量一下自己的現狀。

2012-02-24 14:44:59

的狀態機以及高級邏輯電路。

FPGA工程師需要熟練掌握HDL語言,并能夠根據需要靈活使用這些語言。他們需要知道如何將各種邏輯電路和存儲器組合在一起,以實現所需的功能。同時,FPGA工程師還需要

2023-11-09 11:03:52

FPGA工程師面試試題

2011-03-02 09:36:39

FPGA狀態機的文書資料

2014-09-14 19:01:20

(41)FPGA狀態機一段式1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA狀態機一段式5)結語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 06:45:18

1.1 FPGA狀態機跑飛原因分析1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA狀態機跑飛原因分析;5)結束語。1.1.2 本節引言“不積跬步,無以至千里;不積小流

2021-07-29 06:15:53

FPGA狀態機為什么會跑飛呢?FPGA狀態機跑飛的原因是什么?

2021-11-01 07:52:44

及路線圖詳見報到通知)四、 課程簡介本課程為期三天,旨在幫助已經掌握一定設計基礎的工程師進一步了解FPGA邏輯設計的方法與優化技巧。講述了邏輯設計的驗證、高級狀態機的設計、基于FPGA的DSP設計方法

2009-07-24 13:13:48

FPGA有限狀態機

2013-09-08 08:45:17

,優勢在哪里?

A:在 Verilog 中,狀態機可以全部使用時序邏輯來實現,但通常會采用組合邏輯來實現狀態轉移和輸出,主要是基于以下原因:

資源利用效率:全部使用時序邏輯會導致大量的寄存器資源被消耗

2024-09-23 18:26:15

FPGA設計之浮點DSP算法實現,DSP算法是很多工程師在設計過程中都會遇到的問題,本文將從FPGA設計的角度來講解浮點DSP算法的實現。FPGA設計之浮點DSP算法實現是賽靈思工程師最新力作,資料不可多得,大家珍惜啊1FPGA設計之浮點DSP算法實現[hide][/hide]

2012-03-01 15:23:56

剛開始學fpga,讀資料,有些名詞不太理解,比如狀態機,我只知道fpga就是由查找表和觸發器構成的,狀態機這個概念是怎么提出來的,干什么使得,求大神講解,什么情況下用到

2013-04-25 18:35:55

AI時代FPGA廠商與FPGA工程師該如何轉型?

2020-06-08 11:50:21

本帖最后由 御宇1995 于 2015-6-6 15:06 編輯

實驗課要用FPGA(Altera的cycloneIV)實現交通燈,有用狀態機和非狀態機兩種方法,以下是代碼狀態機實現(一個數

2015-06-06 15:03:52

不管你是一名邏輯設計師、硬件工程師或系統工程師,甚或擁有所有這些頭銜,只要你在任何一種高速和多協議的復雜系統中使用了FPGA,你就很可能需要努力解決好器件配置、電源管理、IP集成、信號完整性和其他

2015-11-30 10:45:48

獵頭職位:FPGA研發工程師(年薪:35-60W)工作職責:1.配合軟件工程師進行產品設計過程中的軟硬件聯調和驗證;2.負責根據系統設計要求進行FPGA代碼的設計、開發與驗證;3.跟蹤FPGA廠商

2017-07-31 15:03:17

獵頭職位:FPGA開發工程師工作職責:1.負責單板邏輯功能性能調試;2.負責低速和高速總線接口在FPGA上實現;3.負責通信協議算法在FPGA上的實現;4.完成設計文檔編寫。崗位要求:1.熟練掌握

2017-07-19 14:21:56

獵頭推薦職位:FPGA開發工程師工作職責:1. 編寫設計方案,完成算法的封裝固化;2. 基于FPGA硬件開發平臺,調試、驗證負責視頻編碼算法和圖像處理算法;3. 利用***log/VHDL硬件描述語言實現

2017-07-04 15:27:02

獵頭職位:FPGA開發工程師工作職責:1.基于FPGA硬件開發平臺,調試、驗證負責視頻編碼算法和圖像處理算法;2.編寫設計方案,完成算法的封裝固化;3.利用Verilo***L硬件描述語言實現相關

2017-07-17 15:15:12

獵頭職位:FPGA開發工程師工作職責:1.基于FPGA硬件開發平臺,調試、驗證負責視頻編碼算法和圖像處理算法;2.編寫設計方案,完成算法的封裝固化;3.利用Verilo***L硬件描述語言實現相關

2017-09-11 15:59:18

。所以如果你有興趣從事 FPGA 這個行業、亦或是正在尋找這方面的工作,或者已經入行一段時間,并且希望明確今后今年的發展方向,那么這篇文章應該會對你有所幫助。和初學者相比,專業的 FPGA 工程師需要

2021-01-08 09:57:05

專業工程師分享FPGA設計中的功率計算技巧速看

2021-05-07 06:16:20

在某大型科技公司的招聘網站上看到招聘邏輯硬件工程師需要掌握SystemVerilog語言,感覺SystemVerilog語言是用于ASIC驗證的,那么做FPGA工程師有沒有必要掌握SystemVerilog語言呢?

2017-08-02 20:30:21

本壇新人,請各位大佬照顧哈:)工作需要招聘FPGA工程師1人,詳情如下:職位描述:密碼安全設備中的FPGA開發,分析設計需求,制定開發方案;負責架構設計和模塊開發,根據系統設計要求實現FPGA部分

2017-05-12 09:45:58

實現基礎的軟件(我后悔沒有跟蹤它們),并且取決于它們是否在(可能)C或Assembly中編寫,它們所做的是在Assembly中實現長塊的“開關盒”鏈或類似的東西:找到實現它的相當粗略的方法。我看不出其他的辦法。我的問題是:這是用微控制器實現狀態機的實際方式嗎?

2019-09-30 09:18:01

狀態機是邏輯設計的重要內容,狀態機的設計水平直接反應工程師的功底。

2012-03-12 16:30:24

一篇經典文獻,詳細講解了一段、兩段、三段式狀態機的實現,效率、優缺點。看完后相信會對狀態機有一個詳細的了解。 狀態機是邏輯設計的重要內容,狀態機的設計水平直接反應工程師的邏輯功底,所以許 多公司

2011-10-24 11:43:11

嵌入式軟件開發工程師與FPGA開發工程師的區別是什么?

2021-11-22 06:11:15

公司行業:航天航空公司性質:國企公司規模:1000人招聘:軟件工程師(數字信號處理方向)、硬件工程師軟件工程師:1)通信、電子、計算機專業,碩士及以上學歷;2)具有XILINX/ACTEL FPGA

2015-04-25 21:02:16

剛入行,看到網上的頭發級別好擔憂哇這年頭有頭發茂密的FPGA工程師嗎?級別.jpg

2022-09-07 15:52:28

FPGA開發工程師崗位職責:1、根據系統需求,完成FPGA器件選型和方案設計;2、負責FPGA的Verilog語言編寫、仿真、調試;3、負責FPGA的綜合和測試工作,編寫FPGA設計文檔、測試文檔等

2019-10-22 11:03:51

獵頭職位推薦:FPGA開發工程師工作職責:FPGA算法實現與調試,FPGA接口設計與調試,負責簡單的電路設計、器件選型、原理圖設計以及PCB加工跟蹤和硬件調試與其他參與項目的人員共同合作,協助完成

2013-02-18 11:26:55

獵頭職位推薦:FPGA開發工程師工作職責:FPGA算法實現與調試,FPGA接口設計與調試,負責簡單的電路設計、器件選型、原理圖設計以及PCB加工跟蹤和硬件調試與其他參與項目的人員共同合作,協助完成

2013-01-28 16:52:56

北京某上市國企,龍頭企業,招算法設計工程師(FPGA)高級、中級工程師,有意者加QQ1736526119,JD如下:崗位描述1、 負責無線通信系統物理層算法及接口相關的FPGA工作評估;2、 負責

2016-04-20 15:31:59

的特點。再加上FPGA自身具有的設計周期短、開發成本低和設計靈活等特點,基于FPGA的開發越來越流行。為了幫助大家解決FPGA開發中碰到的相關問題,電子發燒友網和FPGA資深工程師吳厚航(網名“特權同學

2013-08-20 16:50:48

納睿達科技有限公司誠招“FPGA工程師、嵌入式系統開發工程師”【FPGA工程師】學歷要求:研究生 工作經驗:不限 崗位職責:1、主要從事設備產品中的FPGA的設計、開發,按流程、規范完成所承擔

2018-01-13 14:17:35

獵頭職位:FPGA軟件工程師【上海】崗位描述:1. 根據系統需求,參與FPGA器件選型、方案設計,負責邏輯設計、仿真和調試;2. 編寫FPGA設計文檔、測試文檔與使用文檔等;3. 協助硬件工程師完成

2017-02-17 11:06:31

如何寫好狀態機:狀態機是邏輯設計的重要內容,狀態機的設計水平直接反應工程師的邏輯功底,所以許多公司的硬件和邏輯工程師面試中,狀態機設計幾乎是必選題目。本章在引入

2009-06-14 19:24:49 98

98 本文給出了采用這些技術的高速環境狀態機設計的規范及分析方法和優化方法,并給出了相應的示例。

為了使FPGA或CPLD中的狀態機設計

2009-04-15 11:27:04 801

801

本設計采用賽靈思Spartan-3E系列FPGA芯片,在基于FPGA器件的設計中,狀態機是目前應用最為普遍的設計方法之一。

2012-06-06 15:59:38 31

31 FPGA學習資料教程之工程師創新設計之FPGA開發

2016-09-01 16:40:07 0

0 FPGA學習資料教程——華清遠見FPGA代碼-狀態機

2016-10-27 18:07:54 9

9 我的許多朋友都是經驗豐富的嵌入式設計工程師,但他們都是微控制器(MCU)背景,因此對于FPGA是什么以及FPGA能做什么只有一個模糊的概念。如果問急了,他們會說“你可以通過配置FPGA讓它做

2017-02-08 15:56:11 702

702

練習九.利用狀態機的嵌套實現層次結構化設計目的:1.運用主狀態機與子狀態機產生層次化的邏輯設計;

2017-02-11 05:52:50 3660

3660

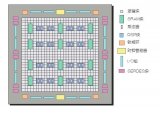

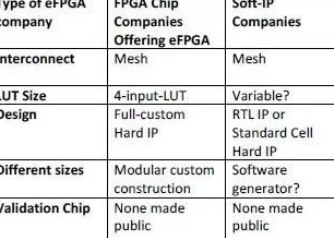

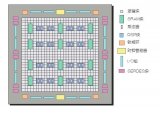

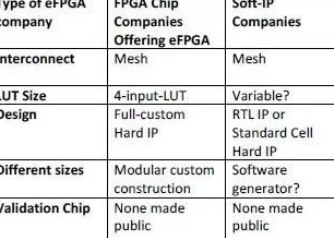

最近eFPGA的概念越來越火了,究竟那些提供嵌入式FPGA IP (eFPGA)的廠商提供的產品之間有沒有區別,區別大不大,做IC設計的工程師應該如何選擇?

2017-11-10 10:16:49 8681

8681

狀態機,并通過解析各階段數據狀態變化,驗證了各節點通信數據的正確性。實驗結果表明,基于上述狀態機的FPGA實現EtherCAT從站基本通信鏈路是完全可行的。

2017-11-15 12:04:01 20754

20754

描述語言)為工具、FPGA/CPLD器件為載體的EDA技術的應用越來越廣泛.從小型電子系統到大規模SOC(Systemonachip)設計,已經無處不在.在FPGA/CPLD設計中,狀態機是最典型、應用最廣泛的時序電路模塊,如何設計一個穩定可靠的狀態機是我們必須面對的問題.

2017-11-24 20:59:08 3889

3889

字IC設計領域,前端驗證工作一般都是用FPGA完成的,因此FPGA工程師也是IC設計公司迫切需要的人才。 FPGA/IC邏輯設計開發已經成為當前最有發展前途的行業之一,特別是熟悉硬件構架的FPGA系統工程師。

2018-04-19 09:03:41 55036

55036

這個問題是老石在知乎上看到的,大家的回答都是“調板子”、“debug”、“硬件實現”等等。作為FPGA工程師,老石看了實在要報以一個禮貌的微笑。 換個角度看,難道其他硬件工程師就不具備調板子

2019-02-23 11:28:01 1776

1776 換個角度看,難道其他硬件工程師就不具備調板子、debug、硬件實現的能力了?或者,為什么說這些是專屬于FPGA工程師的核心競爭力?

2019-04-05 07:57:00 4829

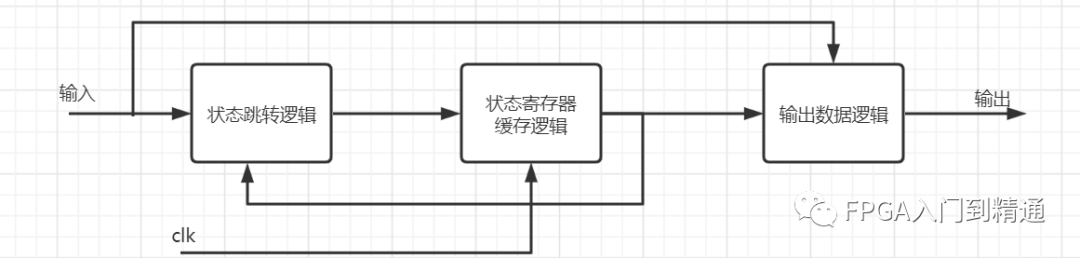

4829 狀態機由狀態寄存器和組合邏輯電路構成,能夠根據控制信號按照預先設定的狀態進行狀態轉移,是協調相關信號動作,完成特定操作的控制中心。狀態機分為摩爾(Moore)型狀態機和米莉(Mealy)型狀態機。

2019-09-19 07:00:00 2999

2999

狀態機可以用兩種方法實現:豎著寫(在狀態中判斷事件)和橫著寫( 在事件中判斷狀態)。這兩種實現在本質上是完全等效的,但在實際操作中,效果卻截然 不同。

2019-10-09 07:09:00 2956

2956 狀態機可以用兩種方法實現:豎著寫(在狀態中判斷事件)和橫著寫( 在事件中判斷狀態)。這兩種實現在本質上是完全等效的,但在實際操作中,效果卻截然 不同。

2019-10-09 07:08:00 2068

2068 狀態機由狀態寄存器和組合邏輯電路構成,能夠根據控制信號按照預先設定的狀態進行狀態轉移,是協調相關信號動作,完成特定操作的控制中心。狀態機分為摩爾(Moore)型狀態機和米莉(Mealy)型狀態機。

2019-10-09 07:07:00 4101

4101 關于狀態機的一個極度確切的描述是它是一個有向圖形,由一組節點和一組相應的轉移函數組成。狀態機通過響應一系列事件而“運行”。每個事件都在屬于“當前” 節點的轉移函數的控制范圍內,其中函數的范圍是節點

2019-10-09 07:05:00 4116

4116 狀態機有三種描述方式:一段式狀態機、兩段式狀態機、三段式狀態機。下面就用一個小例子來看看三種方式是如何實現的。

2019-08-29 06:09:00 3374

3374

狀態機由狀態寄存器和組合邏輯電路構成,能夠根據控制信號按照預先設定的狀態進行狀態轉移,是協調相關信號動作、完成特定操作的控制中心。

2019-12-04 07:03:00 3640

3640

狀態機由狀態寄存器和組合邏輯電路構成,能夠根據控制信號按照預先設定的狀態進行狀態轉移,是協調相關信號動作,完成特定操作的控制中心。狀態機分為摩爾(Moore)型狀態機和米莉(Mealy)型狀態機。

2019-05-28 07:03:49 3390

3390 要想理解和管理FPGA設計師如何在設計周期早期在FPGA上實現高處理狀態和低處理狀態之間的轉換,將顯著影響電源設計師優化電源設計和滿足系統功耗要求的可選方法。FPGA中的每個電源軌沒有要求也沒有

2020-11-18 17:40:38 1403

1403

本文檔的主要內容詳細介紹的是使用verilog HDL實現狀態機8位流水燈的程序和工程文件免費下載。

2020-10-16 16:20:25 23

23 之前寫過一篇狀態機的實用文章,很多朋友說有幾個地方有點難度不易理解,今天給大家換種簡單寫法,使用函數指針的方法實現狀態機。 狀態機簡介 有限狀態機FSM是有限個狀態及在這些狀態之間的轉移和動作等行為

2020-10-19 09:36:53 2958

2958

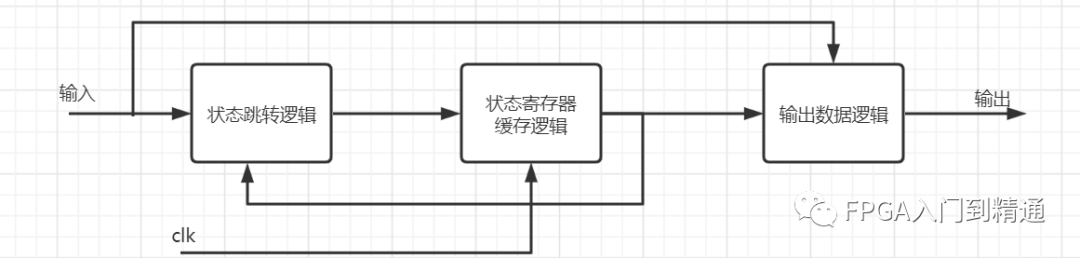

輸出部分外, 有限狀態機還含有一組具有“記憶”功能的寄存器, 這些寄存器的功能是記憶有限狀態機的內部狀態, 它們常被稱為狀態寄存器。在有限狀態機中, 狀態寄存器的的下一個狀態不僅與輸入信號有關, 而且還與該寄存器的當

2020-11-04 17:17:04 12

12 是FPGA設計中一種非常重要、非常根基的設計思想,堪稱FPGA的靈魂,貫穿FPGA設計的始終。 02. 狀態機簡介 什么是狀態機:狀態機通過不同的狀態遷移來完成特定的邏輯操作(時序操作)狀態機是許多數字系統的核心部件, 是一類重要的時序邏輯電路。通常包括三個部分: 下一個

2020-11-05 17:58:47 8700

8700

經典雙進程狀態機的FPGA實現(含testbeach)(肇慶理士電源技術有限公司圖片)-該文檔為經典雙進程狀態機的FPGA實現(含testbeach)總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………? ??

2021-08-31 13:26:52 3

3 (41)FPGA狀態機一段式1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA狀態機一段式5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:41:59 0

0 LABVIEW的狀態機實現資料合集

2022-01-04 11:18:40 51

51 一個工程師有關FPGA項目的9個感言

2022-02-16 16:21:31 2729

2729 作為一名FPGA工程師,我們的任務就是把某些特定的邏輯行為雕刻到FPGA芯片上,通過設計邏輯電路達到預期目的。

2022-03-14 11:23:08 2617

2617 為 FPGA 供電簡便易行 -寫給采用 FPGA 的數字工程師

2022-11-07 08:07:37 7

7 在Verilog HDL中可以用許多種方法來描述有限狀態機,最常用的方法是用always語句和case語句。

2023-03-23 14:06:11 997

997 FPGA的特點是并行執行,但如果需要處理一些具有前后順序的事件,就需要使用狀態機。

2023-05-22 14:24:12 1925

1925

狀態機往往是FPGA 開發的主力。選擇合適的架構和實現方法將確保您獲得一款最佳解決方案。 FPGA 常常用于執行基于序列和控制的行動, 比如實現一個簡單的通信協議。對于設計人員來說,滿足這些行動

2023-07-18 16:05:01 1984

1984

狀態機的基礎知識依然強烈推薦mooc上華科的數字電路與邏輯設計,yyds!但是數電基礎一定要和實際應用結合起來,理論才能發揮真正的價值。我們知道FPGA是并行執行的,如果我們想要處理具有前后順序的事件就需要引入狀態機。

2023-07-28 10:02:04 1769

1769

狀態機,又稱有限狀態機(Finite State Machine,FSM)或米利狀態機(Mealy Machine),是一種描述系統狀態變化的模型。在芯片設計中,狀態機被廣泛應用于各種場景,如CPU指令集、內存控制器、總線控制器等。

2023-10-19 10:27:55 12738

12738 FPGA工程師的就業趨勢呈現出積極的態勢。隨著科技的發展,FPGA(現場可編程門陣列)在通信、汽車、醫療、航空航天等領域的應用越來越廣泛,對FPGA工程師的需求也在不斷增加。

2024-03-14 15:47:20 3072

3072 FPGA工程師的前景看起來相當積極和廣闊。隨著5G通信、物聯網、邊緣計算和人工智能等技術的快速發展,FPGA工程師的需求將進一步增加。FPGA芯片具有可編程性強、并行處理能力強、功耗低等特點,因此在

2024-03-14 16:32:39 4806

4806 在FPGA(現場可編程門陣列)中實現狀態機是一種常見的做法,用于控制復雜的數字系統行為。狀態機能夠根據當前的輸入和系統狀態,決定下一步的動作和新的狀態。這里,我們將詳細探討如何在FPGA設計中實現狀態機,包括其基本概念、類型、設計步驟、實現方法以及優化策略。

2024-07-18 15:57:34 1843

1843

電子發燒友App

電子發燒友App

評論