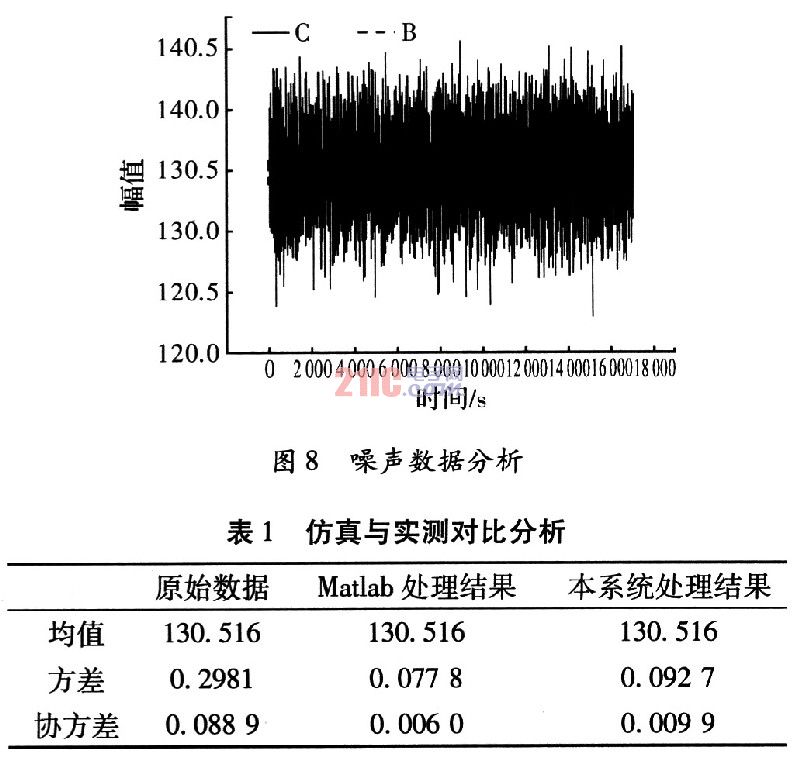

在Matlab/Simulink環(huán)境下,采用DSP Builder模塊搭建FIR模型,根據(jù)FDATool工具對(duì)FIR濾波器進(jìn)行了設(shè)計(jì),然后進(jìn)行系統(tǒng)級(jí)仿真和ModelSim功能仿真,其仿真結(jié)果表明其

2013-10-08 13:39:06 10636

10636

本文簡(jiǎn)要介紹了FIR數(shù)字濾波器的結(jié)構(gòu)特點(diǎn)和基本原理,提出基于FPGA和DSP Builder的FIR數(shù)字濾波器的基本設(shè)計(jì)流程和實(shí)現(xiàn)方案。##FIR 數(shù)字濾波器的詳細(xì)設(shè)計(jì)。

2014-07-24 15:30:05 9476

9476

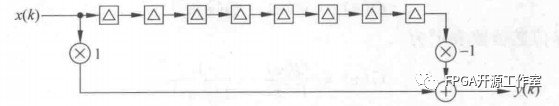

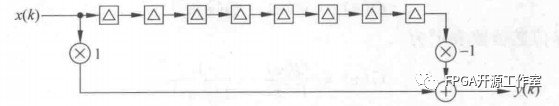

sample rate convert 和 down sample rate convert 的FPGA實(shí)現(xiàn)打下基礎(chǔ)。 1 梳狀濾波器 圖1 梳狀濾波器結(jié)構(gòu) 梳狀濾波器的兩端為1和-1的權(quán)值,具有簡(jiǎn)單

2020-11-21 09:57:00 6749

6749

什么是抽取?DDC的作用是什么?DDC濾波器應(yīng)該多寬?DDC濾波器的頻率是固定的嗎?DDC濾波器是否影響SNR和SFDR?ADC能否提供多個(gè)DDC?

2021-05-21 06:34:42

fpga實(shí)現(xiàn)濾波器fpga實(shí)現(xiàn)濾波器在利用FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理方面,分布式算法發(fā)揮著關(guān)鍵作用,與傳統(tǒng)的乘加結(jié)構(gòu)相比,具有并行處理的高效性特點(diǎn)。本文研究了一種16階FIR濾波器的FPGA設(shè)計(jì)方法

2012-08-12 11:50:16

。本文研究了一種16階FIR濾波器的FPGA設(shè)計(jì)方法,采用Verilog HDI語言描述設(shè)計(jì)文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平臺(tái)上進(jìn)行了實(shí)驗(yàn)仿真及時(shí)序分析,并探討了實(shí)際工程中硬件資源利用率及運(yùn)算速度等問題。

2012-08-11 18:27:41

AD9689芯片 DDC抽取濾波器進(jìn)行多芯片同步時(shí)使用什么信號(hào)進(jìn)行復(fù)位同步?是sysref信號(hào)還是什么?datasheet沒有提供說明。

2023-12-07 06:43:42

CIC抽取濾波器MATLAB仿真和FPGA實(shí)現(xiàn)(1)設(shè)計(jì)理想濾波器目標(biāo):1、濾波器在有效頻段內(nèi)紋波滿足設(shè)計(jì)要求。2、抽取或內(nèi)插處理后在有效頻段內(nèi)不產(chǎn)生混疊。3、濾波器實(shí)現(xiàn)簡(jiǎn)單,需要資源較少。這個(gè)

2021-08-17 08:27:40

跪求protel仿真濾波器的例子!!!!!!{:16:}{:16:}

2013-08-20 15:47:52

主要任務(wù):1.熟悉低通濾波器的原理及應(yīng)用2.熟悉FPGA的硬件描述3.FPGA如何實(shí)現(xiàn)小數(shù)分頻器4.用MATLAB對(duì)低通濾波器的驗(yàn)證預(yù)期成果或目標(biāo):FPGA對(duì)低通濾波器的Verilog(或VHDL

2013-04-04 22:16:11

設(shè)計(jì)一般采用CIC、HB、FIR級(jí)聯(lián)的形式組成。同時(shí),由于CIC濾波器的通帶性能實(shí)在太差,所以中間還要加上一級(jí)PFIR濾波器以平滑濾波器的通帶性能。

2019-09-20 06:13:11

基于FPGA的DDC設(shè)計(jì)及仿真

2012-08-06 12:12:19

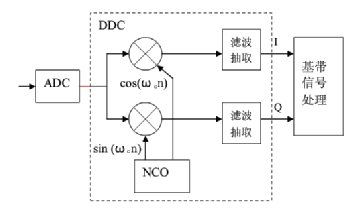

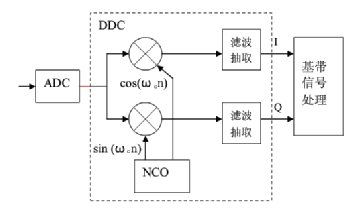

DDC是由哪幾部分組成的?基于FPGA的DDC該怎樣去設(shè)計(jì)?如何對(duì)DDC進(jìn)行仿真測(cè)試?

2021-05-27 07:16:24

基于FPGA的FIR濾波器IP仿真實(shí)例 AT7_Xilinx開發(fā)板(USB3.0+LVDS)資料共享 騰訊鏈接:https://share.weiyun.com/5GQyKKc 百度網(wǎng)盤鏈接

2019-07-16 17:24:22

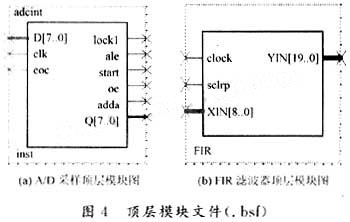

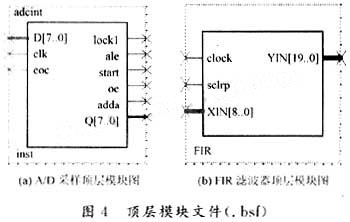

設(shè)計(jì)要求: 利用所學(xué)知識(shí),采用VHDL語言完成FIR濾波器的設(shè)計(jì)仿真。要求用VHDL編程設(shè)計(jì)底層文件,頂層文件可任意(可用原理圖方式或文本方式);完成仿真文件(包括MATLAB和QUARTUSII

2015-09-18 14:54:46

DSPBuilder設(shè)計(jì)了一個(gè)4階FIR濾波器,并用QuartusII進(jìn)行硬件仿真,仿真結(jié)果表明設(shè)計(jì)FIR濾波器的正確性。同時(shí)使用IPCore開發(fā)基于FPGA的FIR數(shù)字濾波器,利用現(xiàn)有的IPCore在FPGA器件上實(shí)現(xiàn)濾波器設(shè)計(jì)。

2012-08-11 15:32:34

源碼-基于FPGA設(shè)計(jì)的插值濾波器設(shè)計(jì).rar (12.14 KB )

2019-05-08 06:35:28

綜合Matlab語言的結(jié)構(gòu)特點(diǎn),提高硬件使用效率的途徑等設(shè)計(jì)細(xì)節(jié),得到了設(shè)計(jì)代碼和仿真結(jié)果.設(shè)計(jì)經(jīng)過硬件時(shí)序仿真驗(yàn)證,可以在FPGA中直接實(shí)現(xiàn).仿真結(jié)果說明,NLMS濾波器對(duì)于音頻信號(hào)有很好的收斂特性

2010-04-24 09:01:12

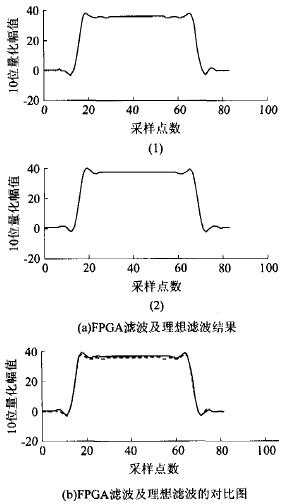

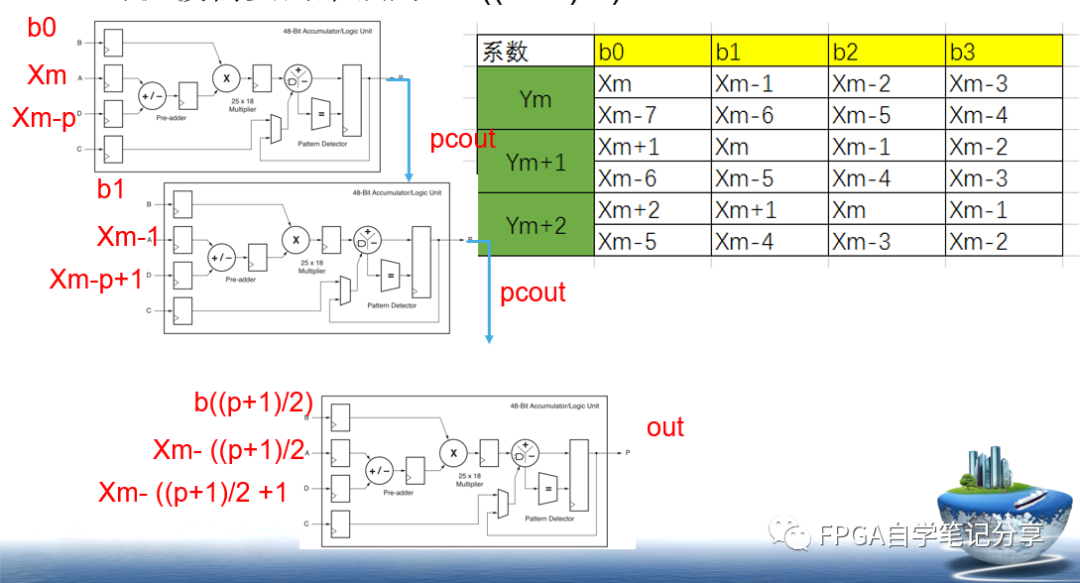

今天和大俠簡(jiǎn)單聊一聊基于matlab FPGA verilog的FIR濾波器設(shè)計(jì),話不多說,上貨。

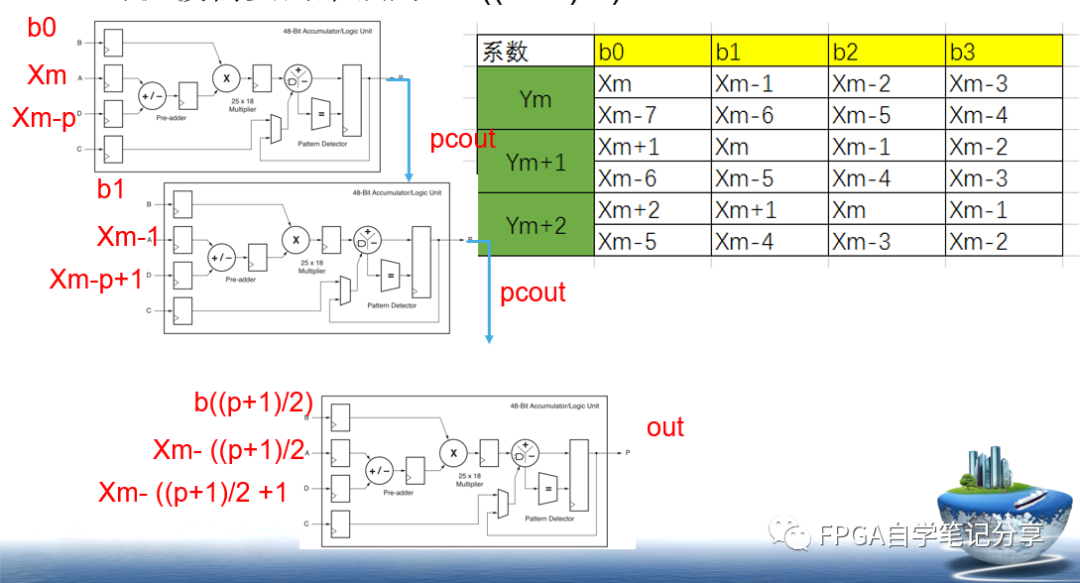

本次設(shè)計(jì)實(shí)現(xiàn)8階濾波器,9個(gè)系數(shù),由于系數(shù)的對(duì)稱性,h(0)=h(8),h1(1)=h(7

2024-07-04 20:11:05

濾波器在FPGA中的實(shí)現(xiàn)用FPGA來實(shí)現(xiàn)濾波器的設(shè)計(jì)優(yōu)點(diǎn)用FPGA來設(shè)計(jì)濾波器,不但設(shè)計(jì)簡(jiǎn)單,而且成本小,可靠性好。且無需像傳統(tǒng)的設(shè)計(jì)芯片一樣進(jìn)行測(cè)試。主要優(yōu)點(diǎn):設(shè)計(jì)簡(jiǎn)潔。若設(shè)計(jì)有誤,則只需

2021-07-30 07:03:10

實(shí)現(xiàn)FPGA數(shù)字下變頻的多類濾波器分組級(jí)聯(lián)技術(shù)分析1 引 言 本文針對(duì)以下高效算法做了總結(jié),進(jìn)行合理的分組級(jí)聯(lián)并引入流水線技術(shù)以便于在FPGA上實(shí)現(xiàn)。數(shù)字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

目前FIR濾波器的硬件實(shí)現(xiàn)的方式有哪幾種?怎么在FPGA上實(shí)現(xiàn)FIR濾波器的設(shè)計(jì)?

2021-05-07 06:03:13

分方程如下所示:由差分方程可知IIR濾波器存在反饋,因此在FPGA設(shè)計(jì)時(shí)要考慮到有限字長(zhǎng)效應(yīng)帶來的影響。差分方程中包括兩個(gè)部分:輸入信號(hào)x(n)的M節(jié)延時(shí)網(wǎng)絡(luò),相當(dāng)于FIR的網(wǎng)絡(luò)結(jié)構(gòu),實(shí)現(xiàn)系統(tǒng)的零點(diǎn)

2020-09-27 09:22:58

HZ的正弦波疊加而成,要求將信號(hào)通過FPGA濾波后的用modelsim仿真,并在matlab中驗(yàn)證濾波器的正確性很多朋友一看,這是嘛呀?即使當(dāng)時(shí)數(shù)字信號(hào)處理學(xué)的還算可以,但是真正到工程中就傻了眼了,好吧

2015-06-16 19:25:35

。對(duì)于這種情況,我們利用Artix-7 FPGA 中現(xiàn)有的16GTP 收發(fā)器設(shè)計(jì)出采用DDC的八ADC結(jié)構(gòu)(圖2)。這樣能更高效使用賽靈思FPGA資源,成為一組FDM通道的多通道數(shù)字接收器。DDC濾波器

2019-06-14 05:00:09

詳細(xì)討論了IIR數(shù)字濾波器從MATLAB設(shè)計(jì)到FPGA實(shí)現(xiàn)的整個(gè)過程,提出了用遞推算法解決實(shí)現(xiàn)過程中一些關(guān)鍵問題的方法,并在modelsim上進(jìn)行了仿真袁最終在以Xilinx公司的FPGA芯片為核心

2009-03-07 10:09:14 7

7 軟件無線電中的多速率信號(hào)處理.介紹r級(jí)聯(lián)積分梳狀濾波器的基本組成及設(shè)計(jì)原理,給出了基于FPGA 的具體設(shè)計(jì)方案及實(shí)現(xiàn)方法。仿真結(jié)果表明,該設(shè)計(jì)簡(jiǎn)單合理,使用靈活方便,

2009-07-07 14:38:30 32

32 根據(jù)超窄帶調(diào)制的原理詳細(xì)分析了超窄帶濾波器的要求,并使用傳統(tǒng)的數(shù)字濾波器設(shè)計(jì)進(jìn)行了仿真,仿真結(jié)果得出傳統(tǒng)的FIR 或IIR 結(jié)構(gòu)是不可能完成超窄帶濾波的。而晶體由于具

2009-08-15 10:52:16 37

37 本文提出了一種采用現(xiàn)場(chǎng)可編程門陣列器件 FPGA 實(shí)現(xiàn)FIR 字濾波器硬件電路的方案,該方案基于只讀存儲(chǔ)器ROM 查找表的分布式算法。并以一個(gè)十六階低通FIR 數(shù)字濾波電路在ALTERA 公

2009-08-31 16:47:47 45

45 探討了DDC中抽取濾波系統(tǒng)的設(shè)計(jì)方法和基于DSP Builder的具體實(shí)現(xiàn)方案,采用CIC濾波器、HB濾波器、FIR濾波器三級(jí)級(jí)聯(lián)的方式來降低采樣率,并進(jìn)行了模型仿真,結(jié)果表明設(shè)計(jì)是可行的

2009-09-17 11:35:08 23

23 基于FPGA對(duì)稱型FIR濾波器的設(shè)計(jì)與實(shí)現(xiàn):在基于FPGA的對(duì)稱型FIR數(shù)字濾波器設(shè)計(jì)中,為了提高速度和運(yùn)行效率,提出了使用線性I相位結(jié)構(gòu)和加法樹乘法器的方法,并利用Altera公I(xiàn)司的FPG

2009-09-25 15:38:38 30

30 本文詳細(xì)討論了利用新版本FPGA 輔助設(shè)計(jì)軟件QuartusII6.0 中提供的浮點(diǎn)運(yùn)算功能模塊實(shí)現(xiàn)IIR 濾波器的方法,與采用FPGA 的乘法模塊的同類設(shè)計(jì)相比,此濾波器設(shè)計(jì)結(jié)構(gòu)簡(jiǎn)單,容易擴(kuò)

2009-12-19 15:44:27 38

38 數(shù)字濾波器在FPGA中的實(shí)現(xiàn)

2010-02-09 10:21:27 77

77 設(shè)計(jì)一個(gè)由現(xiàn)場(chǎng)可編程門陣列(FPGA)控制的濾波器。該濾波器主要由3個(gè)模塊組成:前置放大、濾波電路、FPGA顯示與控制電路等利用FPGA作為放大器及程控濾波器電路中繼電器組的控制模

2010-07-17 18:00:09 45

45 利用matlab里面的simulink 工具箱進(jìn)行濾波器的設(shè)計(jì)和仿真

2010-11-01 11:42:06 302

302 matlab濾波器設(shè)計(jì)-IIR濾波器的設(shè)計(jì)與仿真

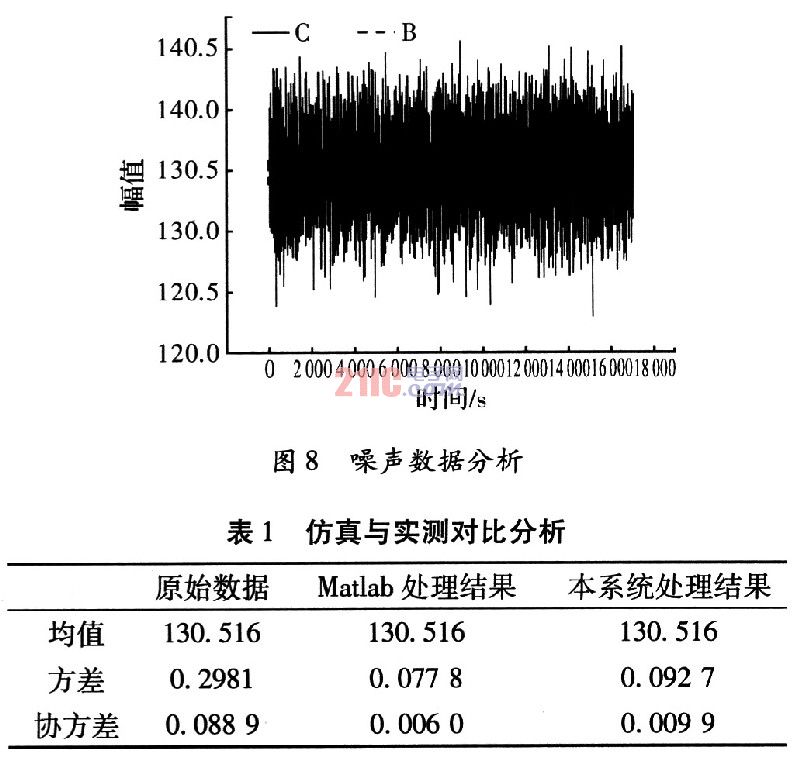

1 引言 在現(xiàn)代通信系統(tǒng)中,由于信號(hào)中經(jīng)常混有各種復(fù)雜成分,所以很多信號(hào)的處理和分析

2008-01-16 09:51:28 5948

5948

高效FIR濾波器的設(shè)計(jì)與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(yīng)(FIR)數(shù)字濾波器理論及常見實(shí)現(xiàn)方法的基礎(chǔ)上,提出了一種基于FPGA的高效實(shí)現(xiàn)方案。

2008-01-16 09:56:02 2060

2060

如何用用FPGA實(shí)現(xiàn)FIR濾波器

你接到要求用FPGA實(shí)現(xiàn)FIR濾波器的任務(wù)時(shí),也許會(huì)想起在學(xué)校里所學(xué)的FIR基礎(chǔ)知識(shí),但是下一步該做什么呢?哪些參數(shù)是重

2009-03-30 12:25:45 4905

4905

典型濾波器的SystemView設(shè)計(jì)與仿真

通信技術(shù)的飛速發(fā)展使得通信系統(tǒng)日趨復(fù)雜,通信系統(tǒng)設(shè)計(jì)的EDA技術(shù)在研發(fā)階段實(shí)現(xiàn)軟件仿真已成為時(shí)尚。文章介紹了通信仿真軟件Sys

2009-06-16 08:35:01 5466

5466 摘要: 針對(duì)在FPGA中實(shí)現(xiàn)FIR濾波器的關(guān)鍵--乘法運(yùn)算的高效實(shí)現(xiàn)進(jìn)行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設(shè)計(jì)了FIR濾波器。通過FPGA仿零點(diǎn)驗(yàn)證

2009-06-20 14:09:36 1050

1050

基于DSP的并聯(lián)電力有源濾波器的仿真研究

1引言

近十年來,隨著電力電子技術(shù)的飛速發(fā)展,電力有源濾波器(簡(jiǎn)

2009-07-10 09:39:12 950

950

FIR帶通濾波器的FPGA實(shí)現(xiàn)

引 言??? 在FPGA應(yīng)用中,比較廣泛而基礎(chǔ)的就是數(shù)字濾波器。根據(jù)其單位沖激響應(yīng)函數(shù)的時(shí)域特性可分為無限沖擊響應(yīng)(Infinite

2009-11-13 09:55:18 7499

7499

LMS自適應(yīng)濾波器的仿真與實(shí)現(xiàn)

0 引言

自適應(yīng)濾波器可廣泛應(yīng)用于系統(tǒng)識(shí)別、信號(hào)處理和數(shù)字通信等許多領(lǐng)域。而超大規(guī)模集成電路和FPGA的飛速發(fā)展,也促

2009-12-16 10:41:56 9300

9300 基于FPGA的數(shù)字濾波器的設(shè)計(jì)與實(shí)現(xiàn)

在信息信號(hào)處理過程中,如對(duì)信號(hào)的過濾、檢測(cè)、預(yù)測(cè)等,都要使用到濾波器,數(shù)字濾波器是數(shù)字信號(hào)處理中使用最廣泛的一

2010-01-07 10:45:35 4082

4082

FPGA的Kalman濾波器的設(shè)計(jì)

摘要:針對(duì)電路設(shè)計(jì)中經(jīng)常碰到數(shù)據(jù)的噪聲干擾現(xiàn)象,提出了一種Kalman濾波的FPGA實(shí)現(xiàn)方法。該方法采用了TI公司的高精度模數(shù)轉(zhuǎn)換

2010-04-13 13:32:46 3553

3553

DNLMS濾波器的FPGA設(shè)計(jì)方案

自適應(yīng)濾波算法的研究始于20世紀(jì)50年代末,Widrow和Hoff等人最早提出最小均方算法(LMS)。算法由于結(jié)構(gòu)簡(jiǎn)單,計(jì)算量小,易于實(shí)

2010-05-10 10:06:23 857

857

摘要:橢圓濾波器在各種濾波器中具有其自身獨(dú)特的優(yōu)點(diǎn),但設(shè)計(jì)過程往往比較復(fù)雜.本文 給出了一種簡(jiǎn)易的計(jì)算方法.這種方法需要的初始值數(shù)據(jù)較少,設(shè)計(jì)步驟簡(jiǎn)練,計(jì)算量小.并用 PSPICE仿真軟件分別對(duì)橢圓函數(shù)低通、高通、帶通濾波器進(jìn)行設(shè)計(jì)和仿真分析,仿

2011-01-28 16:04:44 186

186 摘要: 針對(duì)水下目標(biāo)跟蹤定位系統(tǒng)中信號(hào)的特點(diǎn), 采用自適應(yīng)Notch 濾波器對(duì)接收信號(hào)進(jìn)行檢測(cè), 使系統(tǒng)在低信噪 比的情況下仍能保證較高的正確檢測(cè)率。提出了用FPGA 實(shí)現(xiàn)Notch 濾波器的硬件電路方案, 用DDS 技術(shù)解決了 Notch 濾波器的正交參考源的輸入問題, 簡(jiǎn)化

2011-02-17 16:00:14 69

69 摘要:采用了TI公司的TMS320C55XX數(shù)字信號(hào)處理器完成IIR濾波器的設(shè)計(jì),利用MATLAB的濾波器設(shè)計(jì)工具箱(FDATool)來設(shè)計(jì)最小階切比雪夫低通濾波器,并用代碼調(diào)試器(CCS)進(jìn)行軟硬件的調(diào)試和仿真。結(jié)果表明,該濾波器可以有效的濾除干擾信號(hào),且設(shè)計(jì)方法簡(jiǎn)單可靠,具有

2011-02-28 11:09:14 507

507 為補(bǔ)償傳統(tǒng)CIC濾波器的通帶衰減,提出一種改進(jìn)型的CIC抽取濾波器,即在SCIC濾波器之后級(jí)聯(lián)一個(gè)二階多項(xiàng)式內(nèi)插濾波器。基于硬件實(shí)現(xiàn)的要求,給出改進(jìn)型CIC濾波器的FPGA高效實(shí)現(xiàn)原理圖。仿真結(jié)果表明改進(jìn)的CIC濾波器具有更好的通阻帶特性。

2011-03-15 14:06:35 52

52 充分利用有限沖擊響應(yīng)數(shù)字濾波器(Finite Impulse Response digital filter ,F(xiàn)IR)系數(shù)的對(duì)稱特性,借助于MATLAB語言和現(xiàn)場(chǎng)可編程門陣列(FPGA)實(shí)現(xiàn)了一種高效的 低通濾波器 。設(shè)計(jì)過程中通過

2011-08-05 14:23:07 83

83 目前數(shù)字濾波器的硬件實(shí)現(xiàn)方法通常采用專用DSP芯片或FPGA,本文從FIR濾波器的系數(shù)考慮,采用CSD編碼,對(duì)FIR數(shù)字濾波器進(jìn)行優(yōu)化設(shè)計(jì)。

2011-08-16 10:54:41 4210

4210

基于多速率信號(hào)處理原理,設(shè)計(jì)了用于下變頻的CIC抽取濾波器,由于CIC濾波器結(jié)構(gòu)只用到加法器和延遲器,沒有乘法器,很適合用FPGA來實(shí)現(xiàn),所以本文分析了CIC濾波器的原理,性能及影

2011-08-26 15:12:11 162

162 文中設(shè)計(jì)的均衡濾波器充分利用FPGA內(nèi)部資源、時(shí)間換取空間的方法,在EP1C3系列的FPGA內(nèi)實(shí)現(xiàn)1 024階FIR數(shù)字均衡濾波器,并通過重載系數(shù),可實(shí)現(xiàn)多種頻率響應(yīng)的均衡特性、簡(jiǎn)易數(shù)字均衡濾波

2011-10-19 15:23:48 38

38 根據(jù)基帶成型濾波器的工作原理,文中設(shè)計(jì)出了一種基帶成型濾波器的數(shù)字實(shí)現(xiàn)方案。該方案首先運(yùn)用MATALB仿真工具得到信號(hào)基帶成型后的仿真數(shù)據(jù),并將仿真數(shù)據(jù)存儲(chǔ)在FPGA中,然后通

2012-07-30 10:27:22 52

52 數(shù)字濾波器是數(shù)字信號(hào)處理領(lǐng)域內(nèi)的重要組成部分。FIR濾波器又以其嚴(yán)格的線性相位及穩(wěn)定性高等特性被廣泛應(yīng)用。本文結(jié)合MATLAB工具軟件介紹了FIR數(shù)字濾波器的設(shè)計(jì)方法,并在Xilinx的

2012-09-25 11:34:08 120

120 描述了基于FPGA的FIR濾波器設(shè)計(jì)。根據(jù)FIR的原理及嚴(yán)格線性相位濾波器具有偶對(duì)稱的性質(zhì)給出了FIR濾波器的4種結(jié)構(gòu),即直接乘加結(jié)構(gòu)、乘法器復(fù)用結(jié)構(gòu)、乘累加結(jié)構(gòu)、DA算法。在本文中給

2012-11-09 17:32:37 121

121 文中基于多速率數(shù)字信號(hào)處理原理,設(shè)計(jì)了用于數(shù)字下變頻技術(shù)的CIC抽取濾波器。通過分析CIC濾波器的原理及性能參數(shù),利用MATLAB設(shè)計(jì)了符合系統(tǒng)要求的CIC濾波器,并通過FPGA實(shí)現(xiàn)了CI

2013-04-15 19:29:28 71

71 基于matlab和fpga的FIR濾波器設(shè)計(jì),有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-27 15:51:58 59

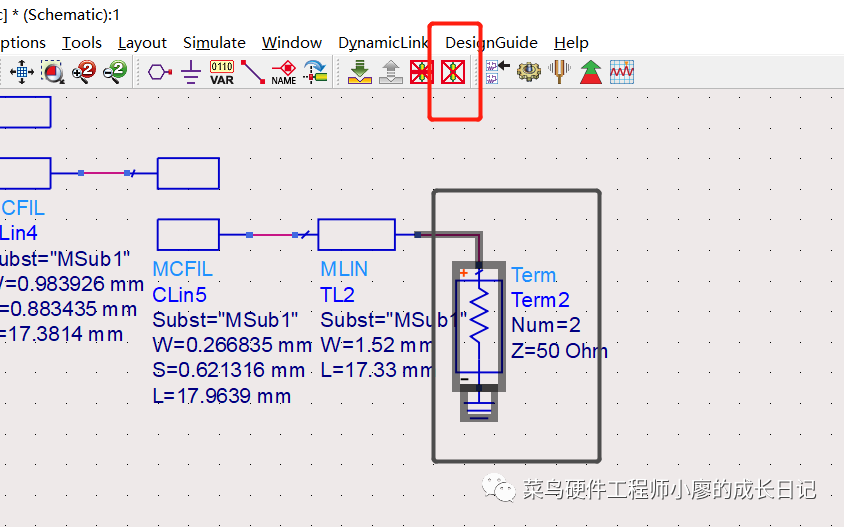

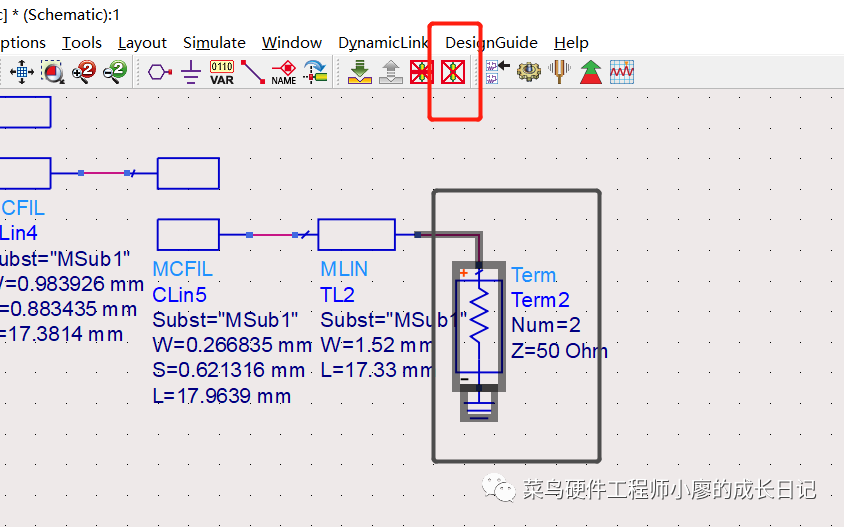

59 基于ADS射頻微帶低通濾波器仿真設(shè)計(jì),有興趣的同學(xué)可以下載學(xué)習(xí)

2016-05-04 15:11:28 88

88 基于FPGA的FIR濾波器設(shè)計(jì)與實(shí)現(xiàn),下來看看

2016-05-10 11:49:02 39

39 基于Simulink的FIR數(shù)字濾波器的仿真。

2016-05-17 09:49:51 1

1 濾波器基于Simulink的數(shù)字濾波器的仿真。

2016-05-17 09:49:51 21

21 matlab設(shè)計(jì)iir濾波器,iir實(shí)現(xiàn)和濾波后結(jié)果以及matlab和fpga聯(lián)調(diào),fpga的verilog源代碼,testbeach實(shí)現(xiàn)。

2016-12-12 20:39:53 56

56 自動(dòng)設(shè)計(jì)仿真濾波器軟件

2017-03-01 12:00:05 23

23 提高時(shí)延精度,有效彌補(bǔ)時(shí)延誤差導(dǎo)致的圖像尾影;其次在FPGA中實(shí)現(xiàn)了該濾波器功能,時(shí)序仿真結(jié)果說明FPGA實(shí)現(xiàn)結(jié)果與理論分析一致,可用于實(shí)際工程實(shí)踐。

2017-11-08 16:58:44 37

37 研究了一種采用FPGA實(shí)現(xiàn)32階FIR濾波器硬件電路方案;討論了窗函數(shù)的選擇、濾波器的結(jié)構(gòu)以及系數(shù)量化問題;研究了FIR濾波器的FPGA實(shí)現(xiàn),各模塊的設(shè)計(jì)以及如何優(yōu)化硬件資源,提高運(yùn)行速度等

2017-11-10 16:41:57 16

16 ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上實(shí)現(xiàn)了一種下采樣率為64的抽取濾波器。Modelsim仿真結(jié)果表明,該抽取濾波器設(shè)計(jì)是有效的,達(dá)到了設(shè)計(jì)指標(biāo)。

2017-11-17 09:01:55 6492

6492 摘要:有限沖擊響應(yīng)(FIR)濾波器是數(shù)字通信系統(tǒng)中常用的基本模塊。文章設(shè)計(jì)了一種流水結(jié)構(gòu)的FIR濾波器,通過FPGA對(duì)其進(jìn)行硬什加速控制。仿真結(jié)果驗(yàn)證了所設(shè)計(jì)的FIR流水結(jié)構(gòu)濾波器功能的正確性

2017-11-18 06:15:02 2101

2101

對(duì)一種單圖像向?qū)?b class="flag-6" style="color: red">濾波器的高性能FPGA設(shè)計(jì)結(jié)構(gòu)進(jìn)行了分析,發(fā)現(xiàn)其中的均值濾波器存在設(shè)計(jì)缺陷,據(jù)此提出了一種向?qū)?b class="flag-6" style="color: red">濾波器的整數(shù)FPGA設(shè)計(jì)結(jié)構(gòu)。通過改變均值濾波器的數(shù)據(jù)累加順序,減少了存儲(chǔ)資源

2017-11-22 15:43:12 12

12 為了掌握微波濾波器的制作原理及設(shè)計(jì)方法,實(shí)現(xiàn)一種UHF波段帶通濾波器的設(shè)計(jì)和制作。該設(shè)計(jì)采用了既定指標(biāo)確定濾波器的形式(橢圓函數(shù)LC帶通濾波器),以橢圓函數(shù)為理論基礎(chǔ),通過軟件仿真、版圖制作、加工

2017-12-06 11:15:01 3523

3523

文介紹了FIR抽取濾波器的工作原理,重點(diǎn)闡述了用XC2V1000實(shí)現(xiàn)FIR抽取濾波器的方法,并給出了仿真波形和設(shè)計(jì)特點(diǎn)。

2018-04-19 11:34:00 2750

2750

要設(shè)計(jì)一個(gè)濾波器,首先要分析濾波器的技術(shù)指標(biāo),選擇合適的濾波器形式,確定濾波器的級(jí)數(shù),分析濾波器的帶外特性以及通帶特性,估算濾波器中心衰減和帶外 抑制的大小,對(duì)濾波器進(jìn)行合理的設(shè)計(jì)與計(jì)算,最后要對(duì)濾波器進(jìn)行仿真優(yōu)化,直至達(dá)到滿意的技術(shù)指標(biāo)。

2018-02-08 19:30:06 13116

13116

用FPGA實(shí)現(xiàn)抽取濾波器比較復(fù)雜,主要是因?yàn)樵?b class="flag-6" style="color: red">FPGA中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu),現(xiàn)在,FPGA中集成了硬件乘法器,使FPGA在數(shù)字信號(hào)處理方面有了長(zhǎng)足的進(jìn)步。本文介紹了一種采用Xilinx公司的XC2V1000實(shí)現(xiàn)FIR抽取濾波器的設(shè)計(jì)方法。

2018-04-28 11:50:00 1620

1620

本文檔內(nèi)容介紹了基于IIR數(shù)字濾波器的FPGA實(shí)現(xiàn),供參考

2018-03-02 13:45:19 36

36 基于靈活自適應(yīng)的空口波形技術(shù)FOFDM(Filtered OFDM)是現(xiàn)代通信技術(shù)的研究熱點(diǎn),設(shè)計(jì)并實(shí)現(xiàn)可調(diào)FIR濾波器是實(shí)現(xiàn)該技術(shù)的核心工作之一。本文設(shè)計(jì)的基于FPGA的可調(diào)節(jié)FIR濾波器系數(shù)

2018-07-23 17:21:00 3003

3003

本文檔的主要內(nèi)容詳細(xì)介紹的是有源濾波器的仿真詳細(xì)資料免費(fèi)下載主要內(nèi)容包括了:帶通有源濾波器,帶阻有源濾波器,低通有源濾波器,一階高通有源濾波器Multisim 14軟件進(jìn)行的仿真。

2018-10-29 08:00:00 71

71 用FPGA實(shí)現(xiàn)抽取濾波器比較復(fù)雜,主要是因?yàn)樵?b class="flag-6" style="color: red">FPGA中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu),現(xiàn)在,FPGA中集成了硬件乘法器,使FPGA在數(shù)字信號(hào)處理方面有了長(zhǎng)足的進(jìn)步。本文介紹了一種采用Xilinx公司的XC2V1000實(shí)現(xiàn)FIR抽取濾波器的設(shè)計(jì)方法。

2020-09-25 10:44:00 3

3 數(shù)字濾波器、DSP器件或可編程邏輯器件(如FPGA)實(shí)現(xiàn)。因?yàn)椋?b class="flag-6" style="color: red">FPGA實(shí)現(xiàn)數(shù)字濾波器具有實(shí)時(shí)性強(qiáng)、靈活性高、處理速度快以及小批量生產(chǎn)成本低等優(yōu)點(diǎn),所以得到了較為廣泛的應(yīng)用。本文以巴特沃思數(shù)字帶通濾波器為例,較為詳細(xì)地介紹了其設(shè)計(jì)和實(shí)

2020-08-06 18:50:00 3

3 針對(duì)Σ△ADC輸出端存在的高頻噪聲問題,設(shè)計(jì)了一種 Sinc數(shù)字抽取濾波器,實(shí)現(xiàn)了Σ-△調(diào)制器輸出信號(hào)的高頻濾波。分析了Sinc濾波器的結(jié)構(gòu)原理,基于 Spartan6FPGA進(jìn)行濾波器的設(shè)計(jì)與實(shí)現(xiàn)

2020-08-26 17:12:00 17

17 本文檔的主要內(nèi)容詳細(xì)介紹的是使用DSP設(shè)計(jì)和仿真FIR濾波器包括了:dsp builder profile和基本設(shè)計(jì)流程和fir的設(shè)計(jì)過程及注意事項(xiàng)

2020-09-01 16:02:00 13

13 在視頻圖像獲取過程中“由于噪聲對(duì)圖像序列的降質(zhì)”需要設(shè)計(jì)實(shí)時(shí)噪聲濾波器。討論了視頻圖像的卡爾曼濾波問題及自適應(yīng)卡爾曼濾波算法“并討論了自適應(yīng)卡爾曼濾波算法的簡(jiǎn)化”以利于硬件實(shí)現(xiàn)自適應(yīng)卡爾曼濾波器“并進(jìn)行了簡(jiǎn)化算法仿真”完成基于FPGA實(shí)現(xiàn)的實(shí)時(shí)自適應(yīng)卡爾曼濾波器的設(shè)計(jì)。

2021-01-22 14:29:29 22

22 在視頻圖像獲取過程中“由于噪聲對(duì)圖像序列的降質(zhì)”需要設(shè)計(jì)實(shí)時(shí)噪聲濾波器。討論了視頻圖像的卡爾曼濾波問題及自適應(yīng)卡爾曼濾波算法“并討論了自適應(yīng)卡爾曼濾波算法的簡(jiǎn)化”以利于硬件實(shí)現(xiàn)自適應(yīng)卡爾曼濾波器“并進(jìn)行了簡(jiǎn)化算法仿真”完成基于FPGA實(shí)現(xiàn)的實(shí)時(shí)自適應(yīng)卡爾曼濾波器的設(shè)計(jì)。

2021-01-22 14:29:29 14

14 WCDMA中規(guī)定了小區(qū)搜索的時(shí)隙同步過程采用匹配濾波器的方法實(shí)現(xiàn),本論文主要研究匹配濾波器原理及FPGA實(shí)現(xiàn)結(jié)構(gòu)。

2021-01-26 16:22:43 12

12 提出一種新的高階FIR濾波器的FPGA實(shí)現(xiàn)方法。該方法運(yùn)用多相分解結(jié)構(gòu)對(duì)高階FIR濾波器進(jìn)行降階處理,采用改進(jìn)的分布式算法來實(shí)現(xiàn)降階后的FIR濾波器。設(shè)計(jì)了一系列階數(shù)從8到1 024的FIR濾波器

2021-03-23 15:44:54 31

31 微波濾波器是用來分離不同頻率微波信號(hào)的一種器件。它的主要作用是抑制不需要的信號(hào), 使其不能通過濾波器, 只讓需要的信號(hào)通過。在微波電路系統(tǒng)中,濾波器的性能對(duì)電路的性能指標(biāo)有很大的影響,因此如何設(shè)計(jì)出

2021-06-04 17:12:20 33

33 LMS自適應(yīng)濾波器的MATLAB仿真和DSP實(shí)現(xiàn)

2021-06-09 10:47:14 73

73 基于FPGA的數(shù)字下變頻器(DDC)的設(shè)計(jì)(ups電源技術(shù)轉(zhuǎn)讓)-基于FPGA的數(shù)字下變頻器(DDC)的設(shè)計(jì).適合新手學(xué)習(xí)參考

2021-09-16 11:43:52 37

37 基于FPGA的_ADC數(shù)字抽取濾波器Sinc_3設(shè)計(jì)(現(xiàn)代電源技術(shù)基礎(chǔ)楊飛)-該文檔為基于FPGA的_ADC數(shù)字抽取濾波器Sinc_3設(shè)計(jì)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-16 13:58:04 27

27 有源電力濾波器APF仿真模型

2021-11-13 15:53:17 31

31 本文介紹了設(shè)計(jì)濾波器的FPGA實(shí)現(xiàn)步驟,并結(jié)合杜勇老師的書籍中的串行FIR濾波器部分進(jìn)行一步步實(shí)現(xiàn)硬件設(shè)計(jì),對(duì)書中的架構(gòu)做了簡(jiǎn)單的優(yōu)化,并進(jìn)行了仿真驗(yàn)證。

2023-05-24 10:56:34 1843

1843

本文介紹了設(shè)計(jì)濾波器的FPGA實(shí)現(xiàn)步驟,并結(jié)合杜勇老師的書籍中的并行FIR濾波器部分進(jìn)行一步步實(shí)現(xiàn)硬件設(shè)計(jì),對(duì)書中的架構(gòu)做了復(fù)現(xiàn)以及解讀,并進(jìn)行了仿真驗(yàn)證。

2023-05-24 10:57:36 1825

1825

積分梳狀濾波器(CIC,Cascaded Integrator Comb),一般用于數(shù)字下變頻(DDC)和數(shù)字上變頻(DUC)系統(tǒng)。

2023-06-01 11:05:41 2232

2232

上文 FPGA數(shù)字信號(hào)處理之濾波器2_使用dsp48e1的fir濾波器設(shè)計(jì)完成了結(jié)構(gòu)設(shè)計(jì)。

2023-06-02 12:36:22 2487

2487

完成濾波器的原理圖后,還需要對(duì)濾波器生成版圖進(jìn)一步的仿真驗(yàn)證。首先對(duì)濾波器生產(chǎn)版圖,之后再對(duì)版圖進(jìn)行仿真驗(yàn)證。

2023-06-30 10:38:35 2952

2952

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論