電子發(fā)燒友網(wǎng)核心提示: DRAM控制器藏在您的系統(tǒng)核心芯片系統(tǒng)(SoC)中,可能有兩個(gè),甚至是四個(gè)。有一些精心制作的邏輯小模塊,用于連接SoC內(nèi)部和外部DRAM,它們并沒有引起系統(tǒng)設(shè)計(jì)

2012-10-22 09:53:12 12526

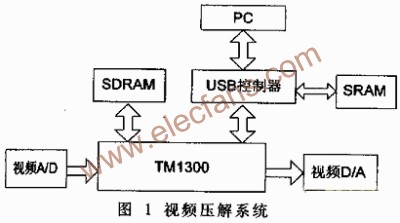

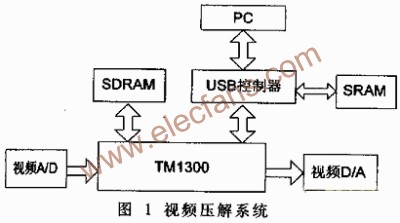

12526 本文針對(duì)高速數(shù)據(jù)傳輸需求,根據(jù)USB2.0的協(xié)議規(guī)范,利用VHDL語言實(shí)現(xiàn)符合該協(xié)議的功能控制器,在視頻壓解系統(tǒng)中使數(shù)據(jù)在PC與外設(shè)之間高速傳輸。

2010-10-28 15:44:03 1499

1499

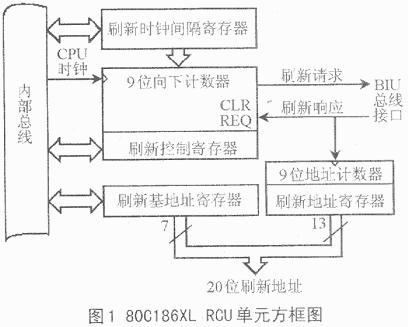

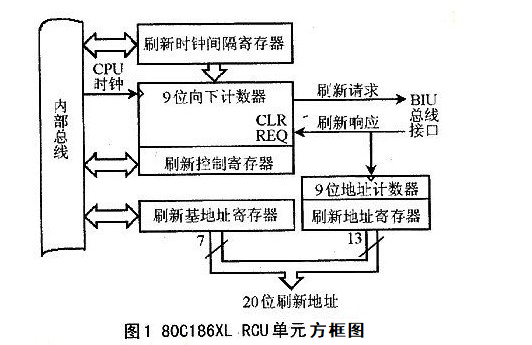

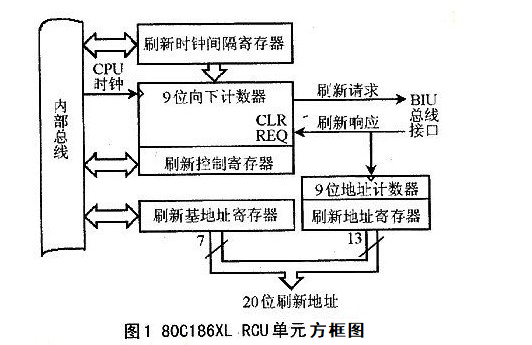

80C186XL16位嵌入式微處理器[1]是Intel公司在嵌入式微處理器市場(chǎng)的上導(dǎo)產(chǎn)品之一,已廣泛應(yīng)用于電腦終端、程控交換和工控等領(lǐng)域。在該嵌入式微處理器片內(nèi),集成有DRAM RCU單元,即DRAM刷新控制單元。

2019-01-07 08:27:00 5220

5220

小,256Kb-16Mb 5.集成度低,單位容量?jī)r(jià)格高 6.靜態(tài)功耗低,運(yùn)行功耗大 DRAM 1.速度較慢 2.需要刷新來保持?jǐn)?shù)據(jù) 3.需要MCU帶外部存儲(chǔ)控制器 4.容量大,16Mb-4Gb 5.集成度高,單位容量?jī)r(jià)格低 6.運(yùn)行功耗低

2020-12-10 15:49:11

BlueNRG-MS設(shè)備,用于天線或測(cè)量?jī)x器的SMA連接器以及用于外部微控制器的SPI連接器。該主板基于STM32L,作為驅(qū)動(dòng)BlueNRG-MS設(shè)備的外部微控制器。 JTAG連接器允許微控制器固件開發(fā)

2020-06-01 17:03:16

DDR_SDRAM控制器的VHDL代碼已經(jīng)測(cè)試

2016-08-24 16:49:35

有誰知道EDK中提供的PPC OPB DDR控制器的VHDL代碼是否可以在任何地方使用?我想在控制器中進(jìn)行一些修改,并在沒有PPC的情況下使用它。

2020-06-02 16:13:50

MAX9930-MAX9933系列RF控制器和檢測(cè)器適用于各種應(yīng)用,其中,通過光纖傳輸有線電視信號(hào)(CATV)是該系列器件非常理想的應(yīng)用之一,利用RF控制器或RF檢測(cè)器控制互阻放大器(TIA)的增益。本文介紹了如何使用MAX9930構(gòu)成RF控制器或檢波器。

2019-08-27 06:35:54

SMBus控制器 Xilinx提供VHDL代碼

2012-08-13 16:20:20

/ml50x_schematics.pdf)(第7頁)中,SystemACE控制器MPU端口連接到賽普拉斯USB控制器GPIO數(shù)據(jù)總線。這種聯(lián)系有什么用?SystemACE控制器的MPU模式可以用于某些USB閃存盤的FPGA配置嗎?謝謝Harshad

2020-05-29 12:28:19

USB接口控制器參考設(shè)計(jì),xilinx提供VHDL代碼

2012-08-15 14:54:06

DRAM控制器方向的時(shí)鐘及由控制器向DRAM方向的時(shí)鐘兩個(gè)系統(tǒng),通過改變讀操作與寫操作時(shí)所利用的時(shí)鐘,實(shí)施時(shí)鐘相位偏移的處理對(duì)策,基本上采用了接近理想的處理方式。 圖的右上

2008-12-04 10:16:36

分析閃存控制器的架構(gòu),首先得了解SSD。一般來說SSD的存儲(chǔ)介質(zhì)分為兩種,一種是采用閃存(Flash芯片)作為存儲(chǔ)介質(zhì),另外一種是采用DRAM作為存儲(chǔ)介質(zhì)。我們通常所說的SSD就是基于閃存的固態(tài)硬盤

2019-09-27 07:12:52

我使用ACE控制器將圖像下載到XC4VLx200中。有兩個(gè)用作DDRII控制器的電源,功率為1.8V。當(dāng)我使用10Mhz用于ACE控制器時(shí),完成信號(hào)變高并且成功。如果我使用20Mhz用于ACE控制器

2020-05-27 14:08:02

分享一款不錯(cuò)的基于VHDL的TP UP-SF微型打印機(jī)控制器設(shè)計(jì)

2021-04-30 06:59:49

80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場(chǎng)的上導(dǎo)產(chǎn)品之一,已廣泛應(yīng)用于電腦終端、程控交換和工控等領(lǐng)域。在該嵌入式微處理器片內(nèi),集成有DRAM RCU單元,即DRAM刷新

2019-11-07 06:01:59

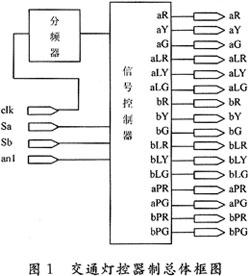

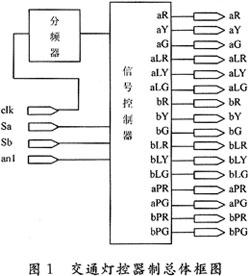

應(yīng)用VHDL語言設(shè)計(jì)數(shù)字系統(tǒng),大部分設(shè)計(jì)工作可在計(jì)算機(jī)上完成,從而縮短系統(tǒng)開發(fā)時(shí)間,提高工作效率。下面介紹基于VHDL設(shè)計(jì)交通燈控制器的一種方案,并給出源程序和仿真結(jié)果。

2019-10-18 07:21:51

為降低設(shè)計(jì)成本,縮短設(shè)計(jì)周期,提出一種基于VHDL的洗衣機(jī)控制器的設(shè)計(jì)方案。

2019-09-30 07:43:39

目前伺服控制器的設(shè)計(jì)多以DSP或MCU為控制核心,但DSP的靈活性不如FPGA,且在某些環(huán)境比較惡劣的條件如高溫高壓下DSP的應(yīng)用效果會(huì)大打折扣,因此以FPGA為控制核心,對(duì)應(yīng)用于機(jī)載三軸伺服控制平臺(tái)的控制器進(jìn)行了設(shè)計(jì)與優(yōu)化。

2019-07-16 07:41:04

用vhdl語言做步進(jìn)電機(jī)的控制器。應(yīng)該如何入手呢?看了很多資料,各有各的思路,越看越混亂,要分成幾個(gè)模塊去做呢? 求大神帶!

2016-04-27 10:21:33

80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場(chǎng)的上導(dǎo)產(chǎn)品之一,已廣泛應(yīng)用于電腦終端、程控交換和工控等領(lǐng)域。在該嵌入式微處理器片內(nèi),集成有DRAMRCU單元,即DRAM刷新控制單元。RCU單元可以自動(dòng)產(chǎn)生DRAM刷新總線周期,它工作于微處理器的增益模式下。

2019-09-25 07:38:04

嗨,我已經(jīng)搜索了很多關(guān)于配置PS DRAM控制器(DDRC)板參數(shù)的信息,鏈接如下,http://www.xilinx.com/support/answers/46778.htm, 我想知道如何獲得包裝長(zhǎng)度?謝謝!

2019-11-07 08:43:39

本文介紹一種基于VHDL設(shè)計(jì)的交通燈控制器方案,并給出源程序和仿真結(jié)果。

2021-04-28 06:54:02

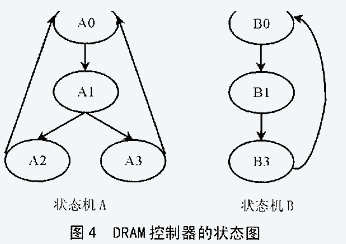

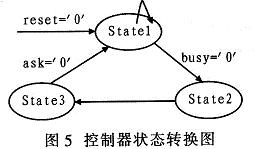

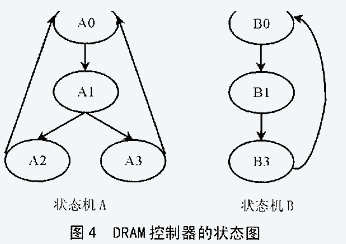

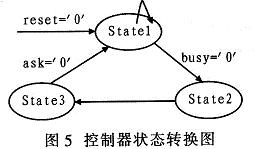

。 關(guān)鍵詞:刷新控制單元(RCU) DRAM控制器 狀態(tài)機(jī) CPLD VHDL語言80C186XL16 位嵌入式微處理器[1]是Intel公司在嵌入式微處理器市場(chǎng)的上導(dǎo)產(chǎn)品之一,已廣泛應(yīng)用于電腦終端

2011-02-24 09:33:15

閃存卡SFCA064GH1AD4TO-I-GS-236-STD嵌入式系統(tǒng)開發(fā)板和套件YSTBS5D3E10DRAM芯片MT53D1024M32D4DT-046微控制器R5F100FCAFP#50閃存卡

2020-09-18 09:13:47

微控制器廣泛應(yīng)用于各種小型電器,隨著技術(shù)的發(fā)展,其不但價(jià)格低廉,而且功能越來越強(qiáng)大。由于家用電器、手持式消費(fèi)電子產(chǎn)品、手持式通信裝置和車用電子等領(lǐng)域的市場(chǎng)推動(dòng),微控制器的使用量越來越大而且表現(xiàn)出

2019-06-25 06:19:25

通過對(duì)傳統(tǒng)MCS-51單片機(jī)指令時(shí)序和體系結(jié)構(gòu)的分析,使用VHDL語言采用自頂向下的設(shè)計(jì)方法重新設(shè)計(jì)了一個(gè)高效的微控制器內(nèi)核。

2021-04-13 06:10:59

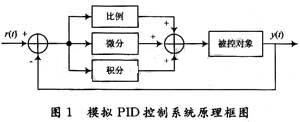

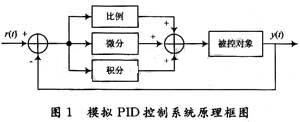

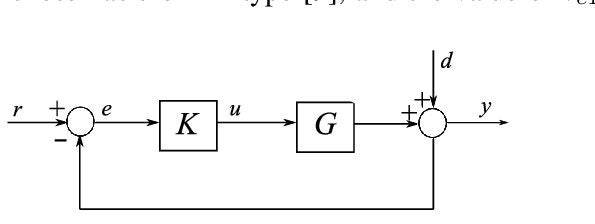

本文介紹VHDL-AMS的新概念和新特性。通過對(duì)PID控制原理進(jìn)行數(shù)學(xué)分析,建立PID控制器的數(shù)學(xué)模型,實(shí)現(xiàn)PID控制器的VHDL-AMS行為級(jí)建模,并進(jìn)行仿真分析。

2021-05-06 07:59:57

本文介紹一種使用硬件描述語言VHDL來實(shí)現(xiàn)基于Petri網(wǎng)的并行控制器的方法。首先使用Petri網(wǎng)對(duì)問題進(jìn)行建模,并對(duì)模型進(jìn)行分析和控制,獲得控制器的Petri網(wǎng)模型;然后用VHDL對(duì)Petri網(wǎng)

2019-08-16 07:52:03

求一個(gè)基于BP神經(jīng)網(wǎng)絡(luò)PID控制器應(yīng)用于雙閉環(huán)直流調(diào)速系統(tǒng)BP_PID控制器學(xué)習(xí)參數(shù)怎么設(shè)置?

2021-10-13 08:10:12

本文介紹了怎樣在嵌入式CPU 80C186XL DRAM刷新控制單元的基礎(chǔ)上,利用CPLD技術(shù)和80C196XL的時(shí)序特征設(shè)計(jì)一個(gè)低價(jià)格、功能完整的DRAM控制器的方法,并采用VHDL語言編程實(shí)現(xiàn)。

2021-04-28 07:10:38

求全彩LED顯示屏控制器的FPGA設(shè)計(jì)的VHDL代碼,不勝感激!!!

2015-11-14 01:57:35

稱重傳感器是稱重,計(jì)量系統(tǒng)中的基礎(chǔ)元件,用于感知重量信息 并將重量信號(hào)轉(zhuǎn)換為 MV 電壓信號(hào), 由控制器或上位機(jī)系統(tǒng)進(jìn)行進(jìn)一 步處理。

2019-11-05 09:02:02

我需要一個(gè)用于無刷直流電機(jī)的位置和速度控制器,帶有霍爾傳感器和 Ethercat(從站)上的正交編碼器。請(qǐng)問有什么關(guān)于 Nucleo 板/控制器/Ethercat 適配器用于原型設(shè)計(jì)的建議嗎?

2023-01-12 07:56:25

和靈活性,可實(shí)時(shí)完成運(yùn)動(dòng)控制過程中復(fù)雜的邏輯處理和控制算法,能實(shí)現(xiàn)多軸高速高精度的伺服控制。本文選用DSP與FPGA作為運(yùn)動(dòng)控制器的核心部件,設(shè)計(jì)了通用型運(yùn)動(dòng)控制器。其中DSP用于運(yùn)動(dòng)軌跡規(guī)劃、速度控制

2019-07-31 08:15:26

SDR SDRAM控制器1?標(biāo)準(zhǔn)SRD SDRAM控制器參考設(shè)計(jì),altera提供 使用手冊(cè) VHDL代碼 Verilog代碼?SDR SDRAM控制器2 標(biāo)準(zhǔn)SRD SDRAM控制器參考設(shè)計(jì),xilinx提供 使用手冊(cè) VHDL代碼Verilog

2008-05-20 10:58:59 155

155 直流步進(jìn)電機(jī)控制器實(shí)例(VHDL源代碼):步進(jìn)電機(jī)控制器.vhd,直流電機(jī)控制器.vhd

2009-05-27 08:51:54 63

63 直流步進(jìn)電機(jī)控制器實(shí)例(VHDL源代碼):

2009-05-27 10:23:05 47

47 介紹了基于VHDL語言設(shè)計(jì)的電梯控制器,并進(jìn)行了電路綜合和仿真。該控制器遵循方向優(yōu)先的控制方式方案,提供 6個(gè)樓層多用戶的載客服務(wù)并指示電梯的運(yùn)行情況。關(guān)鍵詞:

2009-06-09 09:56:40 179

179 傳統(tǒng)交通燈控制器多數(shù)由單片機(jī)或PLC 實(shí)現(xiàn)。本論文介紹一種用FPGA 實(shí)現(xiàn)交通燈控制器的設(shè)計(jì)方法。關(guān)鍵詞:FPGA; VHDL; MAXPLUSll; 交通燈控制器Abstract:Traffic light controller is usually

2009-06-12 11:12:52 90

90

SDRAM控制器參考設(shè)計(jì),Lattice提供的VHDL源代碼

-- Permission:

-- Lattice Semiconductor grants

2009-06-14 08:54:28 93

93 USB接口控制器參考設(shè)計(jì),xilinx提供VHDL代碼 usb xilinx vhdl

;? This program is free software; you can redistribute

2009-06-14 09:05:40 45

45 ZBT SRAM控制器參考設(shè)計(jì),xilinx提供VHDL代碼

Description:? Contains the following files??? readme.txt

2009-06-14 09:22:20 32

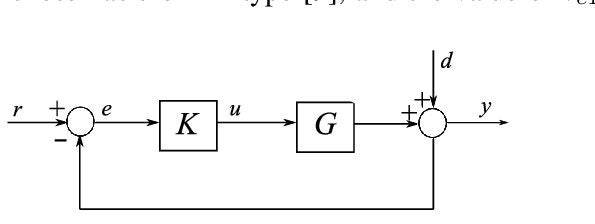

32 通過模糊自整定PID 控制器的設(shè)計(jì),本文提出了一種基于VHDL 描述、DSP Builder 和Modelsim 混合仿真、FPGA實(shí)現(xiàn)的智能控制器設(shè)計(jì)及測(cè)試新方法。首先,通過MATLAB 仿真,得出智能控制器的結(jié)

2009-09-04 09:34:11 17

17 摘要:VHDL設(shè)計(jì)技術(shù)是引起數(shù)字系統(tǒng)設(shè)計(jì)方式發(fā)生突破性變革的技術(shù)。本文論述了使用VHDL設(shè)計(jì)十六路彩燈控制器的過程。VHDL為設(shè)計(jì)提供了更大的靈活性,使程序具有更高的通用性,

2010-05-23 09:36:11 143

143 介紹基于VHDL的微型打印機(jī)控制器的設(shè)計(jì)。論述了微型打印機(jī)的基本原理,以及實(shí)現(xiàn)控制器的VHDL語言設(shè)計(jì)。打印機(jī)的數(shù)據(jù)來自系統(tǒng)中的存儲(chǔ)模塊,根據(jù)需要控制打印。該微型打印機(jī)控

2010-12-23 16:44:19 60

60

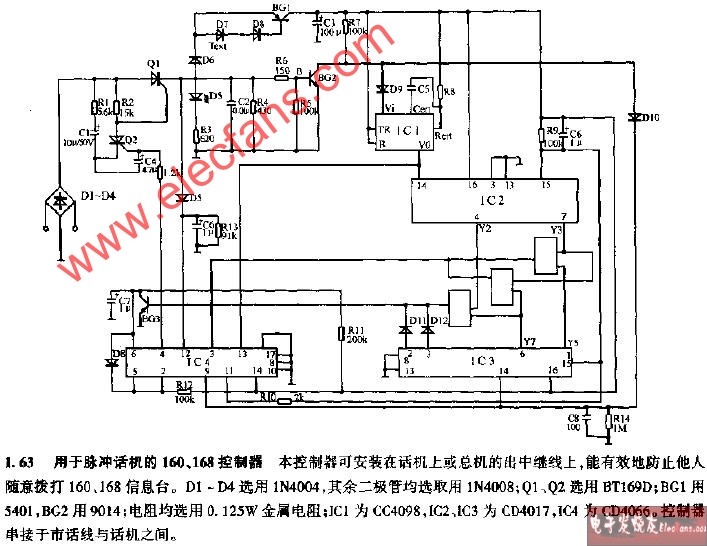

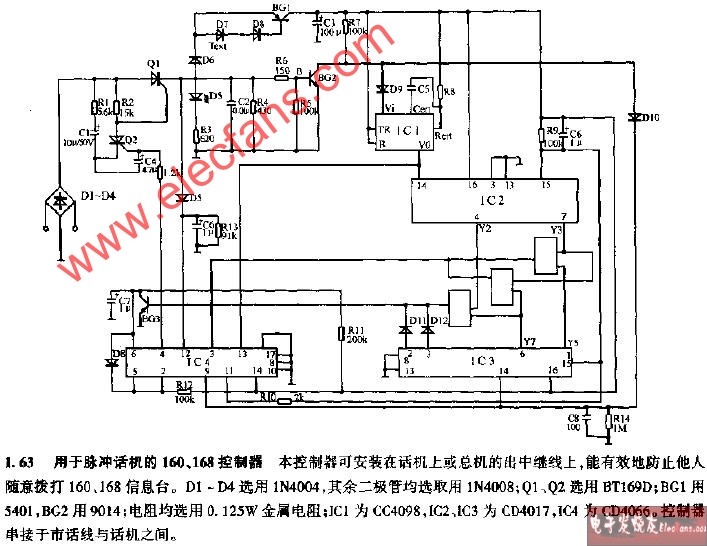

用于脈沖話機(jī)的160,168控制器

2009-03-04 21:19:11 861

861

摘要: 介紹了SDRAM的存儲(chǔ)體結(jié)構(gòu)、主要控制時(shí)序和基本操作命令,并且結(jié)合實(shí)際系統(tǒng),給出了一種用FPGA實(shí)現(xiàn)的通用SDRAM控制器的方案。

關(guān)鍵詞:

2009-06-20 12:51:58 1027

1027

摘要:介紹了一種用VHDL設(shè)計(jì)USB2.0功能控制器的方法,詳術(shù)了其原理和設(shè)計(jì)思想,并在FPGA上予以實(shí)現(xiàn)。

關(guān)鍵詞:USB VHDL FPGA

在視

2009-06-20 13:26:46 1910

1910

摘要:介紹了基于FPGA的圖形式LCD&VGA控制器的設(shè)計(jì),詳細(xì)討論了用VHDL設(shè)計(jì)行場(chǎng)掃描時(shí)序的方法,這種設(shè)計(jì)方法稍作改動(dòng)便可產(chǎn)生任意行場(chǎng)掃描時(shí)序,具有很好的可重用性。

2009-06-20 13:28:05 1686

1686

基于當(dāng)代DRAM結(jié)構(gòu)的存儲(chǔ)器控制器設(shè)計(jì)

1、引言

當(dāng)代計(jì)算機(jī)系統(tǒng)越來越受存儲(chǔ)性能的限制。處理器性能每年以60%的速率增長(zhǎng),存儲(chǔ)器芯片每年僅僅增加10%的

2009-12-31 10:57:03 1028

1028

嵌入式系統(tǒng)中DRAM控制器的CPLD解決方案

80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場(chǎng)的上導(dǎo)產(chǎn)品之一,已廣泛應(yīng)用于電腦終端、程控交換和工控等領(lǐng)域。

2010-01-26 17:25:28 877

877

VHDL設(shè)計(jì)的微型打印機(jī)控制器技術(shù)

1 引言

VHDL是一種面向設(shè)計(jì)、多層次的數(shù)字系

2010-05-04 19:46:45 1231

1231

本文提出一種新穎的解決方案:利用80C186XL的時(shí)序特征,采用CPLD技術(shù),并使用VHDL語言設(shè)計(jì)實(shí)現(xiàn)DRAM控制器。

2012-02-02 11:29:58 1863

1863

應(yīng)用VHDL語言設(shè)計(jì)數(shù)字系統(tǒng),大部分設(shè)計(jì)工作可在計(jì)算機(jī)上完成,從而縮短系統(tǒng)開發(fā)時(shí)間,提高工作效率。下面介紹基于VHDL設(shè)計(jì)交通燈控制器的一種方案,并給出源程序和仿真結(jié)果。

2012-05-22 16:33:30 6271

6271

基于PLD和AHDL的交通燈控制器設(shè)計(jì). 基于VHDL設(shè)計(jì)交通燈控制器,外圍電路少、功耗低、可靠性高,便于系統(tǒng)功能的修改,設(shè)計(jì)效率高。

2016-01-08 16:21:00 27

27 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設(shè)計(jì)VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:FM收音機(jī)的解碼及控制器VHDL語言實(shí)現(xiàn)

2016-06-07 14:13:43 11

11 Xilinx FPGA工程例子源碼:USB接口控制器參考設(shè)計(jì)VHDL代碼(Xilinx)

2016-06-07 14:54:57 21

21 Xilinx FPGA工程例子源碼:Xilinx 的用于設(shè)計(jì)SMBus控制器的源程序

2016-06-07 15:07:45 16

16 Xilinx FPGA工程例子源碼:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

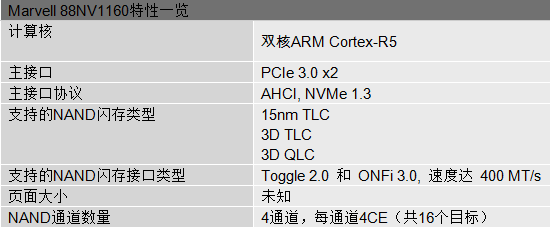

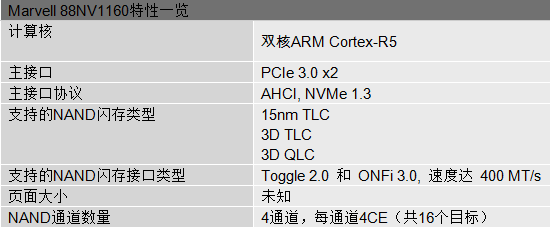

12 Marvell最近推出了一款全新的低成本小尺寸SSD控制器88NV1160,該芯片可用于設(shè)計(jì)以M.2和BGA封裝的小尺寸SSD。88NV1160支持當(dāng)今和未來各種類型的NAND閃存,LDPC糾錯(cuò)功能,NVMe協(xié)議和當(dāng)今SSD控制器的其他各種特性,無需外部DRAM緩存,因此可減少未來SSD的BOM成本。

2016-09-26 15:30:21 2497

2497

8位單片機(jī)與以太網(wǎng)控制器RTL8029接口的VHDL設(shè)計(jì)

2017-01-14 14:42:27 18

18 基于VHDL的SDRAM控制器的實(shí)現(xiàn)

2017-01-22 13:43:27 12

12 DDR 控制器部產(chǎn)品營(yíng)銷總監(jiān) 概述 DDR DRAM內(nèi)存控制器要滿足眾多市場(chǎng)競(jìng)爭(zhēng)的需求。一款出色的內(nèi)存控制器必須能夠增加存儲(chǔ)器接口的帶寬,滿足CPU、圖形處理、系統(tǒng)實(shí)時(shí)DRAM的延遲需求,同時(shí)符合

2017-11-18 18:23:12 3509

3509 本文介紹VHDL-AMS的新概念和新特性。通過對(duì)PID控制原理進(jìn)行數(shù)學(xué)分析,建立PID控制器的數(shù)學(xué)模型,實(shí)現(xiàn)PID控制器的VHDL-AMS行為級(jí)建模,并進(jìn)行仿真分析。

2018-11-14 08:03:00 4304

4304

應(yīng)用VHDL語言設(shè)計(jì)數(shù)字系統(tǒng),大部分設(shè)計(jì)工作可在計(jì)算機(jī)上完成,從而縮短系統(tǒng)開發(fā)時(shí)間,提高工作效率。下面介紹基于VHDL設(shè)計(jì)交通燈控制器的一種方案,并給出源程序和仿真結(jié)果。

2018-11-14 10:59:00 5822

5822

Petri網(wǎng)是離散事件系統(tǒng)建模的重要工具,本文使用硬件描述語言VHDL實(shí)現(xiàn)了基于Petri網(wǎng)的并行控制器。文中通過一個(gè)液位控制系統(tǒng)實(shí)例具體介紹了這一方法,并通過仿真波形證明了該方法的正確性。這對(duì)于離散事件系統(tǒng)并行控制器的設(shè)計(jì)具有十分重要的意義。

2019-04-22 08:10:00 2495

2495

首先應(yīng)進(jìn)行系統(tǒng)模塊的劃分,規(guī)定每一個(gè)模塊的功能以及各模塊之間的接口,最終設(shè)計(jì)方案分為三大模塊:16路花樣彩燈控制器、四頻率輸出分頻器、四選一控制器。四選一控制器從分頻器中選擇不同頻率的時(shí)鐘信號(hào)輸送到彩燈花樣控制器,從而達(dá)到控制彩燈閃爍速度的快慢和花型的的變換。

2018-10-07 12:06:06 6114

6114

觸覺反饋公司Immersion Corp與索尼簽署協(xié)議,將“先進(jìn)觸覺”專利組合授權(quán)給索尼。該公司表示,索尼可以將這一技術(shù)引用于“游戲控制器和VR控制器”。

2019-05-21 16:58:18 1161

1161 項(xiàng)目開始時(shí)我的總體項(xiàng)目功能符合我的預(yù)期,因此我對(duì)結(jié)果感到滿意。感謝您抽出寶貴的時(shí)間閱讀我在VHDL中開發(fā)PID控制器的嘗試。

2019-10-15 09:40:10 4090

4090

利用 VHDL 硬件描述語言在 FPGA 中設(shè)計(jì)直流伺服電機(jī)控制器。其含 4 路 PWM 控制器,每個(gè)控制器均分配一個(gè) ID,當(dāng)?shù)刂肪€ Address 選中某個(gè) ID 時(shí),表明對(duì)該 PWM 控制器

2020-05-11 08:00:00 14

14 VHDL語言由于其其強(qiáng)大的行為描述能力及與硬件行為無關(guān)的特性,被廣泛的用于數(shù)字系統(tǒng)設(shè)計(jì),實(shí)現(xiàn)了硬件電路設(shè)計(jì)的軟件化,成為實(shí)現(xiàn)Petri網(wǎng)邏輯控制器的有力的工具。用VHDL語言進(jìn)行數(shù)字電路設(shè)計(jì)的很大

2020-09-22 20:46:51 1259

1259

DRAM作為PC必備器件之一,大家自然對(duì)DRAM較為熟悉。但是,大家知道DRAM存儲(chǔ)具有哪些分類嗎?大家了解DRAM控制器是如何設(shè)計(jì)出來的嗎?如果你對(duì)DRAM以及本文即將要闡述的內(nèi)容具有興趣,不妨繼續(xù)往下閱讀哦。

2020-10-31 11:51:19 4799

4799

本文檔的主要內(nèi)容詳細(xì)介紹的是電梯控制器的VHDL程序與仿真資料合集免費(fèi)下載。

2021-01-20 13:44:11 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL TFT LCD屏控制器的MCU程序免費(fèi)下載。

2021-01-20 17:03:50 14

14 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL TFT LCD屏控制器的CPLD程序免費(fèi)下載。

2021-01-20 17:03:49 5

5 電子發(fā)燒友網(wǎng)站提供《用于豐田VISTA的LED控制器.zip》資料免費(fèi)下載

2022-08-01 09:51:31 0

0 電子發(fā)燒友網(wǎng)站提供《適用于PC和Android的Arduino游戲控制器.zip》資料免費(fèi)下載

2022-10-31 10:44:41 0

0 用于無刷電機(jī)控制器設(shè)計(jì)的兩芯片解決方案

2022-11-15 19:18:25 8

8 Petri網(wǎng)是離散事件系統(tǒng)建模的重要工具,本文使用硬件描述語言VHDL實(shí)現(xiàn)了基于Petri網(wǎng)的并行控制器。文中通過一個(gè)液位控制系統(tǒng)實(shí)例具體介紹了這一方法,并通過仿真波形證明了該方法的正確性。這對(duì)于離散事件系統(tǒng)并行控制器的設(shè)計(jì)具有十分重要的意義。

2023-08-03 15:33:38 1077

1077

首先拋出重點(diǎn):使用Xilinx的平臺(tái),最大的難點(diǎn)在于,要自己設(shè)計(jì)一個(gè)Flash讀寫控制器。

2023-08-03 09:34:19 1931

1931

電子發(fā)燒友網(wǎng)站提供《基于VHDL的洗衣機(jī)控制器的設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-07 10:28:58 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論