什么是FPGA原型?? FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能

2022-07-19 16:27:29 2400

2400 位流驗證,對于芯片研發(fā)是一個非常重要的測試手段,對于純軟件開發(fā)人員,最難理解的就是位流驗證。在FPGA芯片研發(fā)中,位流驗證是在做什么,在哪些階段需要做位流驗證,如何做?都是問題。

2025-04-25 09:42:51 2204

2204

FPGA Editor數(shù)字設(shè)計工具怎么樣?FPGA Editor如何幫助你完成設(shè)計調(diào)試和驗證?

2021-05-07 06:17:23

(06)FPGA資源評估1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA資源評估5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable Gate

2022-02-23 06:31:32

/sinat_41653350/article/details/105736117---這個里面有FPGA硬件資源介紹。FPGA簡介 FPGA(Field-Programmable Gate Array), 即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物。它是作為專用集成..

2021-07-26 07:09:37

各位大佬,我想問一下怎么用FPGA驗證偽隨機數(shù)發(fā)生器呀,都有哪些步驟呀,有知道了回答一下,謝謝了

2018-11-29 19:56:52

幾個不錯的資料哦,給大家共享下《FPGA系統(tǒng)設(shè)計的主要思路和方法初探》.pdf (766.25 KB )FPGA驗證簡介.pdf (255.69 KB )FPGA經(jīng)驗總結(jié)(精華).doc (1.03

2019-05-27 02:11:57

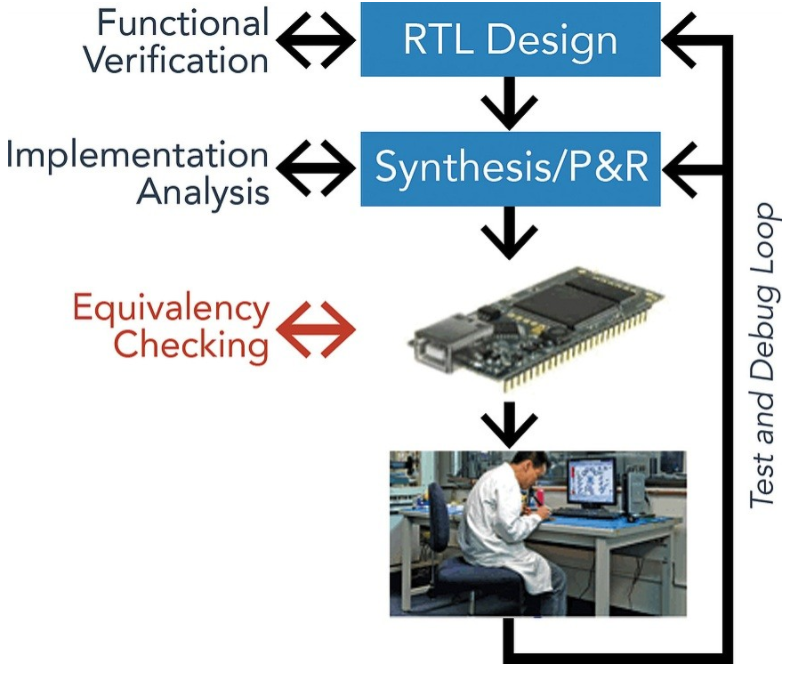

FPGA原型驗證已是當前原型驗證的主流且成熟的芯片驗證方法——它通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證ASIC的功能,并在芯片的基本功能驗證通過后就可以開始驅(qū)動的開發(fā),一直到芯片

2020-08-21 05:00:12

FPGA基本原理及設(shè)計思想和驗證方法看完你就懂了

2021-09-18 07:08:52

(41)FPGA狀態(tài)機一段式1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA狀態(tài)機一段式5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 06:45:18

設(shè)計驗證周期過程中使用的工具及技術(shù),并逐一審視各項優(yōu)缺點。 有效驗證降低設(shè)計風險FPGA設(shè)計驗證的規(guī)畫和預(yù)算安排的失敗,可能瓦解整個產(chǎn)品開發(fā)計畫;時程的延誤會和光罩技術(shù)的再修正(respin)一樣嚴重

2010-05-21 20:32:24

時序仿真的重要性是什么傳統(tǒng)的FPGA驗證方法是什么FPGA設(shè)計的驗證技術(shù)及應(yīng)用原則是什么

2021-05-08 09:05:32

仿真驗證概述本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 仿真測試是FPGA設(shè)計流程中必不可少的步驟

2019-04-10 06:35:34

(10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:47:50

fpga 簡介

2013-02-16 13:46:33

fpga的簡介適合新手

2013-01-12 17:22:32

驗證方法簡介 設(shè)計驗證是用于證明設(shè)計正確性的過程,要求和規(guī)格。 在數(shù)字設(shè)計流程中,驗證可確保芯片按照設(shè)計意圖正確運行,然后再將設(shè)計送去制造。 具體來說,驗證方法是驗證集成電路設(shè)計的標準化方法。 驗證

2022-02-13 17:03:49

...............................................11.2 FPGA 驗證技術(shù)...............................................31.3 Altera

2015-09-18 15:26:25

ASIC設(shè)計-FPGA原型驗證

2020-03-19 16:15:49

1.射頻(RF)技術(shù)簡介RF(Radio Frequency)技術(shù)被廣泛應(yīng)用于多種領(lǐng)域,如:電視、廣播、移動電話、雷達、自動識別系統(tǒng)等。專用詞RFID(射頻識別)即指應(yīng)用射頻識別信號對目標物進行識別

2019-06-20 08:34:25

有沒有搞過Xilinx FPGA回讀驗證的,尋人共同討論

2014-09-20 09:15:09

PS和PL互聯(lián)技術(shù)ZYNQ芯片開發(fā)流程的簡介

2021-01-26 07:12:50

海淀區(qū)永定路 技術(shù)要求:1)熟悉Verilog/VHDL中的一門語言;2)具有扎實的數(shù)字芯片設(shè)計基礎(chǔ),熟悉FPGA設(shè)計驗證流程;3)熟悉ISE、Libero、Quartus等FPGA開發(fā)工具

2018-02-08 11:17:26

使用高級校準技術(shù)驗證收發(fā)器FPGA

2019-09-19 09:05:14

基于FPGA的數(shù)字脈沖壓縮技術(shù)1.數(shù)字脈沖壓縮實現(xiàn)原理2.電路設(shè)計2.1APEX2OKE系列FPGA 簡介2.2 基于FPGA 的算法研究及實現(xiàn) 2.3 脈沖壓縮在FPGA 上的實現(xiàn)

2011-03-02 09:41:50

隨著SoC設(shè)計上的混合信號組件數(shù)量增加了,基本的功能驗證對于硅初期能否成功也愈來愈重要。FPGA在系統(tǒng)整合難題上加入了一個新特點。在核心上,此新范例-可編程系統(tǒng)單芯片(programmable

2011-10-16 22:55:10

FPGA在視頻處理方面可能很有用處,但在驗證基于FPGA的視頻系統(tǒng)時,則需要仔細關(guān)注您所用的方法。

2019-07-23 06:36:45

但是,如果FPGA通過接口與DSP核心連接,并且高速視頻數(shù)據(jù)是通過它來傳輸,那么它根本不是簡單的系統(tǒng)。這種更高的設(shè)計復(fù)雜度導(dǎo)致了額外的驗證難題,并且如果您在設(shè)計階段晚期發(fā)現(xiàn)一處重大錯誤,那么這還會導(dǎo)致高成本的系統(tǒng)板重制。為了消除這一隱患,您必須仔細考慮自己采用的驗證方法,以便降低重制風險。

2019-09-19 06:00:59

智能家庭現(xiàn)有技術(shù)及驗證要點分析

2021-05-08 06:02:33

硬件驗證語言——簡介 硬件驗證語言 (HVL) 是一種編程語言,用于驗證以硬件描述語言 (HDL) 編寫的電子電路設(shè)計。 HVL 通常包括高級編程語言(如 C++ 或 Java)的特性,以及類似于

2022-02-16 13:36:53

本帖最后由 eehome 于 2013-1-5 10:01 編輯

EDA先鋒工作室的精品書籍,國內(nèi)少有的系統(tǒng)講述FPGA設(shè)計和驗證的好書,特別是驗證部分很精華,現(xiàn)在和大家分享,同時附上本書的實例源代碼和Verilog HDL語法國際標準。

2011-08-02 14:54:41

隨著基于FPGA進行原型設(shè)計的復(fù)雜性不斷增加,市場對更好調(diào)試技術(shù)的需求也日益增加。FPGA原型設(shè)計可用于驗證、早期軟件開發(fā)、概念證明等,因此變得非常重要。它的主要職責仍然是執(zhí)行這些任務(wù),而不是試圖找出因原型構(gòu)建錯誤而造成的問題。

2019-09-27 07:05:17

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經(jīng)成為ASIC芯片設(shè)計中重要的驗證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設(shè)計,并給出驗證結(jié)果。

2019-06-18 07:43:00

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經(jīng)成為ASIC芯片設(shè)計中重要的驗證方法。本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設(shè)計,并給出驗證結(jié)果。1、RFID芯片的FPGA

2019-05-29 08:03:31

在芯片的研發(fā)環(huán)節(jié),FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約

2010-06-24 17:43:35 29

29 FPGA驗證是基于VHDL的VLSI設(shè)計中非常重要的一個環(huán)節(jié)。用戶設(shè)計的電子系統(tǒng)首先必須是可綜合的,綜合之后再通過FPGA原型驗證,即可在物理層面對用戶設(shè)計完成實物驗證。通過FPGA驗證

2010-07-12 19:13:59 28

28 隨著SoC設(shè)計復(fù)雜度的提高,驗證已成為集成電路設(shè)計過程中的瓶頸,而FPGA技術(shù)的快速發(fā)展以及良好的可編程特性使基于FPGA的原型驗證越來越多地被用于SoC系統(tǒng)的設(shè)計過程。本文討論

2010-11-11 16:00:07 35

35 針對基于軟件仿真片上網(wǎng)絡(luò)NoC(Network on Chip)效率低的問題,提出基于FPGA的NoC驗證平臺構(gòu)建方案。該平臺集成可重用的流量產(chǎn)生器TG(Traffic Generation),流量接收器TR(Traffic Receiver)

2011-01-04 16:24:38 12

12 虛擬FPGA邏輯驗證分析儀的設(shè)計

隨著FPGA技術(shù)的廣泛使用,越來越需要一臺能夠測試驗證FPGA芯片中所下載電路邏輯時序是否正確的儀器。目前,雖然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 704

704

FPGA基礎(chǔ)知識簡介

FPGA技術(shù)的發(fā)展歷史縱觀數(shù)字集成電路的發(fā)展歷史,經(jīng)歷了從電子管、晶體管、小規(guī)模集成電路到大規(guī)模以及超大規(guī)模集成

2010-02-09 08:34:01 1412

1412 FPGA教程之頻率簡介

每個CPU都有一個工作頻率,FPGA也不例外(當然,只有你的設(shè)計應(yīng)該是時序邏輯),那該頻率是

2010-03-24 10:41:03 4848

4848

對ASIC設(shè)計進行FPGA原型驗證時,由于物理結(jié)構(gòu)不同,ASIC的代碼必須進行一定的轉(zhuǎn)換后才能作為FPGA的輸入。 現(xiàn)代集成電路設(shè)計中,芯片的規(guī)模和復(fù)雜度正呈指數(shù)增加。尤其在ASIC設(shè)計流程中

2011-03-25 15:16:20 108

108 本內(nèi)容提供了基于FPGA的DSP算法快速驗證,希望對大家學(xué)習(xí)有所幫助

2011-06-15 18:08:07 87

87 臺灣工業(yè)技術(shù)研究院提出一種能夠顯著提升客制化FPGA原型板驗證效率的創(chuàng)新方法,自動化現(xiàn)有的 電路仿真 (in-circuit emulation)偵錯功能,并提供更高的FPGA能見度。這個以FPGA為基礎(chǔ)的SoC驗

2011-09-09 11:35:24 1404

1404

S2C日前宣布其Verification Module技術(shù)(專利申請中)已可用于其基于 Xilinx 的FPGA原型驗證系統(tǒng)中。V6 TAI Verification Module可以實現(xiàn)在FPGA原型驗證環(huán)境和用戶驗證環(huán)境之間高速海量數(shù)據(jù)傳輸。用戶

2011-09-20 09:07:58 1622

1622 FPGA論壇精華帖摘選,主要是講述驗證、仿真方面的技術(shù)。

2015-11-30 17:41:48 0

0 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設(shè)計的簡介

2016-01-06 11:32:55 65

65 基于FPGA_A_D的數(shù)據(jù)采集設(shè)計及驗證

2016-05-10 11:24:33 26

26 Cyclone FPGA系列簡介

2016-12-26 22:02:46 0

0 一種基于FPGA的雙接口NFC芯片驗證系統(tǒng)_彭廣

2017-01-03 15:24:45 5

5 EtherCAT是一種實時工業(yè)以太網(wǎng)協(xié)議,使用鏈路冗余技術(shù)是實現(xiàn)鏈路穩(wěn)定性和可靠性的重要手段。介紹了基于FPGA的EtherCAT鏈路冗余原理,設(shè)計通過FPGA實現(xiàn)主站與從站、從站與從站之間的通信鏈

2017-11-15 12:42:13 9791

9791

技術(shù)方法,驗證了SoC系統(tǒng)、DSP指令、硬件IP等。實驗證明,此FPGA驗證平臺能夠驗證SoC設(shè)計,提高了設(shè)計效率。

2017-11-17 03:06:01 21449

21449

技術(shù)方法,驗證了SoC系統(tǒng)、DSP指令、硬件IP等。實驗證明,此FPGA驗證平臺能夠驗證SoC設(shè)計,提高了設(shè)計效率。

2017-11-17 03:06:01 5210

5210

隨著集成電路設(shè)計技術(shù)的發(fā)展和芯片集成度的提高,驗證已經(jīng)成為芯片設(shè)計流程中的主要瓶頸。本文設(shè)計了一個基于FPGA的智能卡驗證平臺,并對驗證方法做了詳細闡述。本文對于雙界面智能卡芯片驗證的成功實踐

2017-11-17 16:25:01 1455

1455 利用Xilinx的FPGA設(shè)計了一個FPGA原型驗證平臺,用于無源高頻電子標簽芯片的功能驗證。主要描述了驗證平臺的硬件設(shè)計,解決了由分立元件實現(xiàn)模擬射頻前端電路時存在的問題,提出了FPGA器件選型

2017-11-18 08:42:22 4347

4347

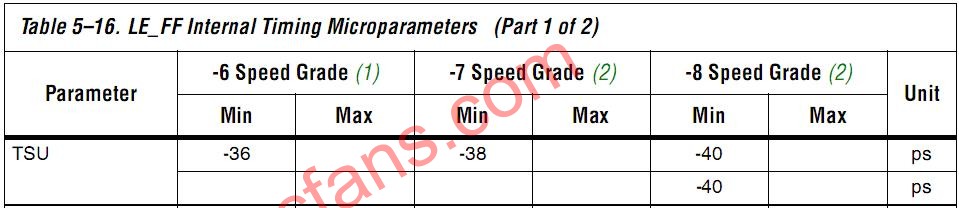

FPGA設(shè)計和驗證工程師當今面臨的最大挑戰(zhàn)之一是時間和資源制約。隨著FPGA在速度、密度和復(fù)雜性方面的增加,完成一個完整時序驗證對人力和計算機處理器、存儲器提出了更多更高的要求。 隨著FPGA器件

2019-10-06 17:57:00 1556

1556

隨著基于FPGA進行原型設(shè)計的復(fù)雜性不斷增加,市場對更好調(diào)試技術(shù)的需求也日益增加。FPGA原型設(shè)計可用于驗證、早期軟件開發(fā)、概念證明等,因此變得非常重要。它的主要職責仍然是執(zhí)行這些任務(wù),而不是試圖找出因原型構(gòu)建錯誤而造成的問題。

2018-07-11 09:31:00 1633

1633 ( Achronix Semiconductor Corporation)日前宣布:已完成了其采用臺積電(TSMC)16nm FinFET+工藝技術(shù)的SpeedcoreTM eFPGA量產(chǎn)驗證芯片的全芯片驗證。通過在所

2018-01-22 16:46:01 2180

2180 有關(guān)FPGA設(shè)計驗證的相關(guān)方法

2018-04-03 15:01:41 10

10 本文檔的主要內(nèi)容詳細介紹的是FPGA教程之ISE設(shè)計流程簡介的詳細資料說明。

2019-04-04 17:18:45 15

15 復(fù)旦大學(xué)微電子學(xué)院某國家重點實驗室內(nèi)部教學(xué)視頻:基于ZYNQ FPGA與PC的IP設(shè)計與驗證方案。

關(guān)鍵詞:IP設(shè)計,IP驗證,AXI總線協(xié)議,ARM,UDP傳輸,PYTHON

2019-08-06 06:16:00 2714

2714

本文檔的主要內(nèi)容詳細介紹的是FPGA的硬件電路設(shè)計教程和FPGA平臺資料簡介包括了:FPGA技術(shù)概述;主流FPGA器件介紹;VIRTEX-5 FPGA電路設(shè)計;V4LX160 FPGA平臺介紹;

2020-07-06 18:11:22 177

177 國微思爾芯(“S2C”), 全球領(lǐng)先的前端電子設(shè)計自動化 (EDA) 供應(yīng)商, 發(fā)布全球首款FPGA驗證仿真云系統(tǒng) Prodigy Cloud System。這是為下一代 SoC 設(shè)計驗證需要而特別

2020-07-13 09:18:38 1030

1030 介紹了一種雙接口NFC芯片的架構(gòu)和功能,提岀并實現(xiàn)了用于該雙接口NFC芯片的FPGA驗證系統(tǒng)及其驗證流程。該FPGA驗證系統(tǒng)包括FPGA、PIC單片機以及帶NFC功能的手機,可有效縮短芯片設(shè)計周期

2021-05-26 14:03:26 17

17 基于FPGA的寬頻帶數(shù)字鎖相環(huán)的設(shè)計與實現(xiàn)簡介說明。

2021-06-01 09:41:14 26

26 基于FPGA的ROM的實現(xiàn)簡介(嵌入式開發(fā)工程師培訓(xùn)學(xué)校)-該文檔為基于FPGA的ROM的實現(xiàn)簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:08:40 5

5 基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)簡介(嵌入式開發(fā)工程師和基層公務(wù)員)-該文檔為基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)簡介文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 09:34:59 11

11 1. FPGA 簡介第1節(jié) 什么是 FPGAFPGA 的全稱為 Field-Programmable Gate Array,即現(xiàn)場可編程門陣列。 FPGA 是在 PAL、 GAL、 CPLD 等

2021-11-30 17:21:05 45

45 其次,部分FPGA開發(fā)板也被用在IP和小型芯片設(shè)計的開發(fā)驗證場景。這部分開發(fā)板配備大容量的FPGA芯片,甚至是單板配備多片FPGA芯片來適應(yīng)開發(fā)驗證場景,一般由用戶自己負責手工實現(xiàn)從設(shè)計到FPGA功能原型的流程。

2022-04-28 09:38:33 3563

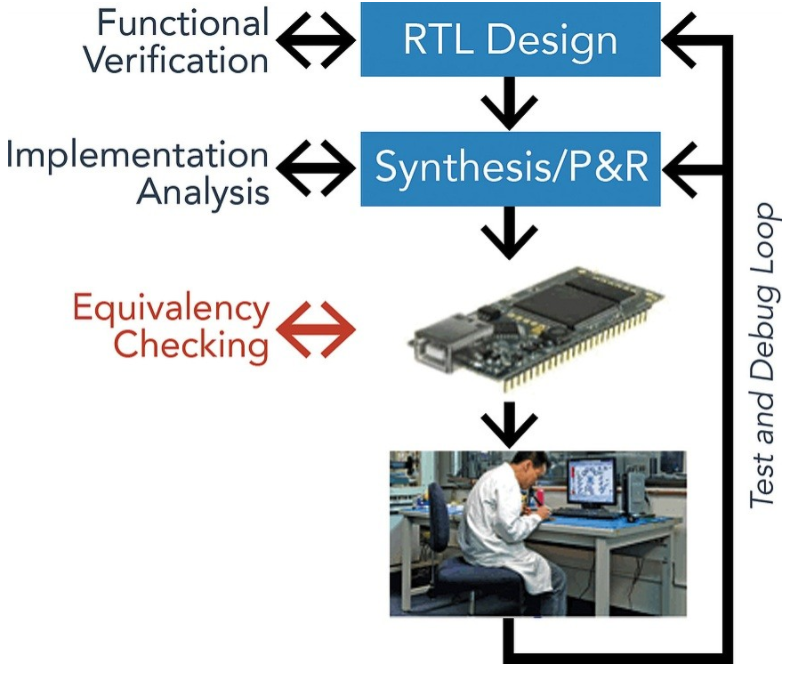

3563 隨著 FPGA 變得越來越大和越來越復(fù)雜,它們的設(shè)計和功能驗證趨向于 ASIC。在現(xiàn)代 FPGA 設(shè)計流程的先進性的推動下,這種趨勢現(xiàn)在正在擴展到實現(xiàn)驗證領(lǐng)域。EC 現(xiàn)在是該流程的必要組成部分,保留了 FPGA 生產(chǎn)過程中的固有效率。

2022-06-14 09:21:55 2067

2067

FPGA電源簡介

2022-11-04 09:51:06 0

0 在芯片的研發(fā)環(huán)節(jié),FPGA驗證是其中的重要的組成部分,如何有效的利用FPGA的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應(yīng)的工具自動分配,但是從研發(fā)

2023-02-22 17:45:02 9859

9859 在現(xiàn)代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應(yīng)該是非常熟悉的場景了。

2023-03-28 09:33:16 2001

2001 我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-03-28 14:11:15 1690

1690 FPGA原型驗證在數(shù)字SoC系統(tǒng)項目當中已經(jīng)非常普遍且非常重要,但對于一個SoC的項目而言,選擇合適的FPGA原型驗證系統(tǒng)顯的格外重要

2023-04-03 09:46:45 2074

2074 當SoC系統(tǒng)的規(guī)模很大的時候,單片FPGA驗證平臺已經(jīng)無法容納這么多容量,我們將采取將SoC設(shè)計劃分為多個FPGA的映射。

2023-04-06 11:20:48 1400

1400 FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2023-04-10 09:23:29 2664

2664 FPGA原型驗證平臺系統(tǒng)靈活性主要體現(xiàn)在其外部連接表現(xiàn)形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統(tǒng)。

2023-04-11 09:50:03 1543

1543 FPGA原型驗證平臺系統(tǒng)靈活性主要體現(xiàn)在其外部連接表現(xiàn)形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統(tǒng)。

2023-04-11 09:50:37 936

936 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規(guī)模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣。

2023-05-04 16:21:34 1331

1331

FPGA原型驗證的原理是將芯片RTL代碼綜合到FPGA上來驗證芯片的功能。對于目前主流行業(yè)應(yīng)用而言,芯片規(guī)模通常達到上億門甚至數(shù)十億門,一顆FPGA的容量難以容納下芯片的所有邏輯功能。

2023-05-18 12:52:52 1145

1145

多片FPGA的原型驗證系統(tǒng)的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數(shù)量受封裝技術(shù)的限制,通常只有1000個左右的用戶IO引腳。

2023-05-23 17:12:35 2189

2189

我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-05-30 11:10:27 1358

1358

在現(xiàn)代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應(yīng)該是非常熟悉的場景了。

2023-05-30 15:04:06 2103

2103

當SoC系統(tǒng)的規(guī)模很大的時候,單片FPGA驗證平臺已經(jīng)無法容納這么多容量,我們將采取將SoC設(shè)計劃分為多個FPGA的映射。

2023-06-19 15:42:08 1081

1081 很多其他行業(yè)也能從電子器件的增加受益,當然保障功能安全是大的前提。本文討論SOC芯片設(shè)計驗證、驗證計劃和策略以及驗證方法。它定義了功能模擬、功能覆蓋、代碼覆蓋以及設(shè)計驗證中使用的重要術(shù)語。本文還涉及FPGA驗證及其在S

2023-07-20 09:05:59 2053

2053 FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2024-01-12 16:13:01 2194

2194 proFPGA是mentor的FPGA原型驗證平臺,當然mentor被西門子收購之后,現(xiàn)在叫西門子EDA。

2024-01-22 09:21:01 3230

3230

FPGA驗證和UVM驗證在芯片設(shè)計和驗證過程中都扮演著重要的角色,但它們之間存在明顯的區(qū)別。

2024-03-15 15:00:41 3024

3024 FPGA驗證和測試在芯片設(shè)計和開發(fā)過程中都扮演著重要的角色,但它們各自有著不同的側(cè)重點和應(yīng)用場景。

2024-03-15 15:03:26 2325

2325 FPGA原型驗證流程是確保FPGA(現(xiàn)場可編程門陣列)設(shè)計正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計實現(xiàn)到功能驗證的整個過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 3058

3058 FPGA原型驗證平臺與硬件仿真器在芯片設(shè)計和驗證過程中各自發(fā)揮著獨特的作用,它們之間存在明顯的區(qū)別。

2024-03-15 15:07:03 2340

2340

電子發(fā)燒友App

電子發(fā)燒友App

評論