SAMC21(一款 Cortex-M0+ MCU)非常適合需要數學計算的應用。SAMC21 MCU 具有可進行乘法運算的快速單周期乘法器選項,還具有一個新的外設,稱為除法和平方根加速器

2018-07-19 09:25:25 6371

6371 已經查閱了A53的手冊沒有找到相關的答案,自己有剛剛接觸這方面,老大給的任務,希望有大佬幫忙指點一下,或是有相關資料經驗也可以。ARM cortex-A53相關性能:是否支持硬件預取、整型流水線的個數、乘法器的個數及時鐘周期、除法器的個數及時鐘周期、整形流水線中乘法器的個數。

2020-01-16 20:32:32

位來完成。實際上乘以任何一個整數都可以用移位和加法來代替乘法。ARM 7 中加法和移位可以通過一條指令來完成,且執行時間少于乘法指令。例如: i = i × 5 可以用i = (i (y × z

2011-07-07 11:06:42

我是電子技術員,努力學習PIC的C編程。我已經用XC8編譯器為pic16f676編寫了簡單的程序,以便理解ADC。當我直接比較adc結果(0到1023)時,當我像下面的程序那樣對adc結果進行乘法和除法時,程序運行良好,為什么它不工作呢?如何解決這個問題?

2020-04-23 06:15:39

優化電路設計:在電路設計中,可以采用更快速的邏輯單元和存儲器元件,優化關鍵路徑和信號傳輸路線,從而降低延遲,縮短乘法器的運算周期。

固定位寬:Boot4乘法器可以處理不同位寬的數據,但是處理不同位寬

2025-10-21 12:13:54

優化電路設計:在電路設計中,優化關鍵路徑和信號傳輸路線,使用更高速的邏輯單元和存儲器元件來降低延遲,從而縮短乘法器的運算周期。

利用流水線技術:使用流水線技術將乘法操作分成多個階段,使每個階段的操作

2025-10-21 13:17:04

如題,ATMEGA128L中用什么代替GICR??求助!!

2016-07-17 10:23:52

CCS有對這種常數除法自動編譯優化的選項嗎

2023-03-09 15:13:34

優化思路

E203為了實現低功耗的要求,乘法器為基于booth編碼和移位加法器結合的思路,優點是只需要一個加法器,而且該加法器還和除法器復用,可以說是將面積縮小到了極致。缺點也很明顯,即使通過

2025-10-27 07:54:58

請問E203的乘法和除法這種多周期指令是怎么解決數據相關性的?

2025-11-07 06:50:43

Newton-Raphson算法

Newton-Raphson算法采用乘法來代替除法運算,即a/b=a(1/b),基本原理如下:

已知曲線方程f(x),我們在xn點做切線,求xn+1

首先我們

2025-10-24 07:53:47

Verilog中用*實現乘法和用乘法器ip核實現乘法綜合結果有哪些不同?

2016-03-18 09:35:13

首先我們知道,對于e203的乘除法器,為了實現低功耗,低面積、高資源利用率,乘除法過程復用了alu數據通路,沒有設計單獨的乘除法器。

其中乘法采用基4booth編碼得到部分積,并通過移位相加,復用

2025-10-24 06:37:44

我在使用quartus自帶的乘法核時遇到了問題,得到的電路文件沒有輸出端口,然后我直接用VHDL例化,仿真也沒有結果,說明也是沒有輸出。那么問題來了,為啥除法器加法器減法器都有輸出,這個乘法器就沒有,是license不全嗎?

2018-12-12 15:20:46

其性能十分低下。

對于乘法操作,為了減少乘法操作所需的周期數, MDV 對乘法采用基 (Radix-4 ) 的Booth 編碼,進行一次乘法操作需要17個時鐘周期。

對于除法操作,采用普通的加減交替法

2025-10-27 07:16:56

為什么MCU中的除法運算要比乘法運算的效率低

2023-10-09 07:45:11

有一個卡爾曼算法,里面很多乘法運算,現在就是考慮到產品的穩定性,如何避免乘法運算造成CPU內存泄露或者實時性較差!

2016-06-25 13:03:22

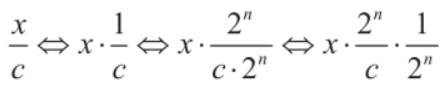

速度快。(3) 用位移代替乘法除法N=M*8 可以改為N=M3說明:通常如果需要乘以或除以2n,都可以用移位的方法代替。如果乘以2n,都可以生成左移的代碼,而乘以其它的整數或除以任何數,均調用乘除法

2011-12-05 13:53:51

乘法除法N=M*8 可以改為N=M3說明:通常如果需要乘以或除以2n,都可以用移位的方法代替。如果乘以2n,都可以生成左移 的代碼,而乘以其它的整數或除以任何數,均調用乘除法子程序。用移位的方法得到代碼

2021-07-09 06:30:00

=a*a*a;則效率的改善更明顯。(3)用移位實現乘除法運算a=a*4;b=b/4;可以改為:a=a2;說明:通常如果需要乘以或除以2n,都可以用移位的方法代替。在ICCAVR 中,如果乘以2n,都可以

2020-06-07 09:34:55

主要的除法運算優化方法是使用基本的SRT-4算法進行除法運算,以模擬SRT-64除法運算:

為了減少時鐘周期并提高運算頻率,極大基法是SRT算法中提出的一種方法。在該方法中,每次迭代的位數取決于所

2025-10-23 07:23:18

運算(/和%)執行起來比較慢,所以應盡量避免使用。但是,除數是常數的除法運算和用同一個除數的重復除法,執行效率會比較高。在ARM中,可以利用單條MUL指令實現乘法操作。本文將闡述如何用乘法運算代替除法

2011-07-14 14:48:47

匯編實現多字節乘除法乘法單片機的乘法本質是二進制的乘法,而乘法本身是通過加法實現的。多字節的乘法其實就是移位做加法。例如7x11,用二進制豎式表示如下圖:可以看到,其實就是判斷乘數的每一位是1還是0

2021-11-24 06:59:27

=(2k-1)/d。可用乘以s的2k位乘法來代替除以d的k位無符號整數除法。4)使用2的整數次冪作除數。當2的整數次冪做除數時,編譯器會自動將除法運算轉換成移位運算。所以在編寫程序算法時,盡量使用2

2018-03-31 22:17:10

使用除法程序同時產生商n/d和余數n%d的好處。3) 對于重復對同一除數d的除法,預先計算好s=(2k-1)/d。可用乘以s的2k位乘法來代替除以d的k位無符號整數除法。4)使用2的整數次冪作除數。當2

2020-04-20 11:36:07

) 對于重復對同一除數d的除法,預先計算好s=(2k-1)/d。可用乘以s的2k位乘法來代替除以d的k位無符號整數除法。4)使用2的整數次冪作除數。當2的整數次冪做除數時,編譯器會自動將除法運算轉換成移位

2020-04-22 10:26:25

蜂鳥E203是一款基于RISC-V指令集的多核處理器,內置了乘法和除法運算單元,這些運算單元的性能直接影響到整個處理器的性能表現。因此,優化乘除法器是提高整個處理器性能的重要手段之一。

一、原理介紹

2025-10-24 06:47:29

在數字信號處理中,乘法器是整個硬件電路時序的關鍵路徑。速度和面積的優化是乘法器設計過程的兩個主要考慮因素。由于現代可編程邏輯芯片FPGA的集成度越來越高,及其相對于ASIC設計難度較低和產品設計

2019-09-03 07:16:34

首先,根據之前分享的乘法器的優缺點,我們針對17周期的乘法器進行優化,為乘法設計的專用數據通路,為了保持e203的低功耗、低面積的優點、我們仍采用基4booth算法進行部分積生成,而對于原有的17

2025-10-23 06:37:01

各位大俠,我在使用DSP2833CCS3.3軟件編程做除法運算時,每次得到的結果都是0,請問這是為什么?加減乘法都能正確計算。謝謝

2015-01-16 16:14:28

,常常在各類文章里看到,編程人員應該使用右移運算來代替除法。這個右移方法沒有問題,也確實能提高微處理器的計算能力,節省處理時間。但是,我們必須要注意到,這種方式只適用于整數運算的2的倍數的除法,即除以2

2019-04-30 00:31:32

,如加減、乘除、乘加、開方、比較等。

3.乘除法器優化:對于乘法操作,為了減少乘法操作所需的周期數,可以采用基(Radix-4)的Booth編碼,進行一次乘法操作需要17個時鐘周期。對于除法操作,采用

2025-10-22 07:04:49

現在的ASIC綜合器可以綜合出經過優化的乘法、除法和求模的電路嗎?也就是說在Verilog代碼里直接用*、/和%就可以實現相應運算嗎?

2014-11-12 16:35:26

蜂鳥的乘法器主體設計在ALU模塊的子單元MDV模塊中,MDV模塊包括乘除法器邏輯設計,它只包含運算控制,但并不包含具體運算,它們都需要將部分積或者部分余數傳入數據通路(dpath模塊)中,從而實現

2025-10-22 08:21:36

乘法器的優化實現一般從兩個方面入手。第一是減少生成的部分積數量,另外就是減少部分積累加的延時。

在開源的E203源碼中,32*32乘法器是利用radix-4 booth編碼產生部分積,每個周期做一次

2025-10-22 06:11:44

,第二部分是關于 Python AI 應用在 ARM 云平臺-倚天 710 上的最佳實踐。一、優化工作介紹前面說我們的優化是和矩陣乘法相關的,那首先需要說明為什么我們會關注到這個。這里有一個繞不開的場景

2022-12-23 16:02:46

我在用ARM的時候挺困惑的,LPC111x有硬件的乘法、除法器嗎?我找了2遍datasheet,上說有乘法器。ARM一般都應該有硬件的乘法、除法器吧? 我想確定一下。還有就是lpc111x的ARM的IAP可以字節操作嗎? 在usermanul上沒找到響應的命令是不是就代表沒有啊?謝謝各位指點啊!

2011-03-21 17:28:12

請問各位,DSP2803x的IQmath.h在使用過程中乘法可以使用,除法不能使用是怎么回事呢?都在一個頭文件里面,為什么除法連編譯都過去不呢?Description Resource Path

2018-10-01 17:31:31

請高人指點:ARM系統中的除法是怎么實現的?最好能給arm的匯編源碼看看,謝謝啦!

2022-06-17 11:42:05

如果除法中的除數是2的冪次,我們可以更好的優化除法。

編譯器使用移位操作來執行除法。因此,我們需要盡可能的設置除數為2的冪次(例如64而不是66)。

并且依然記住,無符號unsigned整數除法

2025-12-12 06:02:27

TI推出的CDC706是目前市場上體積最小且功能強大的PLL合成器/乘法器/除法器之一。盡管其物理外形非常小巧,但卻極為靈活。該器件能夠在特定輸入頻率下生成幾乎獨立的輸出頻率。

2009-11-26 14:35:47 21

21 AD534是一款單芯片激光調整四象限乘法器除法器,其精度規格以前只有昂貴的混合或模塊化產品才有。無需任何外部調整,AD534L的最大乘法誤差保證為0.25%。出色的電源抑制性能、低溫度系數以及片內

2023-08-09 16:52:53

高精度的乘除法和開方等數學運算在FPGA實現中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計算時延要求較低的應用中,以處理時間換取資源的串行運算方法具有廣泛的應

2010-07-28 18:05:14 37

37 描述AD534是一款單芯片激光調整四象限乘法器/除法器,可提供以前只有昂貴的混合式或模塊式產品才具有的精度規格。無需外部調整便可保證±0.25%的最大乘法誤差。該器件具有出色的電源抑制、低溫度系數

2024-01-11 15:27:16

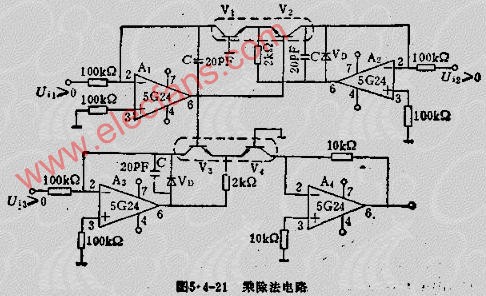

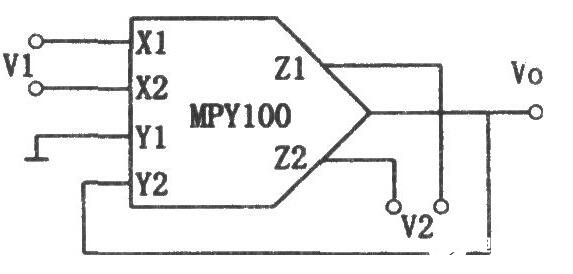

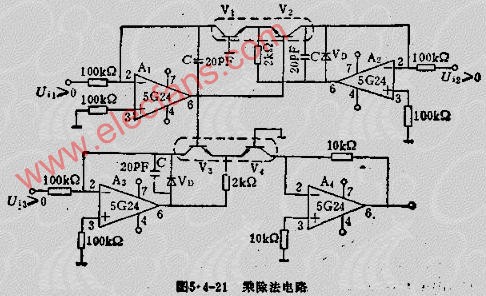

模擬乘法器在運算電路中的應用

8.6.1 乘法運算電路

8.6.2 除法運算電路

8.6.3 開方運算電路

2010-09-25 16:28:45 146

146 AD532是首款預調整的單芯片乘法器/除法器;無需任何外部調整電阻或輸出運算放大器,即可保證±1.0%的最大乘法誤差和±10 V的輸出電壓范圍。AD532經過內部調整,易于使用,為設計

2010-10-02 09:37:50 133

133 AD534是一款單芯片激光調整四象限乘法器/除法器,可提供以前只有昂貴的混合式或模塊式產品才具有的精度規格。無需外部調整便可保證±0.25%的最大乘法誤差。該器件具有出色的

2010-10-02 09:39:56 133

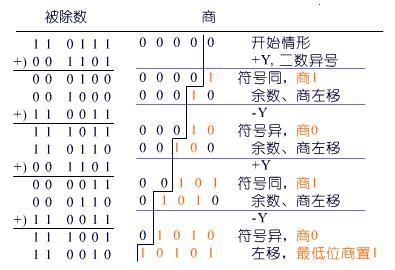

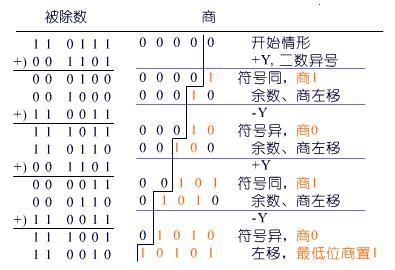

133 定點補碼一位除法的實現方案 與補碼乘法類似,也可以用補碼直接完成除法運算,即用 [X]補/[Y] 補 直接求得[X/Y]補 。補碼除法的規則比原碼除

2009-10-13 22:58:39 3829

3829

并行除法器 ,并行除法器結構原理是什么?

1.可控加法/減法(CAS)單元 和陣列乘法器非常相似,陣列式除法器也是一種并行運算部件,采用大規模集成

2010-04-13 10:46:30 16505

16505 除法器對數運算電路的應用

由對數電路實現除法運算的數學原理是:

2010-04-24 16:07:27 3082

3082

乘除法電路

圖5.4-21是乘除法運算實用電路之一。

1、A

2010-04-26 16:11:49 17164

17164

理解ARM9 與ARM7 的差別,以及如何針對ARM9 進行系統優化,成為了一個令人關注的話題。本文通過對ARM9 處理器的特點介紹,介紹針對ARM9處理器進行系統優化的一些有效方法。

2012-04-13 14:58:18 55

55 計算機如何來計算除法的?

第一步:分析除法

第二步,計算機中對第一步的模擬(真值)

2015-12-31 10:43:18 15

15 14.2 除法運算 因為ARM體系結構本身并不包含除法運算硬件,所以在ARM上實現除法是十分耗時的。ARM指令集中沒有直接提供除法匯編指令,當代碼中出現除法運算時,ARM編譯器會調用C庫函數(有符合

2017-10-17 17:22:29 5

5 ARM9和ARM7的比較及優化

2017-10-31 09:46:43 4

4 乘法器,求模運算部分利用Barrett約減運算,用硬件描述語言進行FPGA設計與實現,避免了除法運算。對于192位的操作數,完成Barrett模乘需要約186個時鐘周期,計算速率可以達到269.17 Mb/s。

2017-11-08 15:18:19 32

32 算法進行改進。算法在乘法運算中引入冗余編碼及差異化思想,從而確保安全性;在除法運算中引入逆元,將除法運算轉化為低復雜度的乘法運算,避免了模運算帶來的開銷,降低了復雜度并提高了算法安全性,并對安全性進行理論論證。理論

2017-12-04 16:44:29 0

0 FPGA中的硬件邏輯與軟件程序的區別,相信大家在做除法運算時會有深入體會。若其中一個操作數為常數,可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結構復雜,且

2018-05-18 01:15:00 5106

5106 我們使用英特爾?數學核心函數庫(MKL)在Linux *上優化了三重嵌套循環矩陣乘法的版本。

2018-11-07 06:04:00 4330

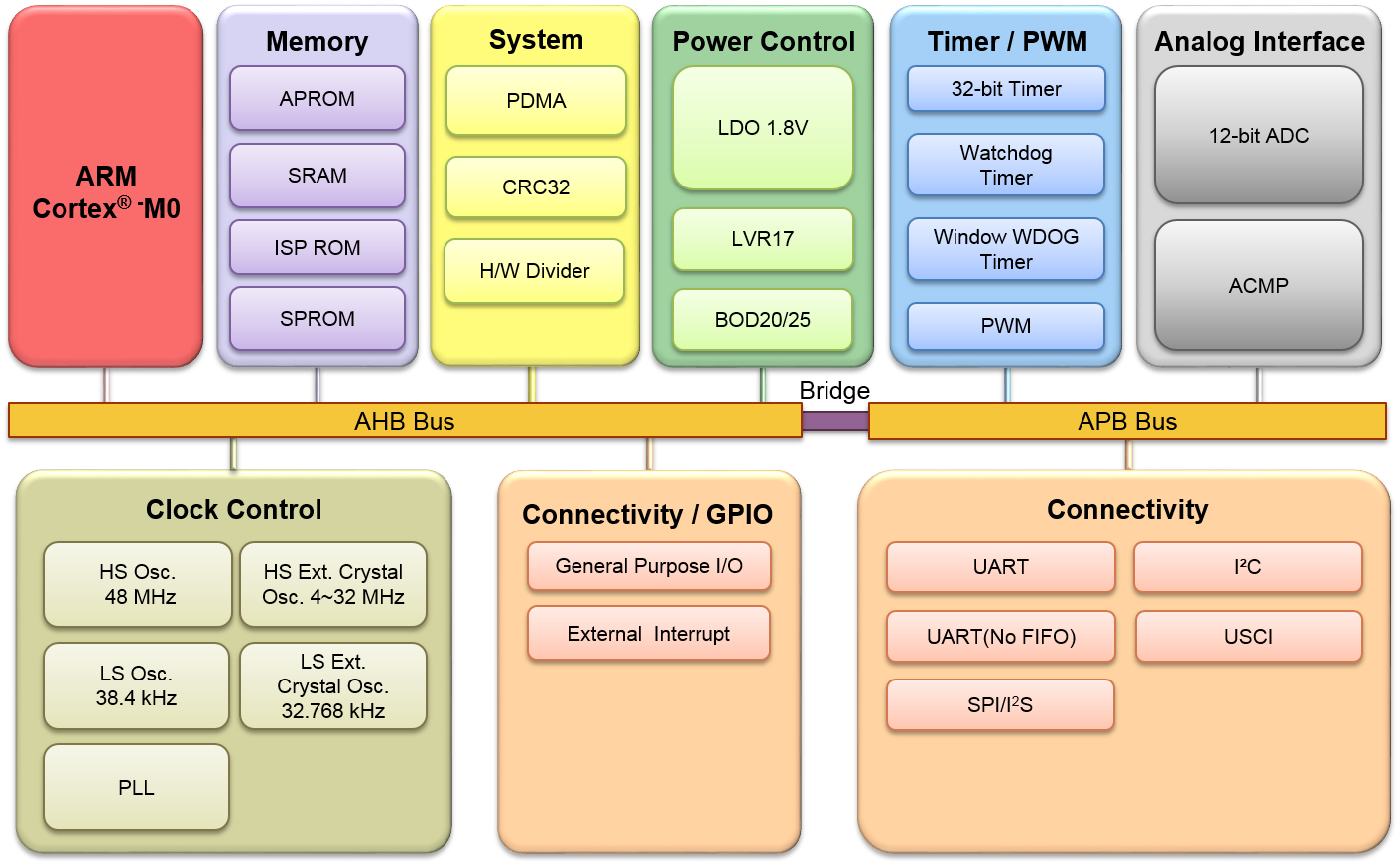

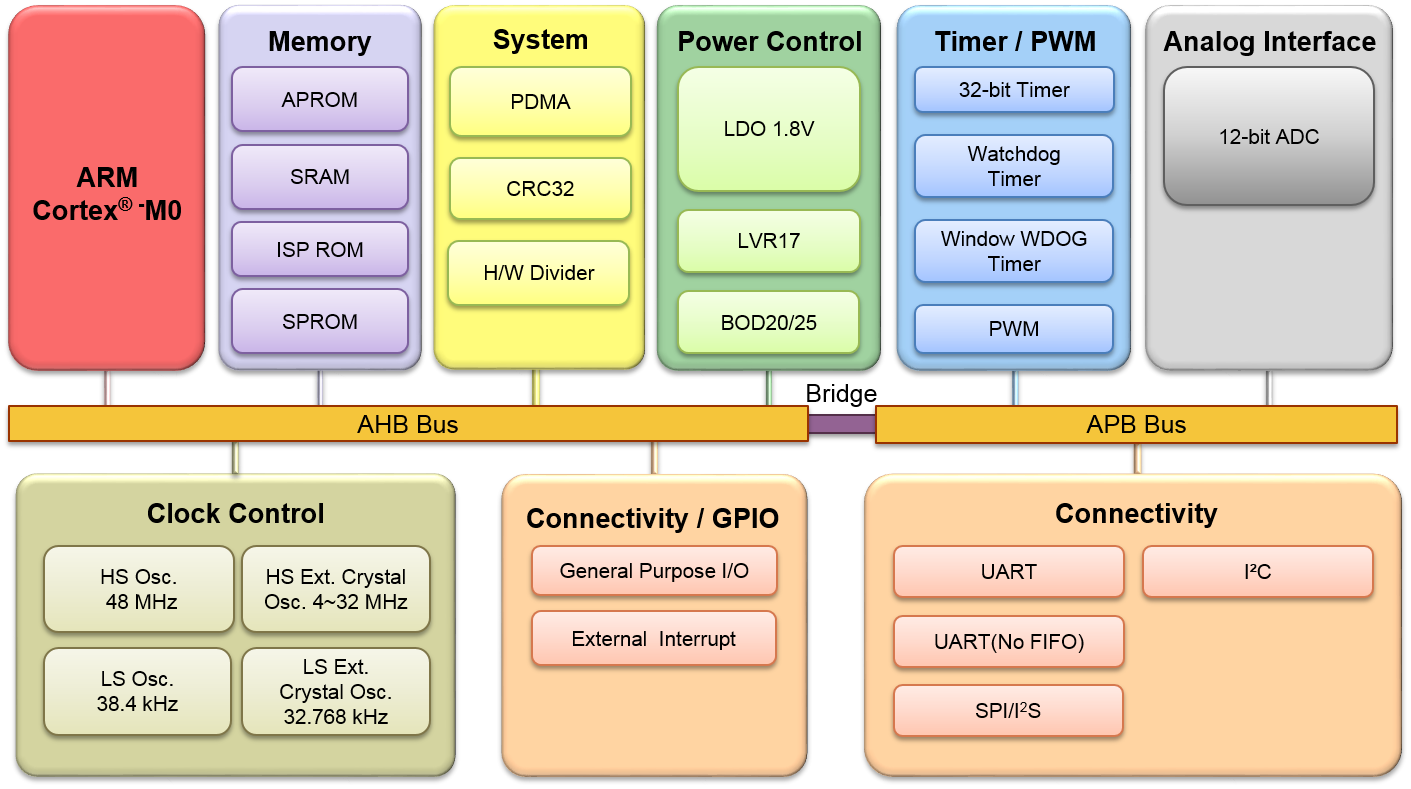

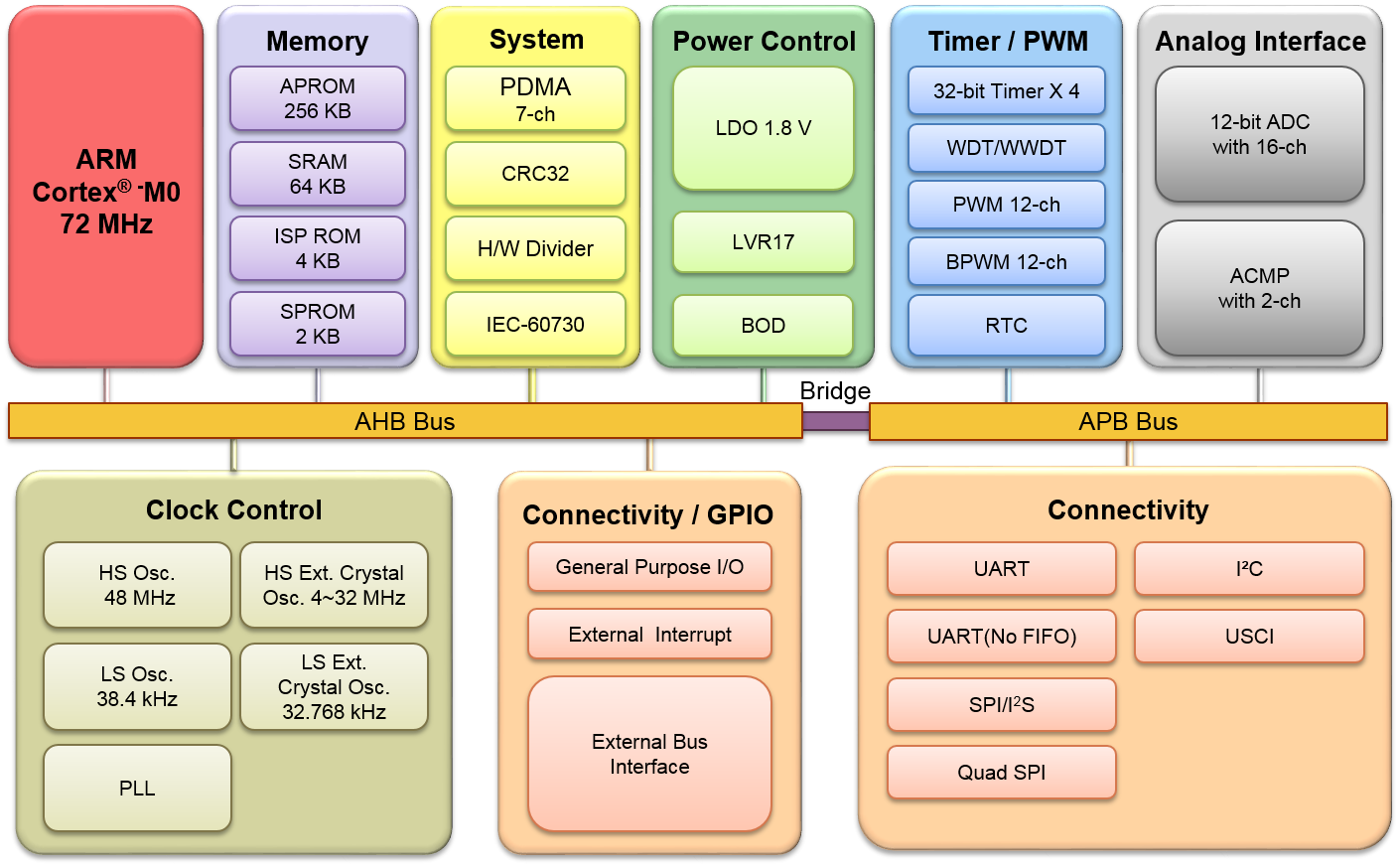

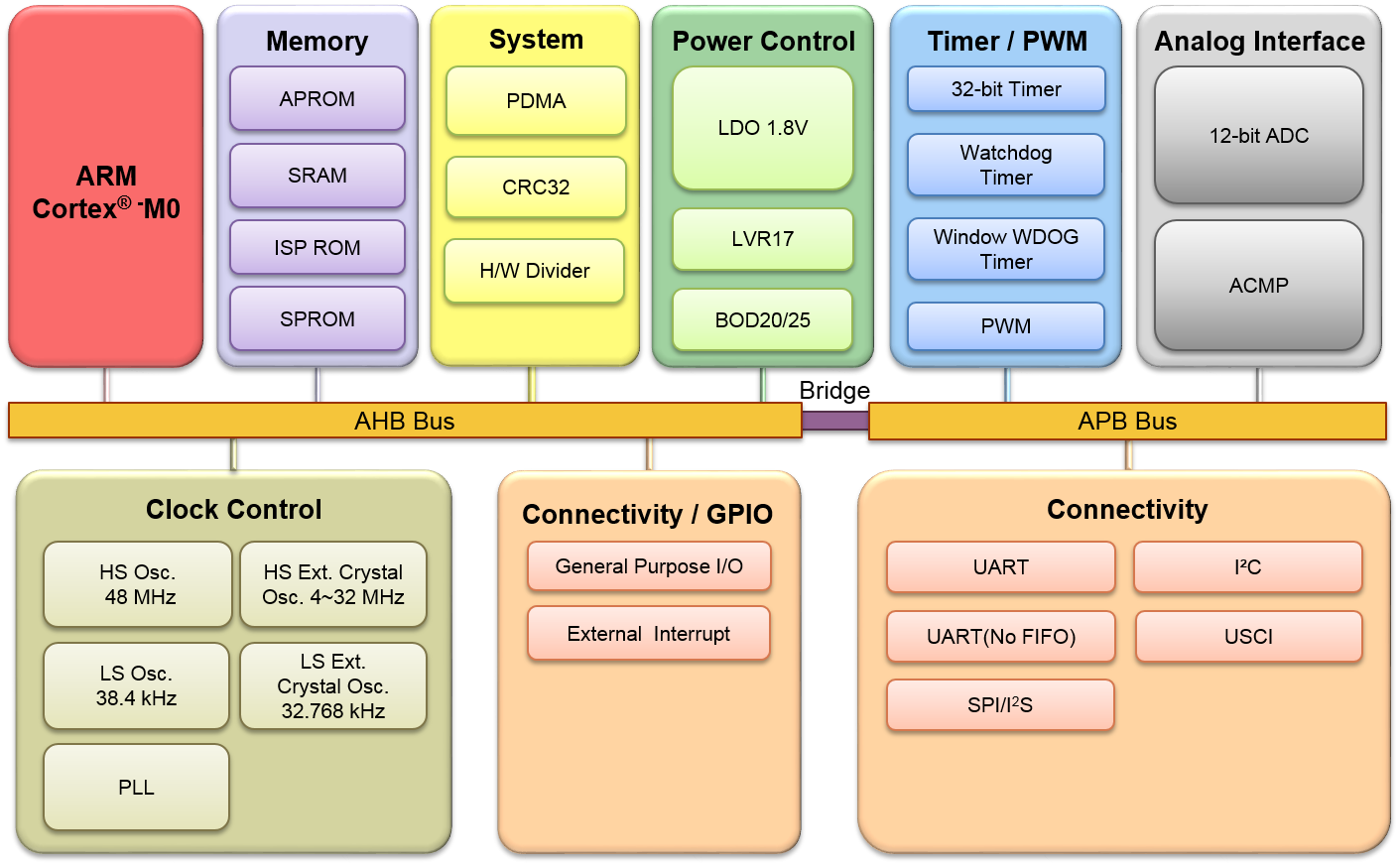

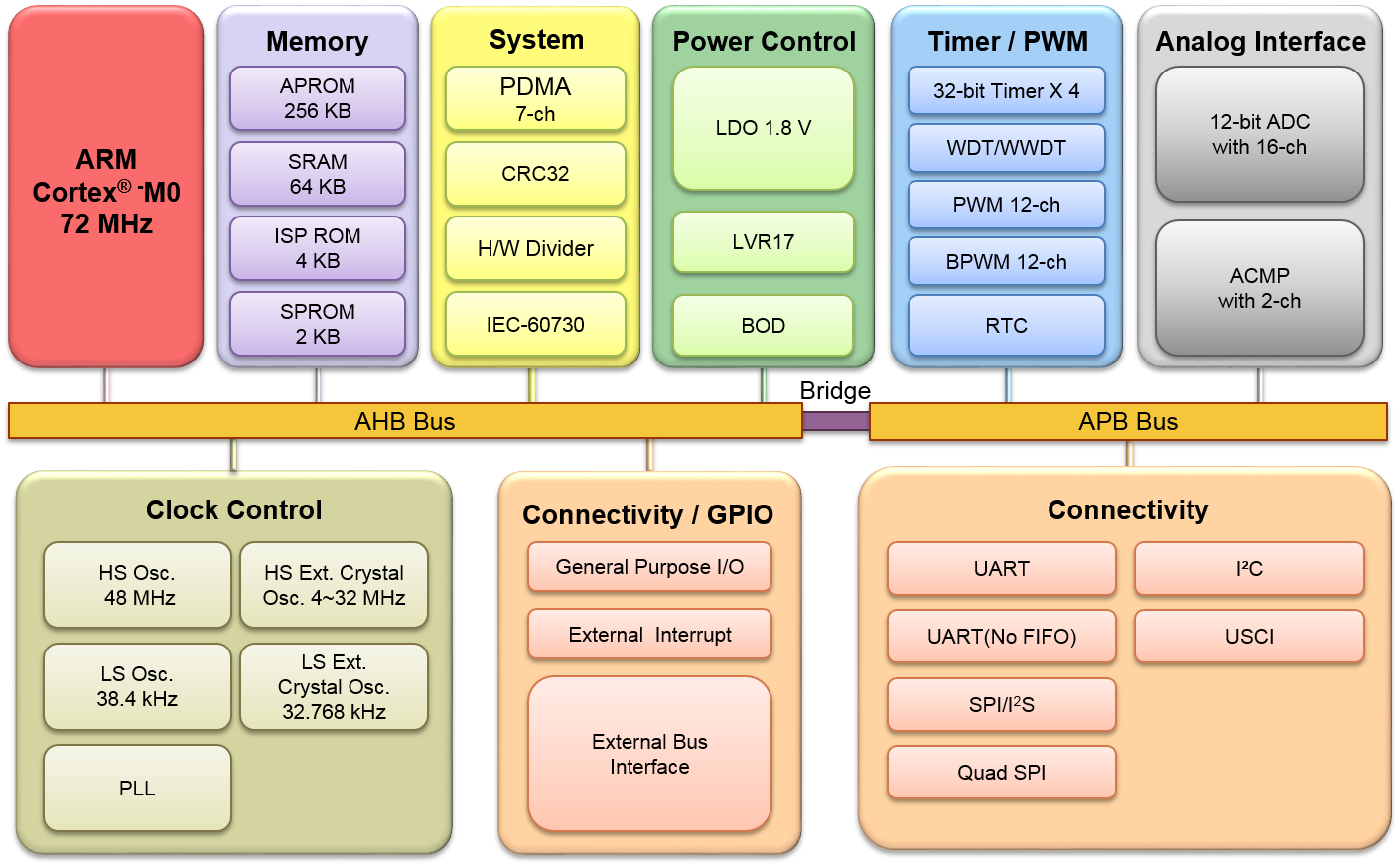

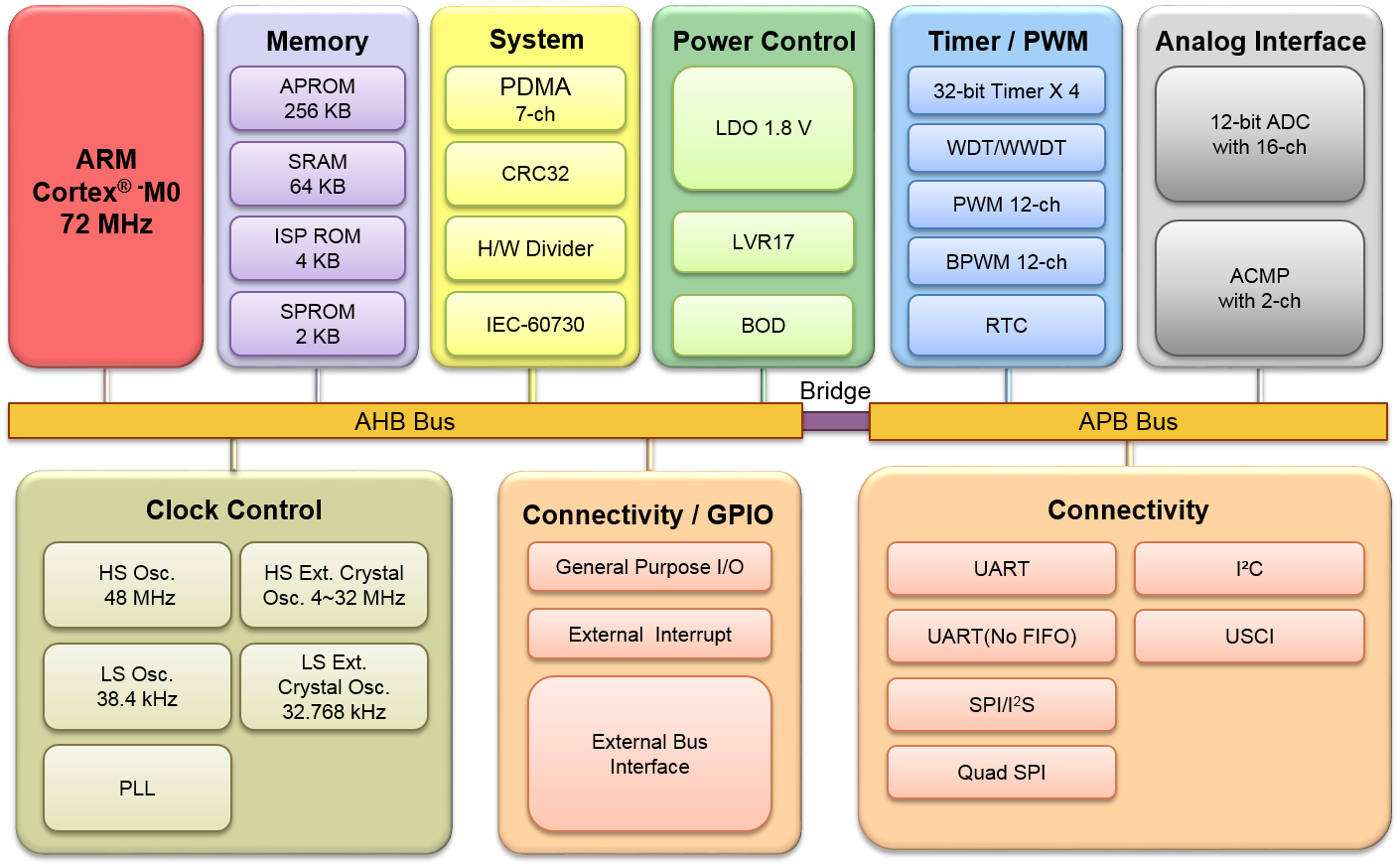

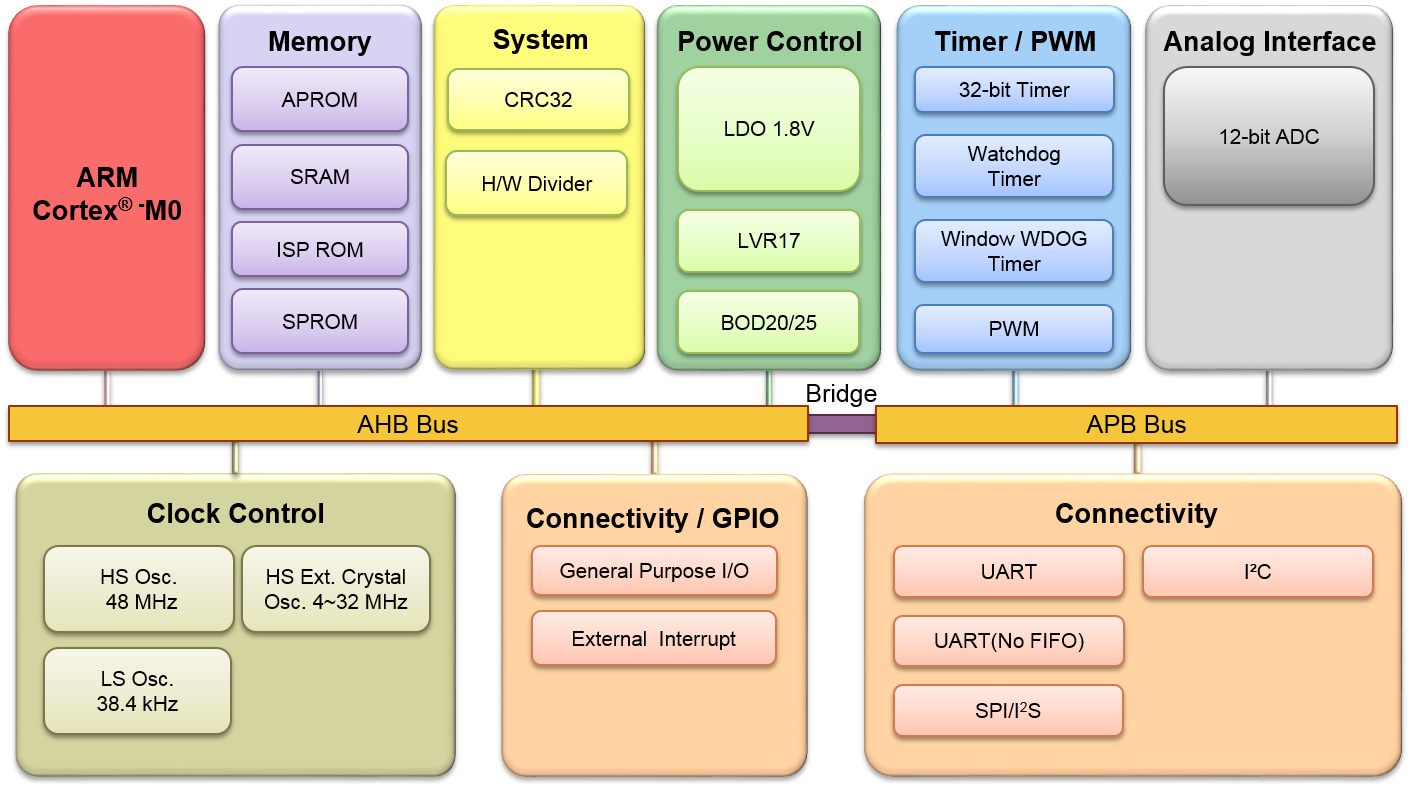

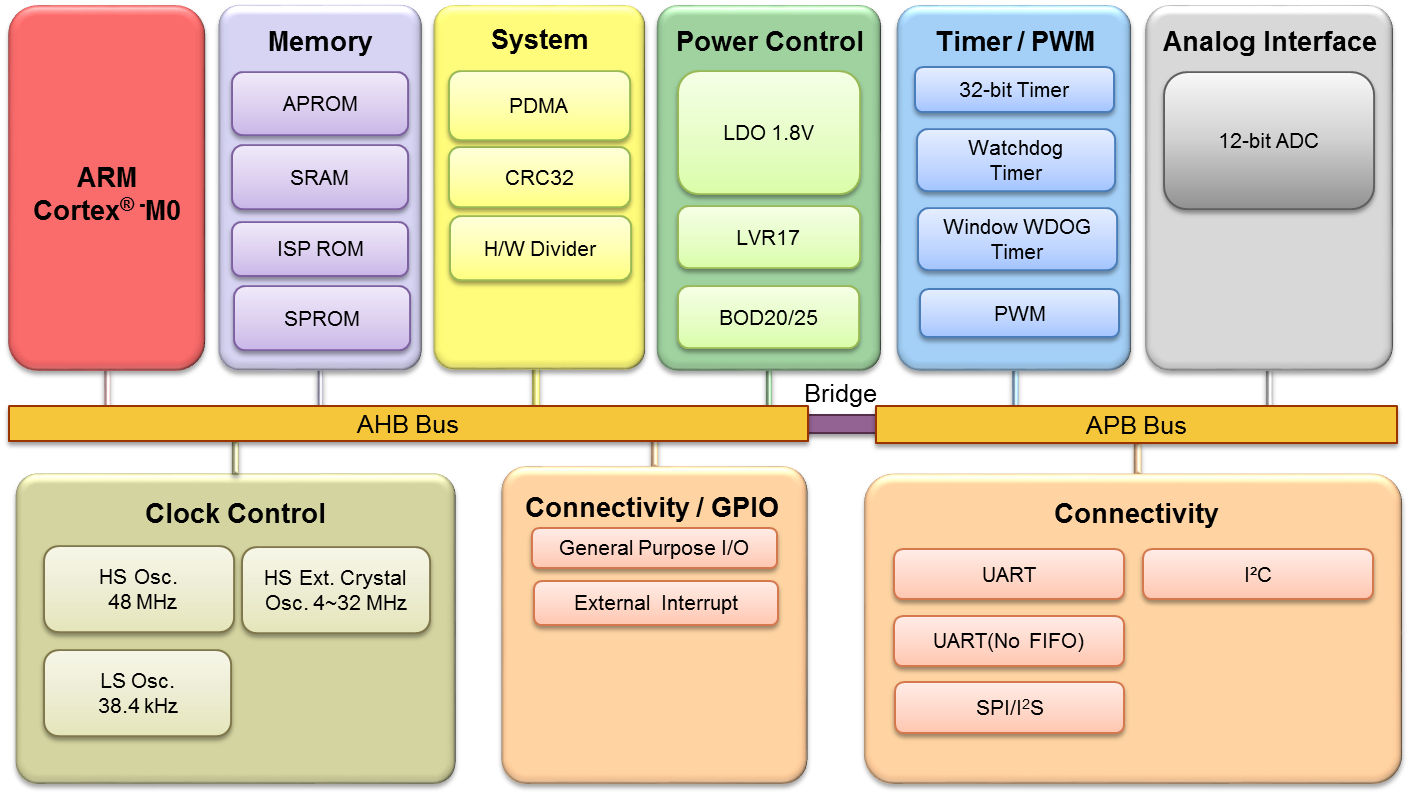

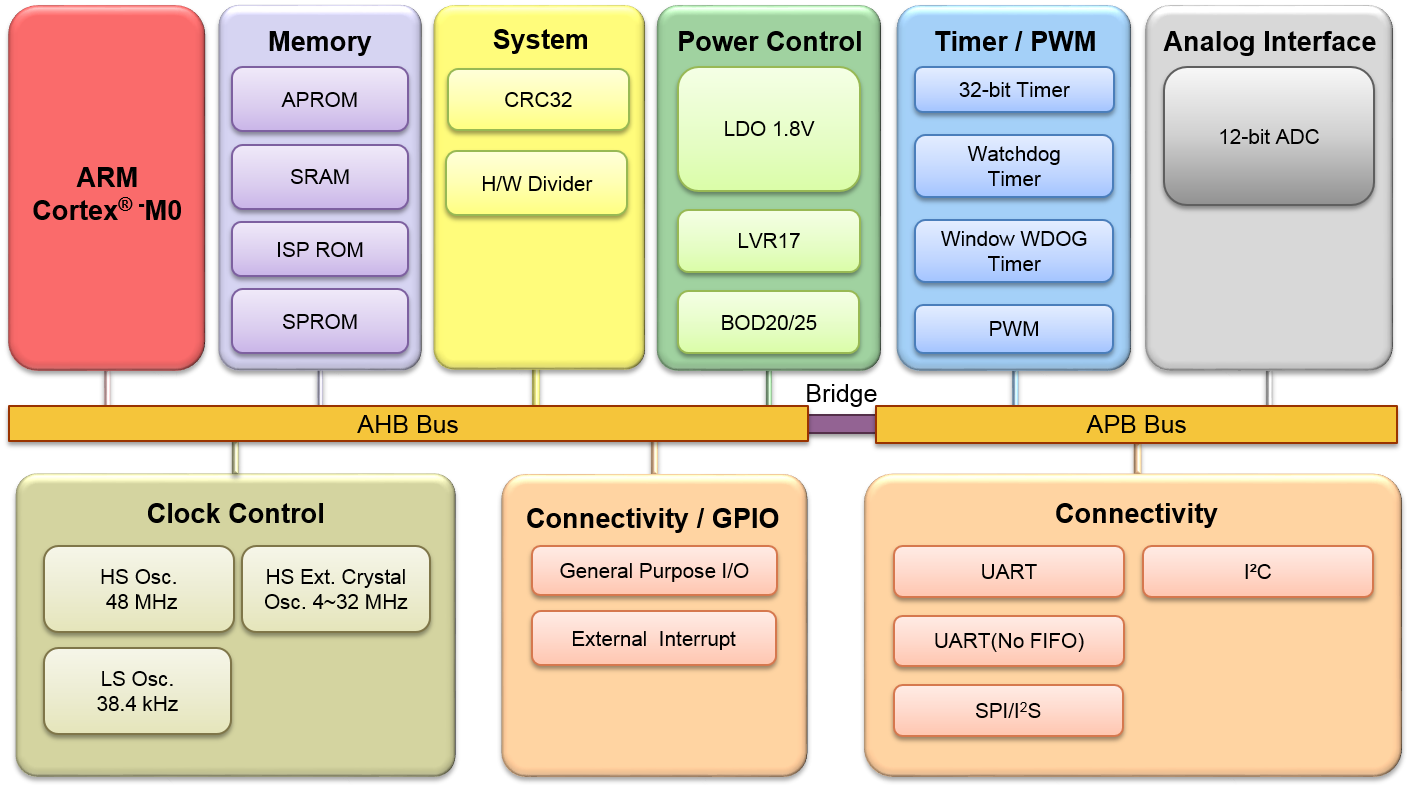

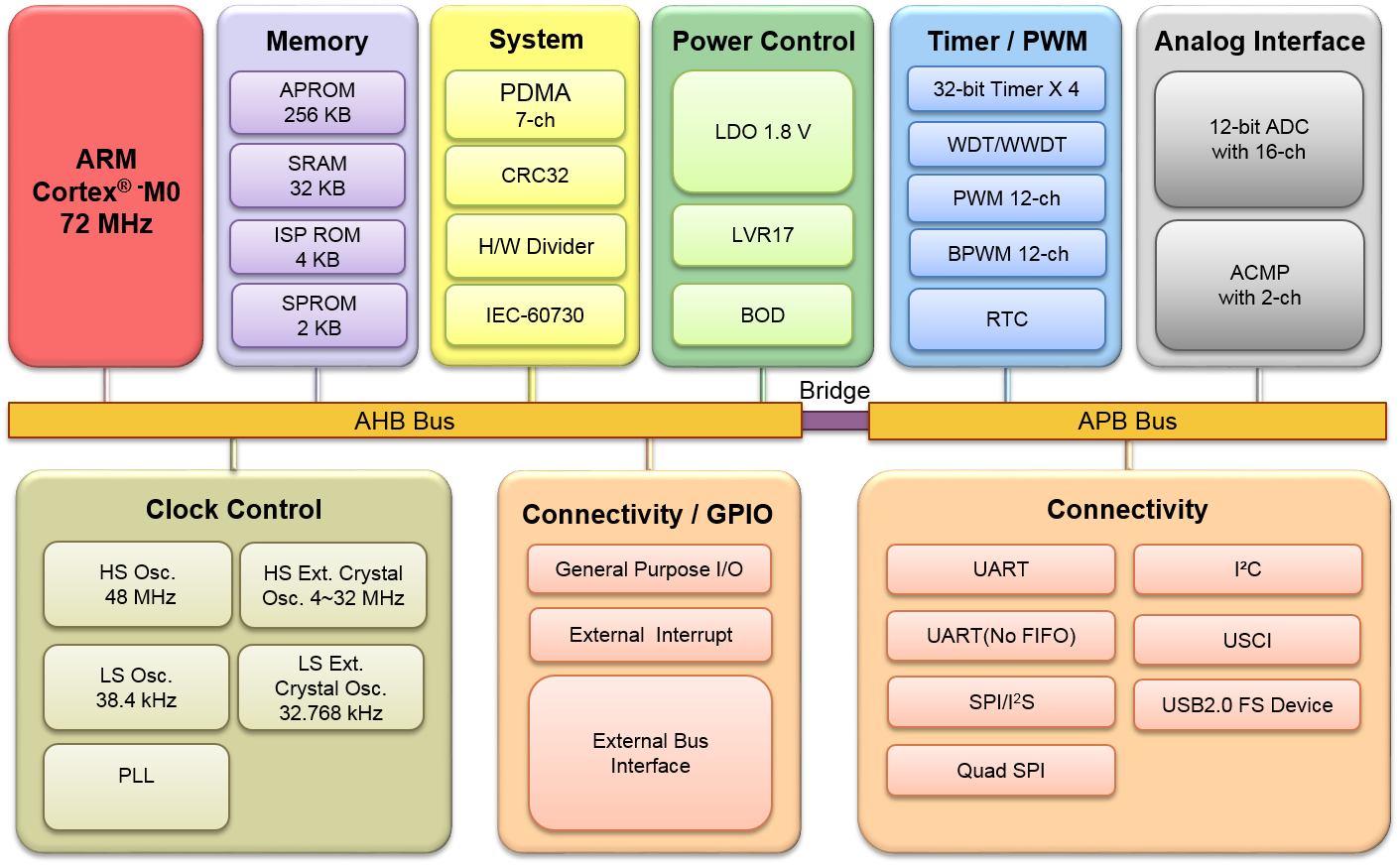

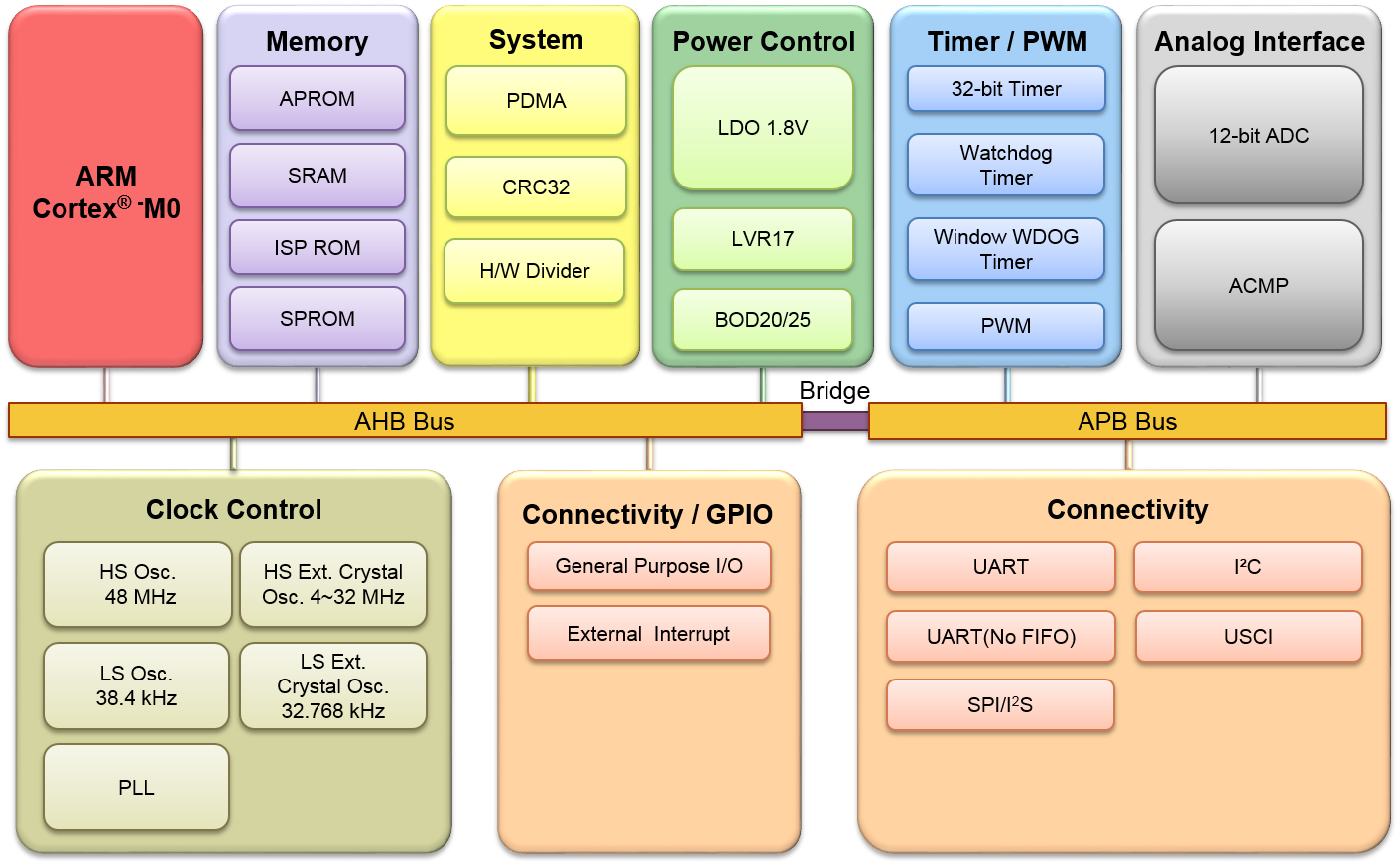

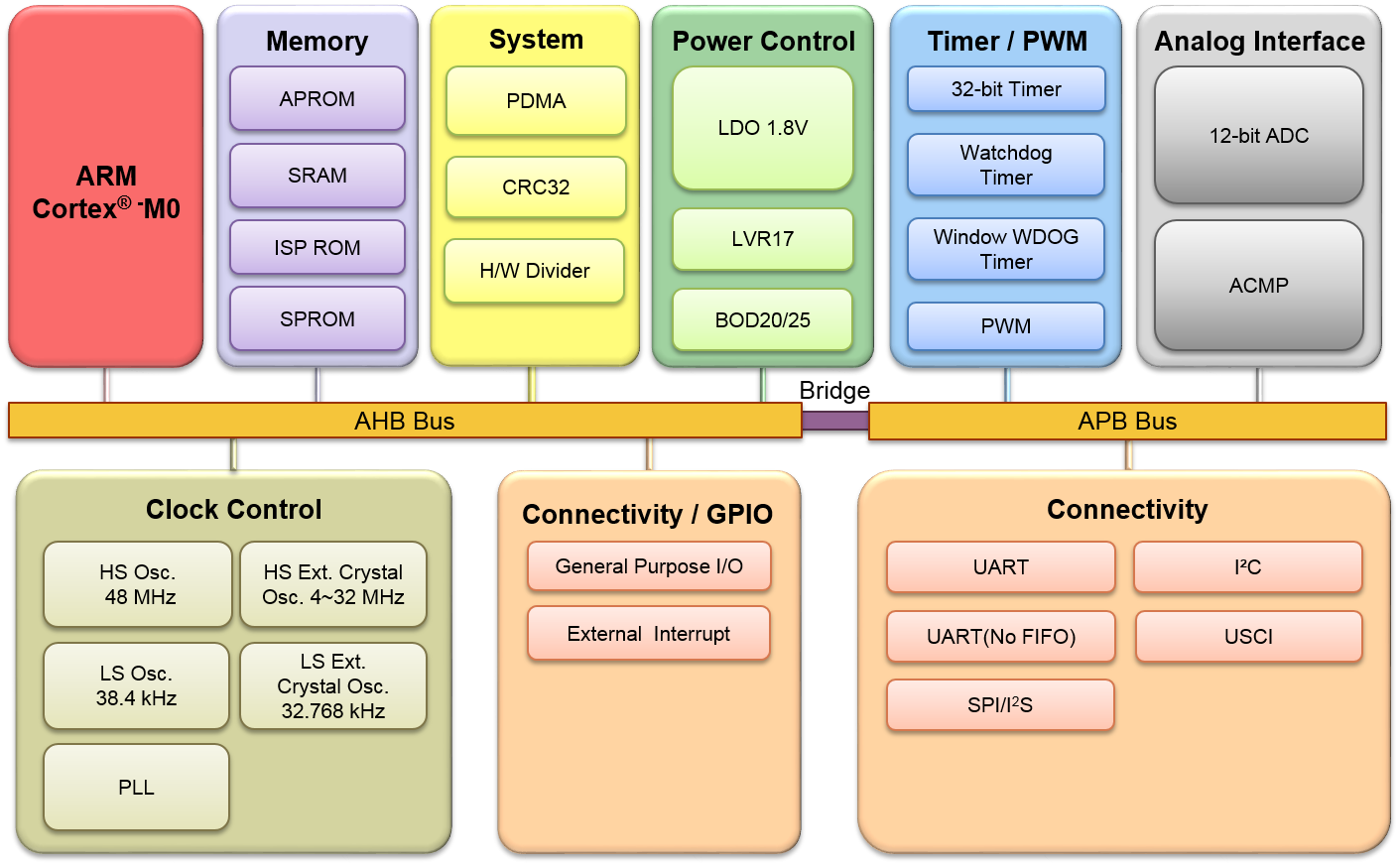

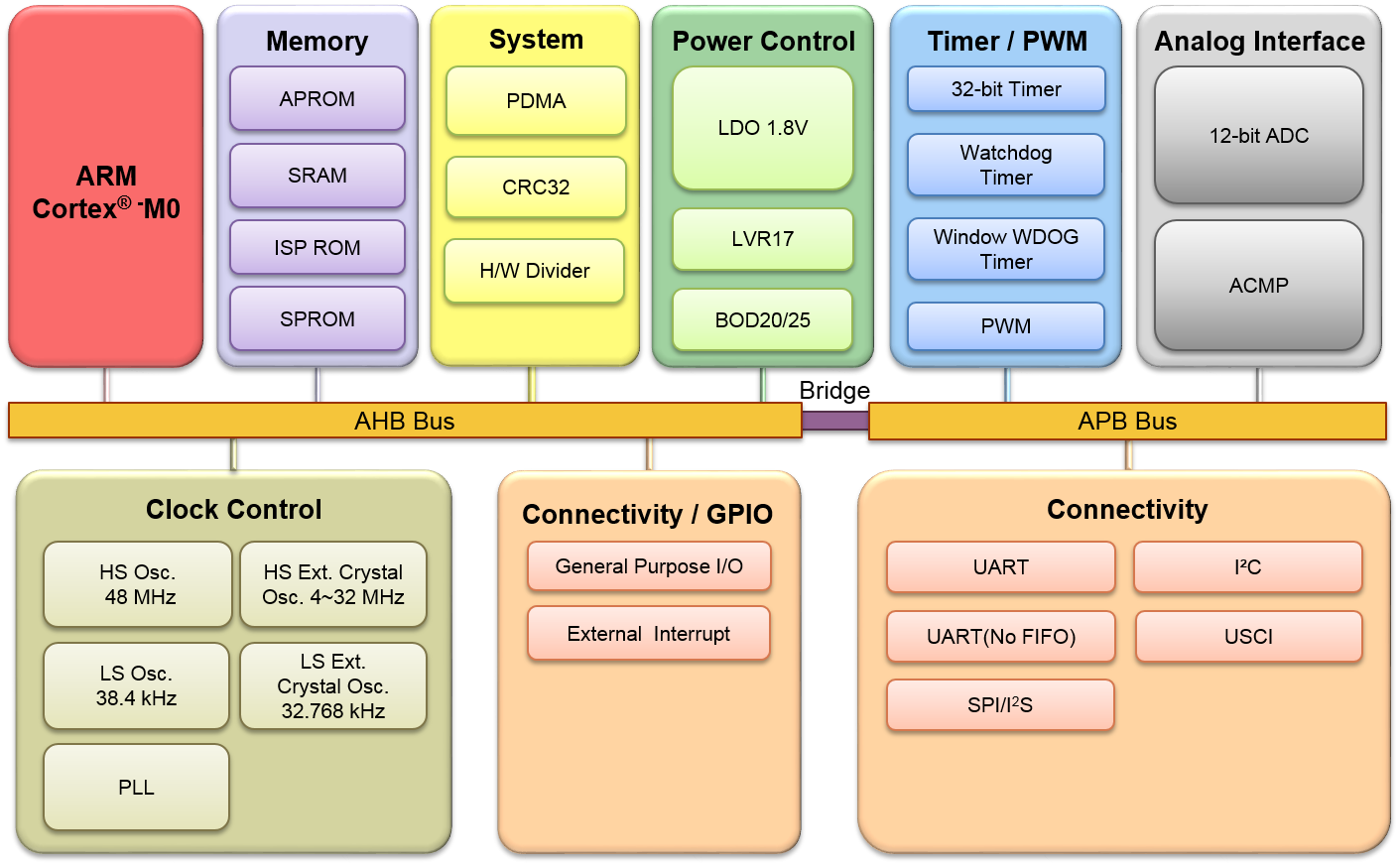

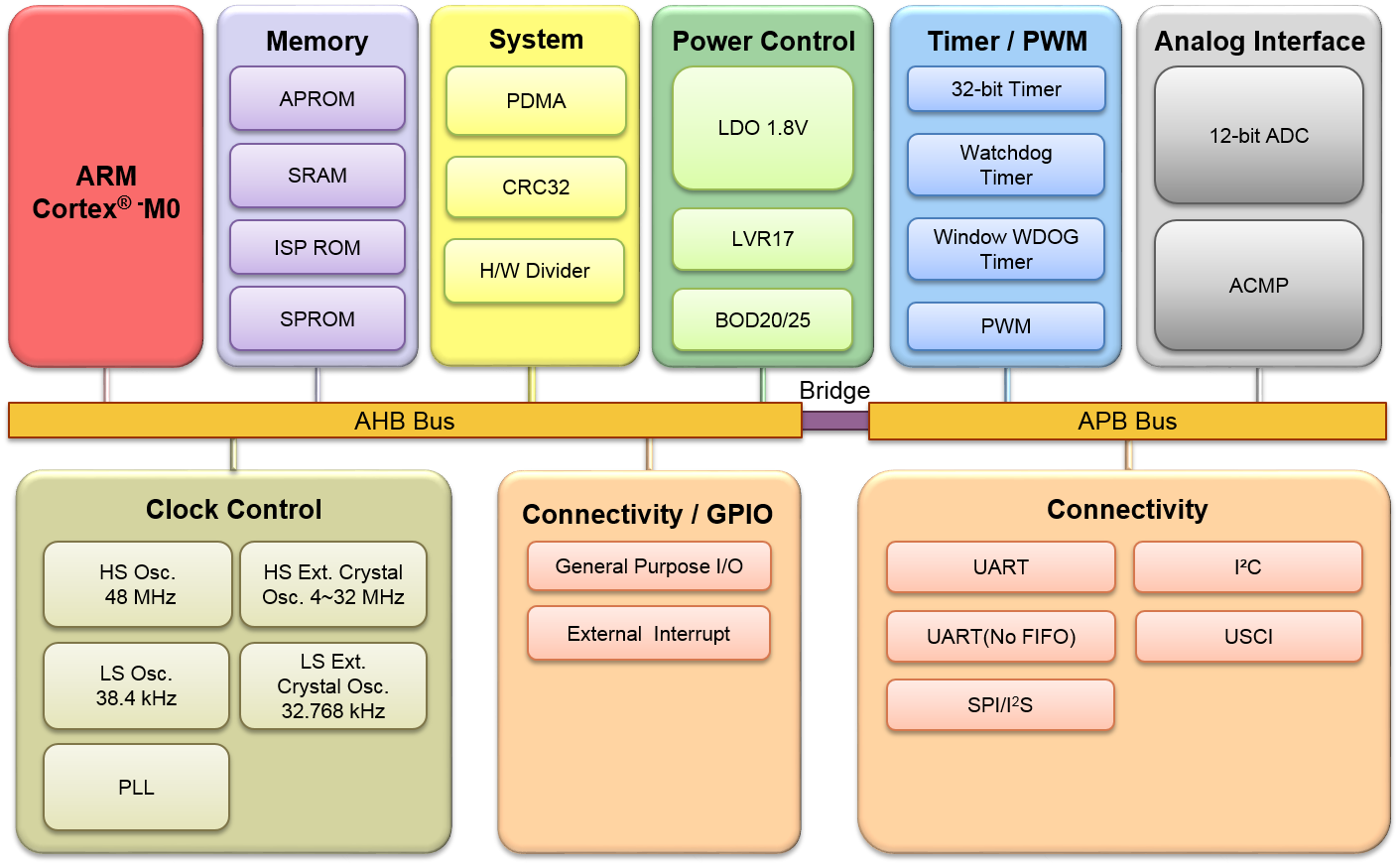

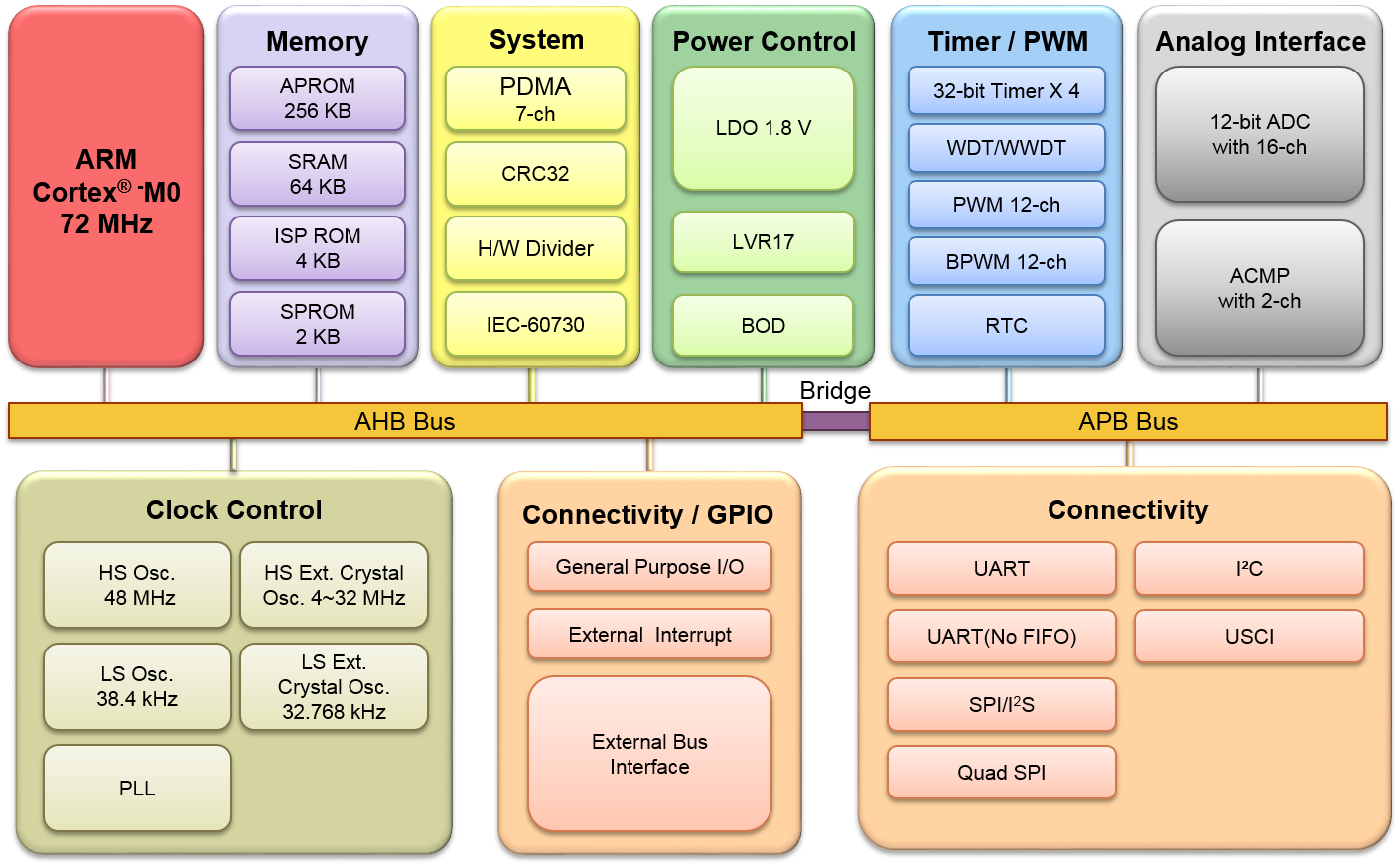

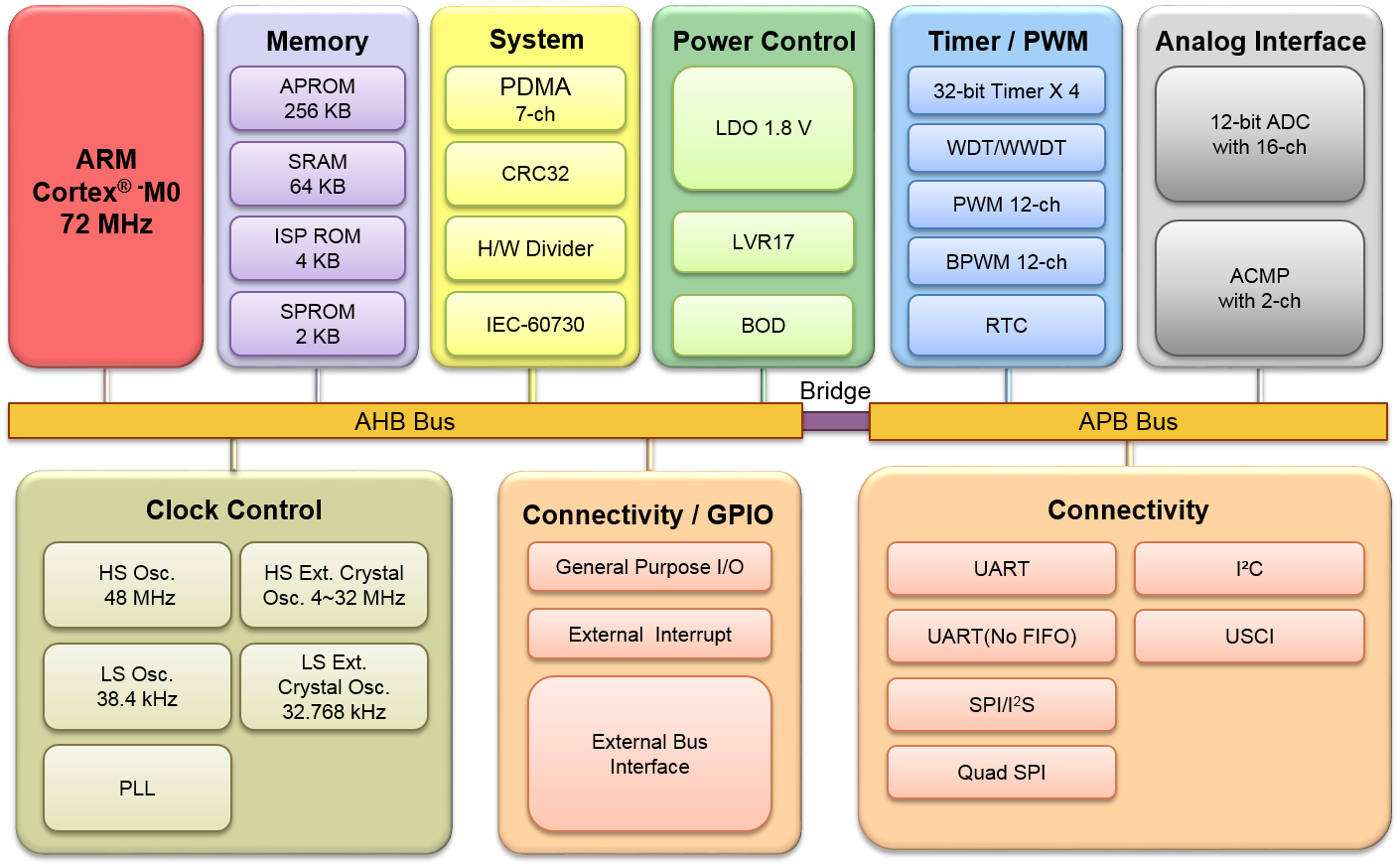

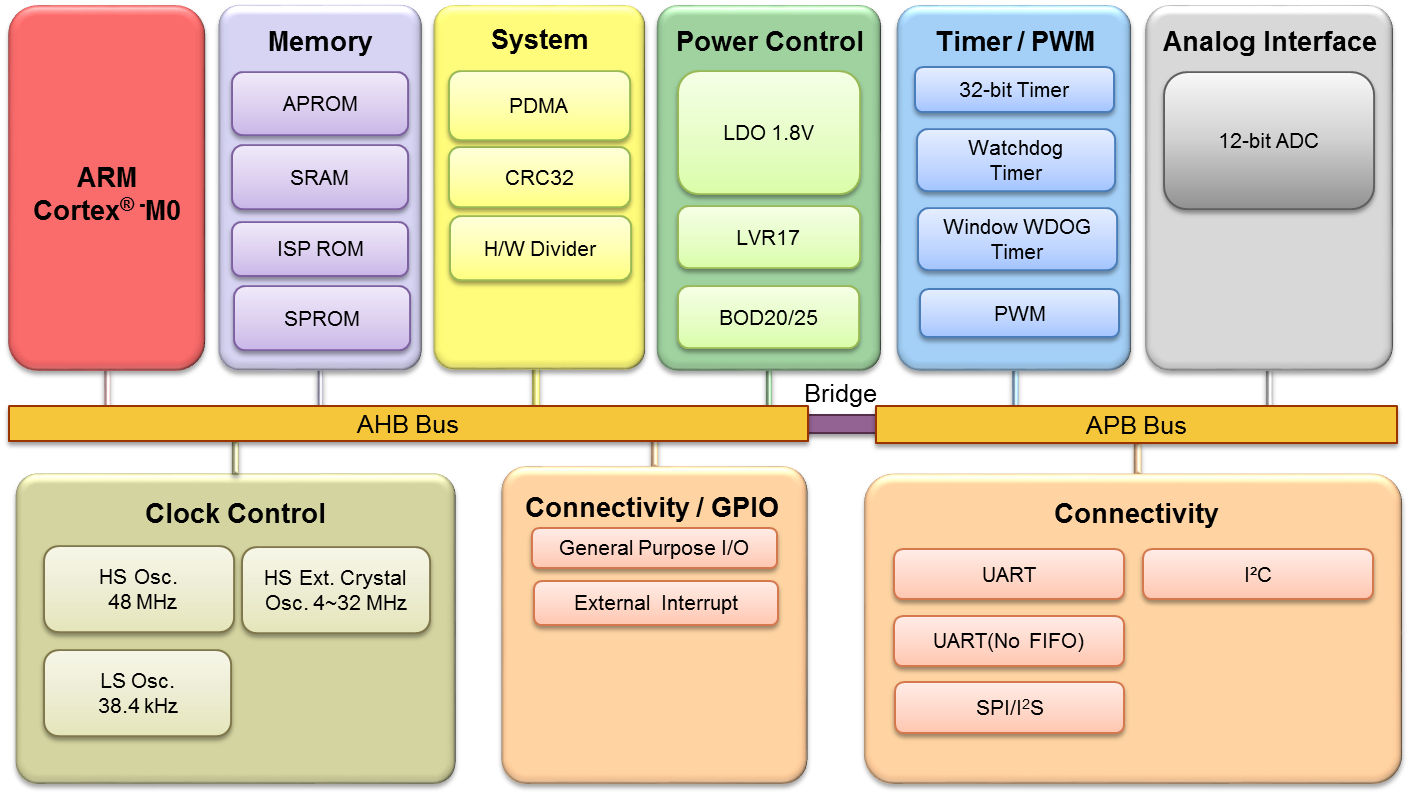

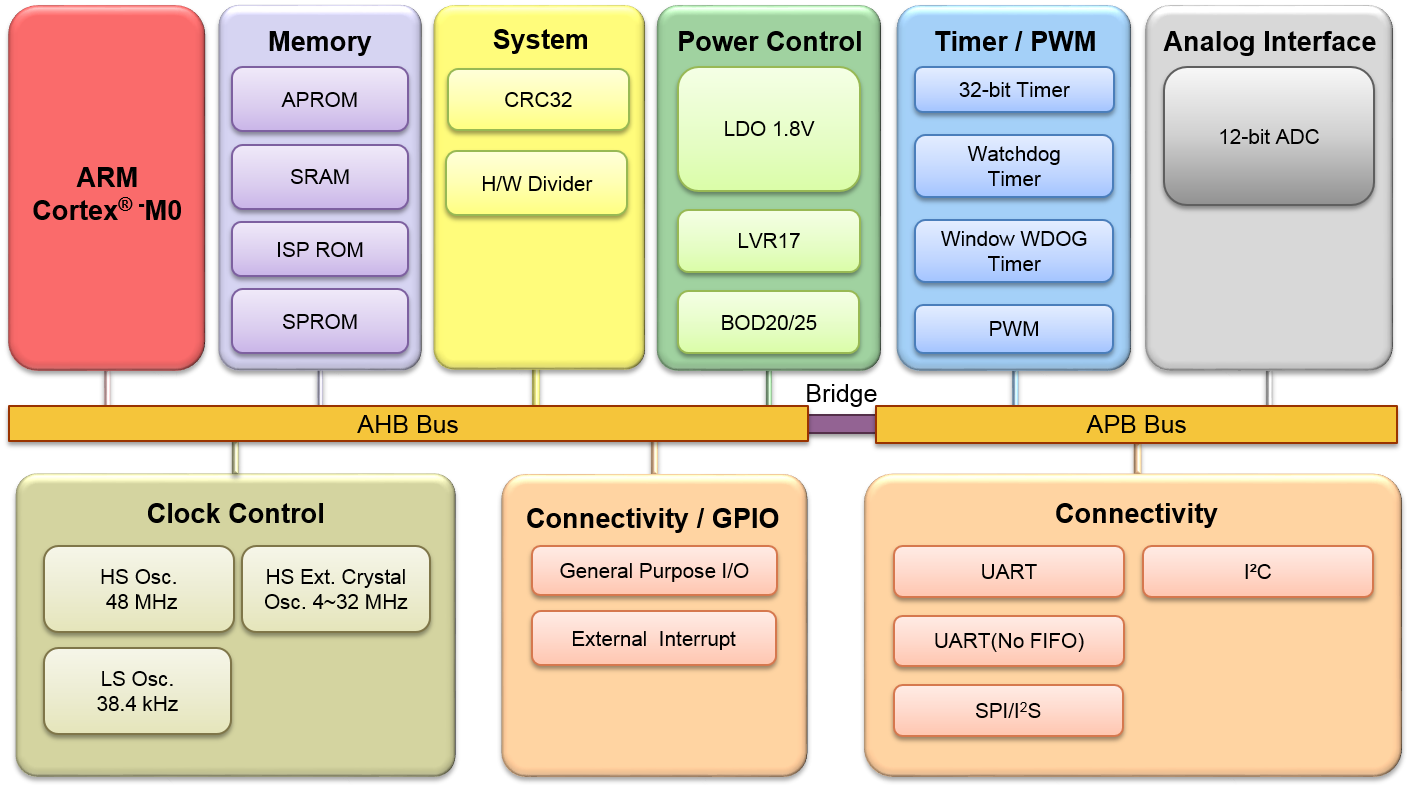

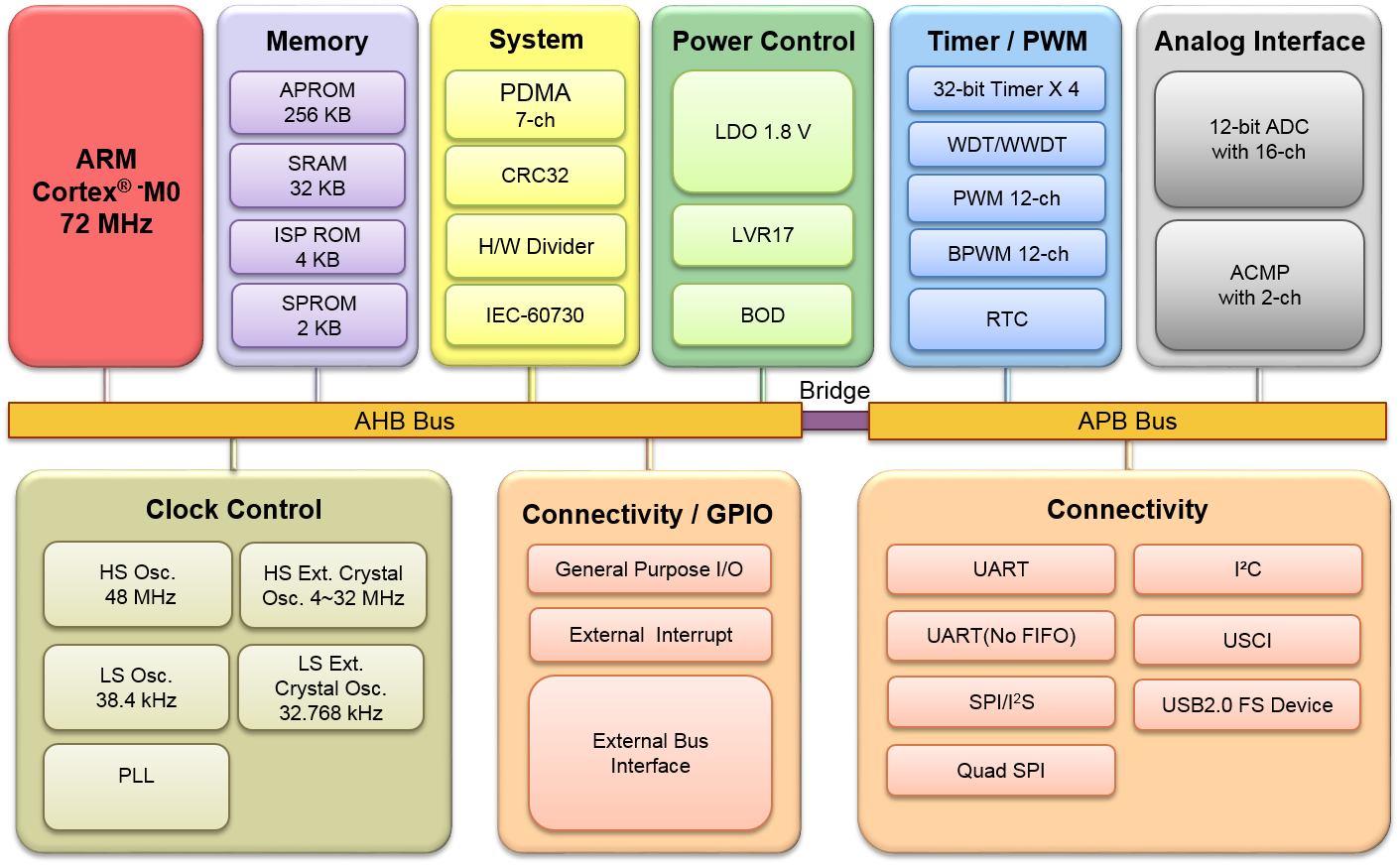

4330 M031TD2AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-28 09:15:16 4148

4148

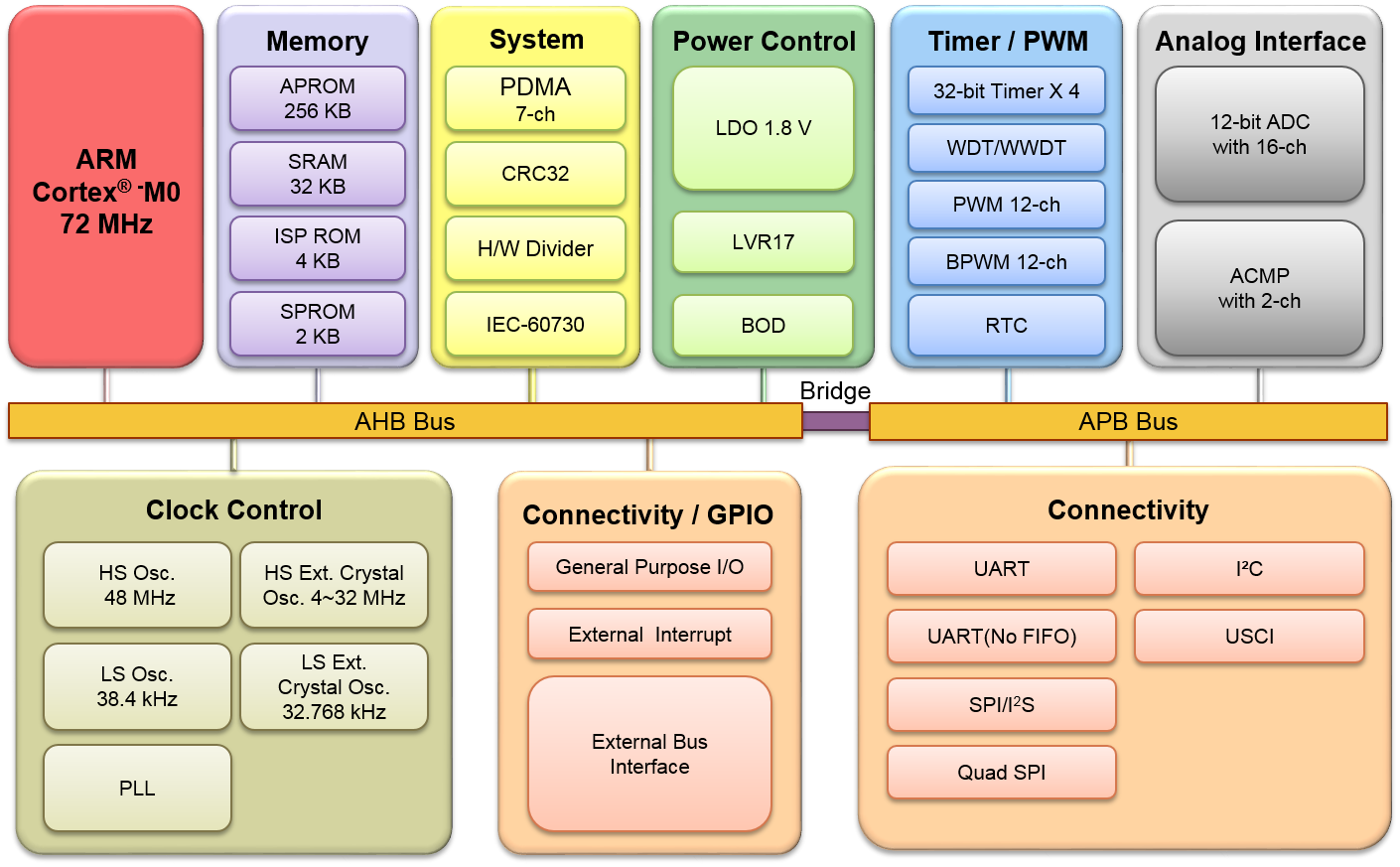

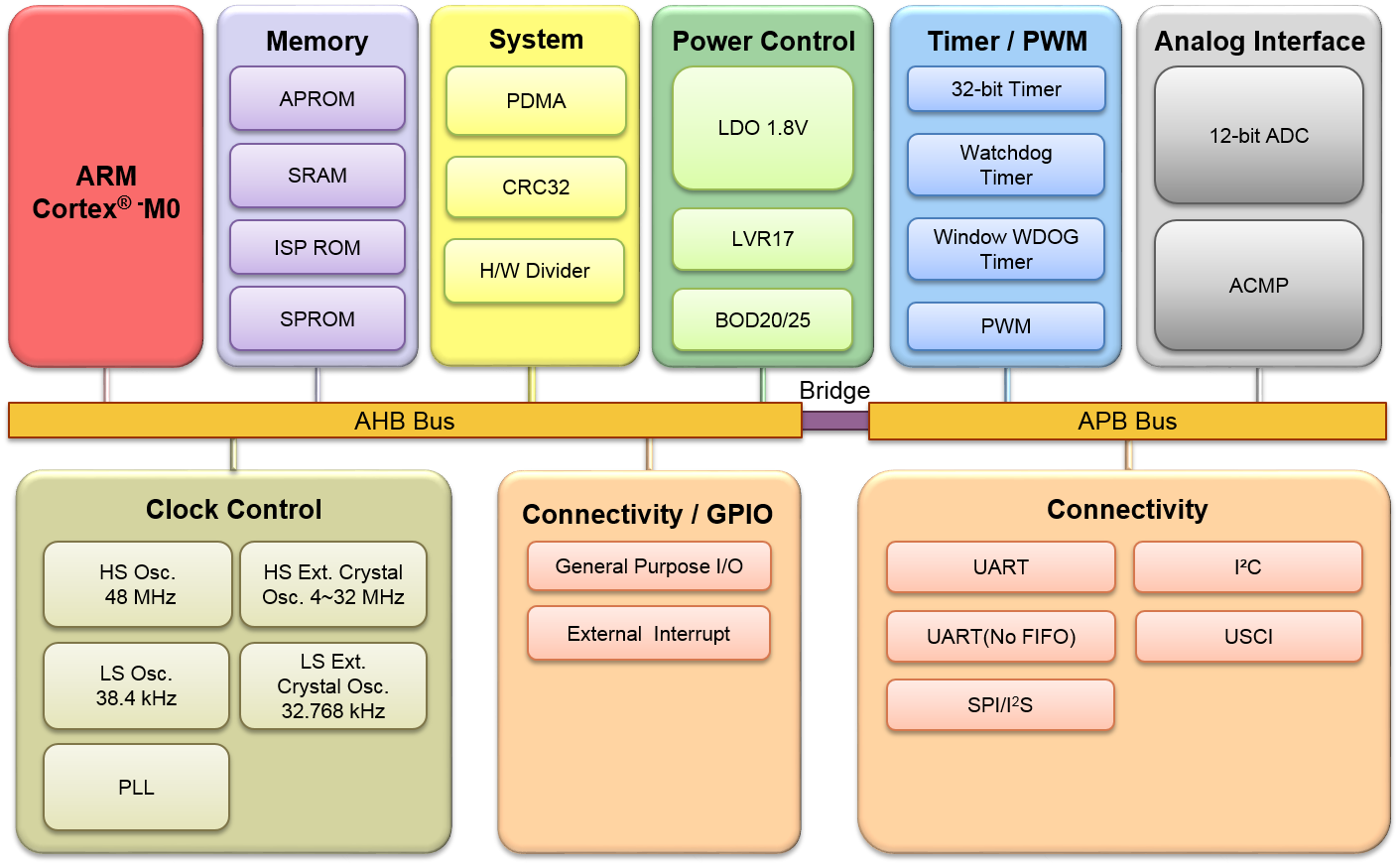

M031TC1AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-28 09:19:10 3263

3263

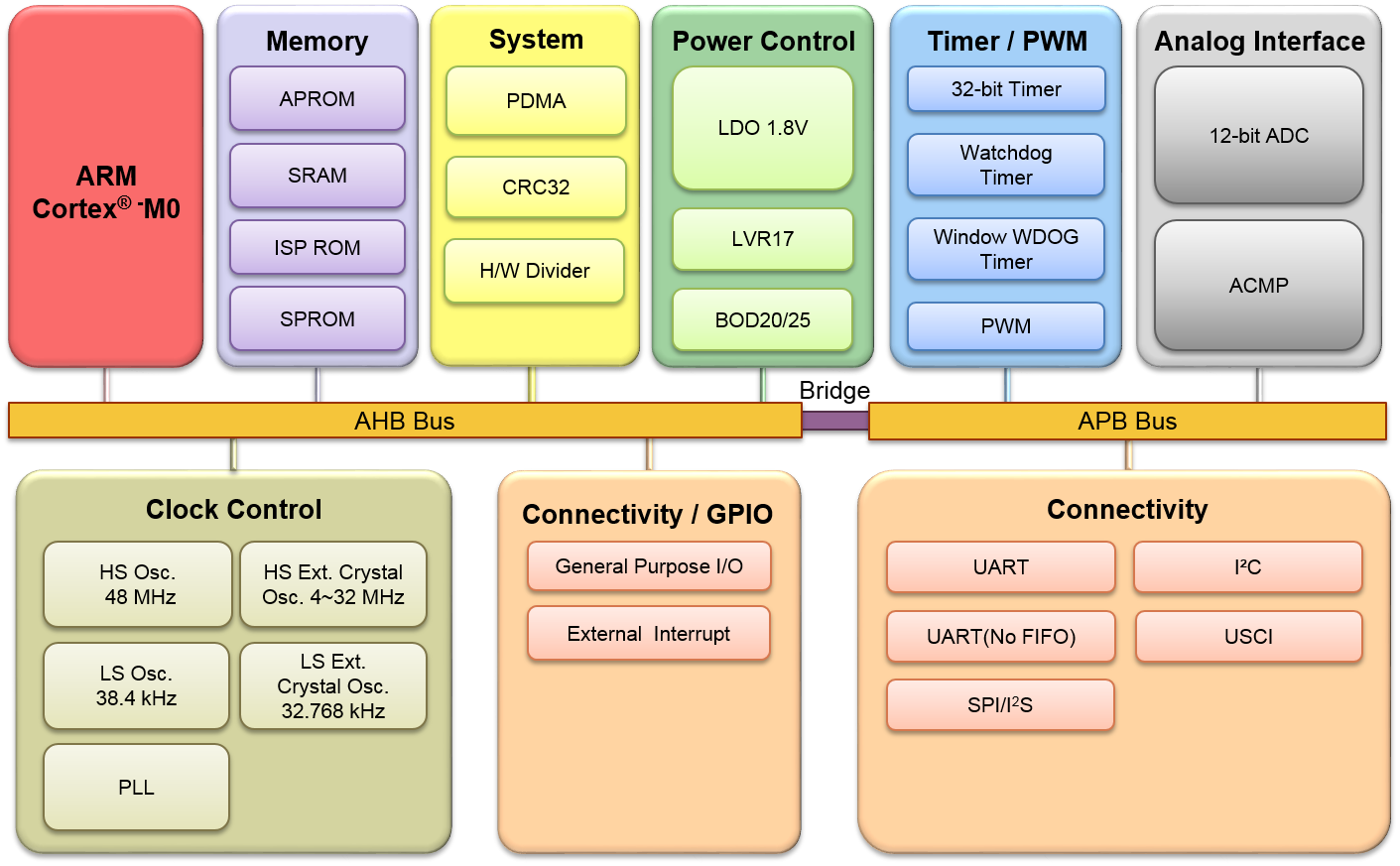

M031SG8AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-28 09:28:27 2420

2420

M031SG6AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-28 09:47:37 2612

2612

M031SE3AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-28 09:33:10 3109

3109

M031SD2AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-28 09:40:07 2707

2707

M031SC2AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-28 09:50:16 2567

2567

M031LE3AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-11-29 17:22:19 3950

3950

M031LD2AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 10:35:27 4361

4361

M031LC2AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 10:48:22 2633

2633

M031KG8AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 10:47:55 2633

2633

M031KG6AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 10:55:35 2528

2528

M031FB0AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 11:03:18 3650

3650

M031EC1AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 10:55:14 3379

3379

M031EB0AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 10:52:42 2757

2757

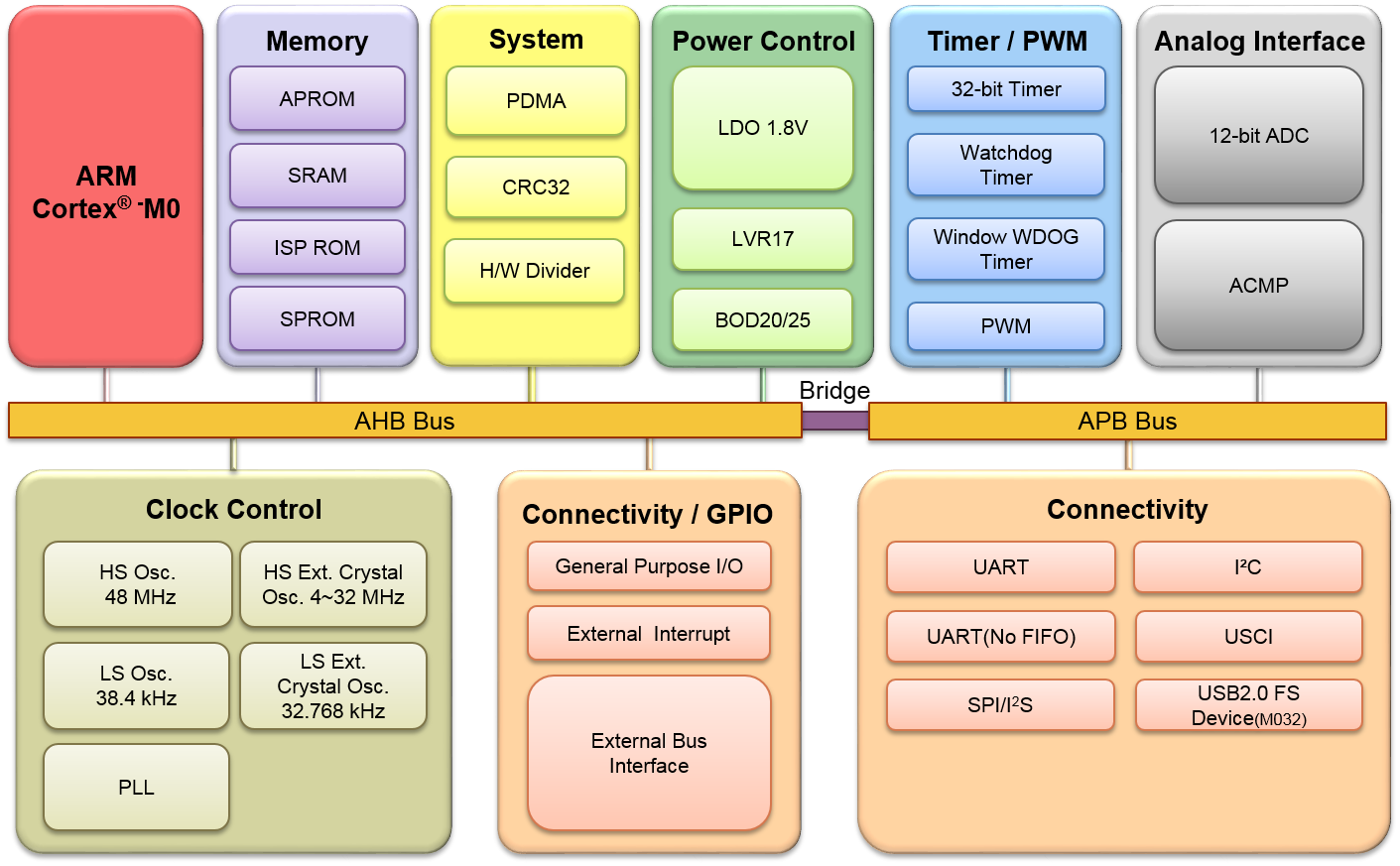

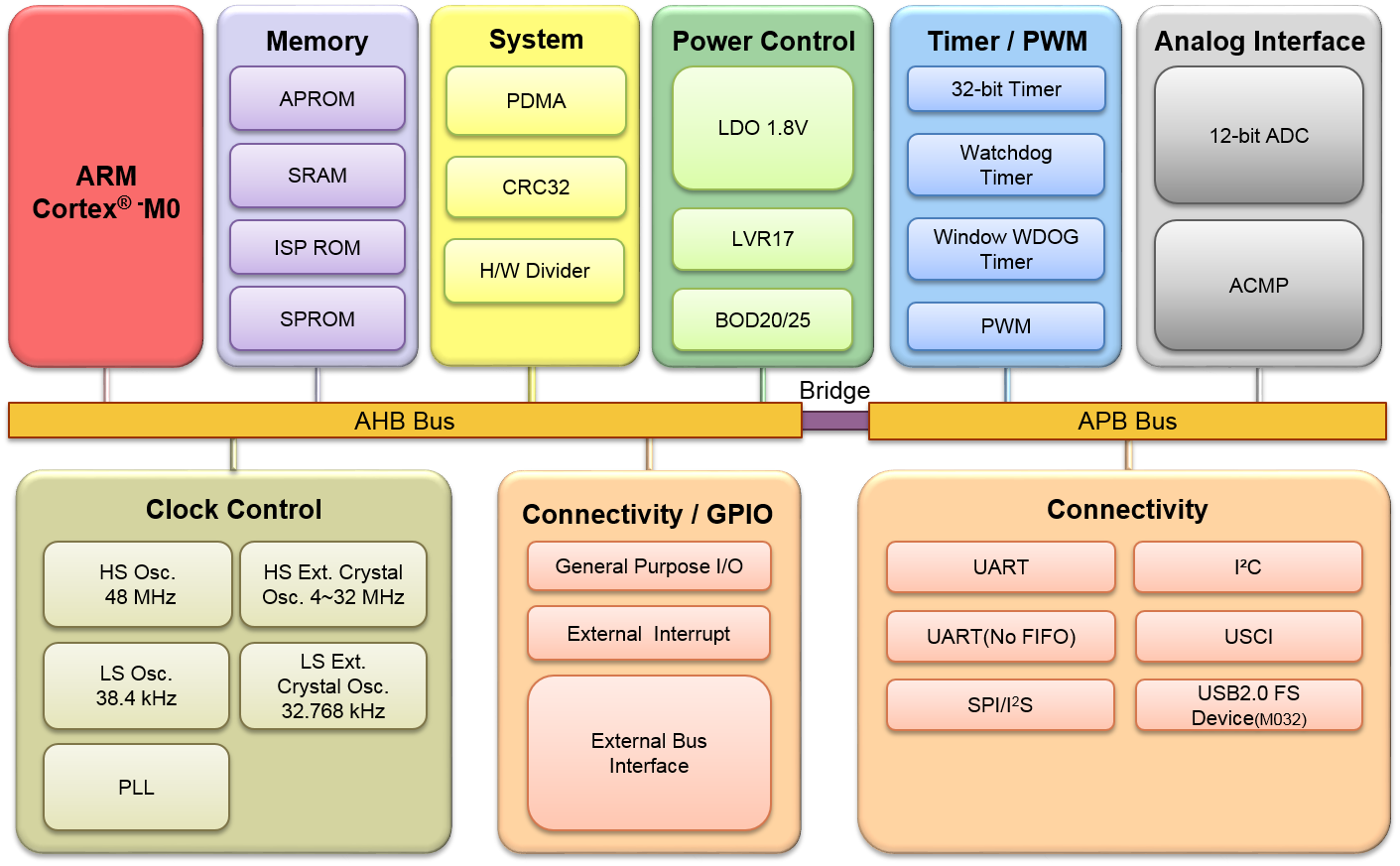

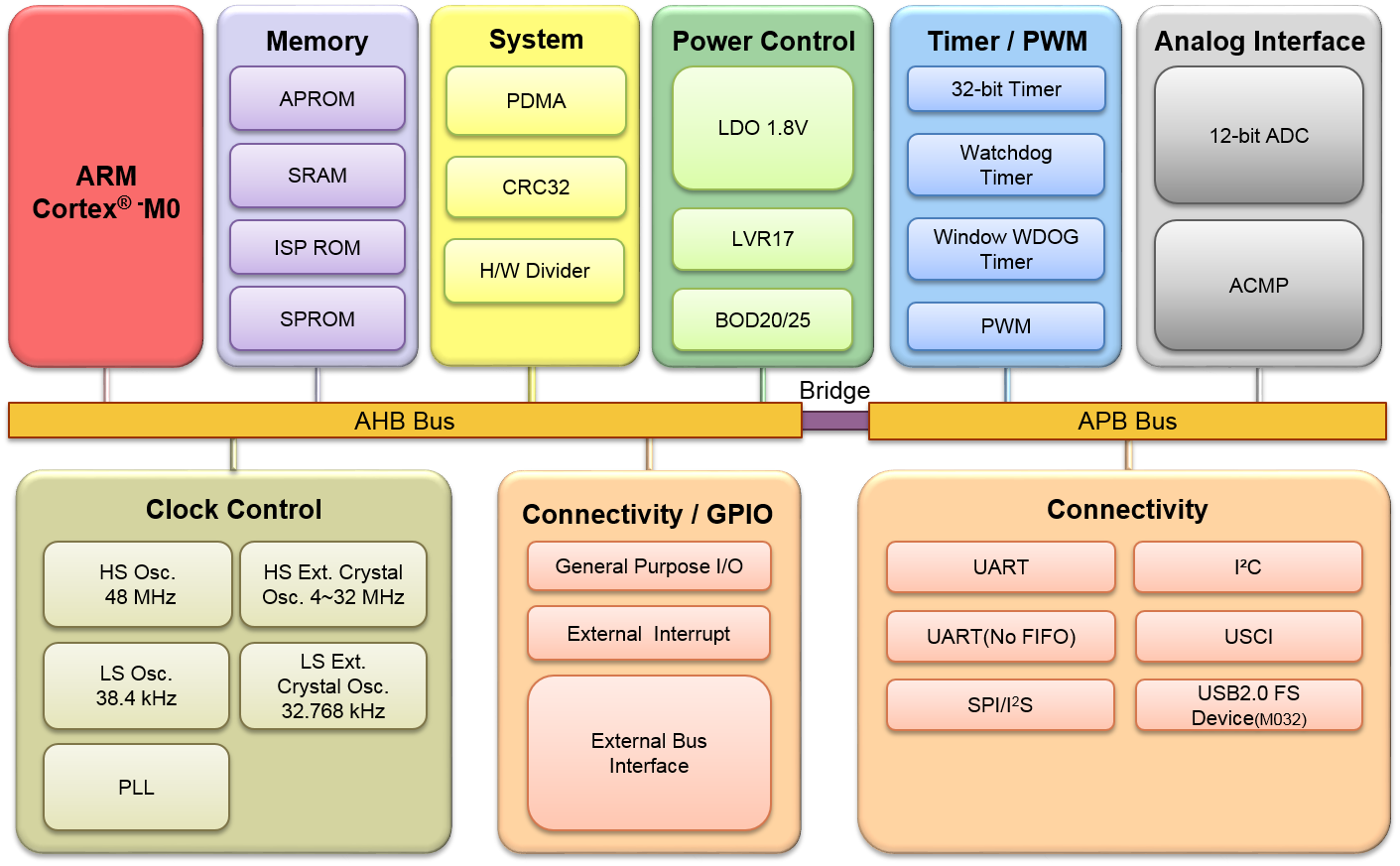

M032KG6AE 是基于 Arm? Cortex?-M0 內核的低工作電壓微控制器,具有 32 位硬件乘法器/除法器。

2019-12-01 10:51:01 2601

2601

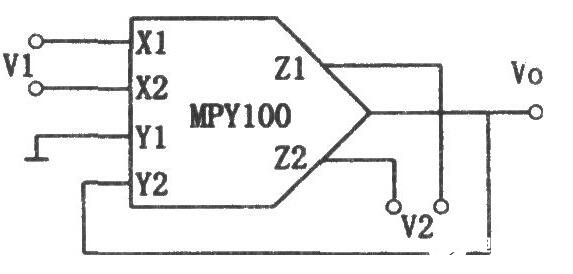

輸入信號為V1、V2,輸出Vo為Vo=10V2/V1。這種除法器是將乘法器接在運算放大器的反院回路組成的。V1的輸入范圍為-0.2V到10V,V2的輸入范圍為-10V到10V。

2019-12-31 14:12:44 22135

22135

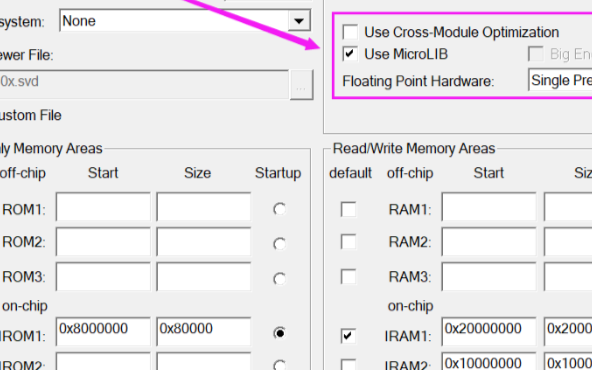

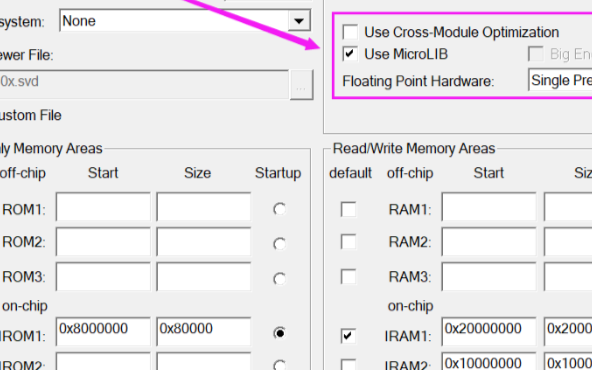

如何正確使用MDK-ARM優化功能,以及優化之后帶來的影響

2020-02-28 15:17:52 9794

9794

乘法、除法、乘方和開方等模擬運算的主要基本單元,而且還廣泛用于電子通信系統作為調制、解調、混頻、鑒相和自動增益控制;另外還可用于濾波、波形形成和頻率控制等場合,因此是一種用途廣泛的功能電路。

2021-02-18 15:08:01 28128

28128

AD533:低成本乘法器、除法器、平方器、平方器、根過時數據表

2021-04-30 21:05:33 3

3 AD533:低成本乘法器、除法器、平方器、平方根過時數據表

2021-05-07 10:50:33 20

20 AD734:10 MHz四象限乘法器/除法器數據表

2021-05-15 10:18:05 12

12 簡化合成器的有源乘法器和除法器

2021-05-16 17:15:02 9

9 4.3 實例九 除法器設計4.3.1. 本章導讀要求掌握除法器原理,并根據原理設計除法器模塊以及設計對應的測試模塊,最后在 Robei可視化仿真軟件經行功能實現和仿真驗證。設計原理這個除法器的設計為

2021-11-07 10:51:04 18

18 匯編實現多字節乘除法乘法單片機的乘法本質是二進制的乘法,而乘法本身是通過加法實現的。多字節的乘法其實就是移位做加法。例如7x11,用二進制豎式表示如下圖:可以看到,其實就是判斷乘數的每一位是1還是0

2021-11-15 17:21:03 21

21 FPGA中的硬件邏輯與軟件程序的區別,相信大家在做除法運算時會有深入體會。若其中一個操作數為常數,可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結構復雜,且通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。

2022-04-27 09:16:03 9041

9041 單精度矩陣乘法(SGEMM)幾乎是每一位學習 CUDA 的同學繞不開的案例,這個經典的計算密集型案例可以很好地展示 GPU 編程中常用的優化技巧。本文將詳細介紹 CUDA SGEMM 的優化手段

2022-09-28 09:46:54 2686

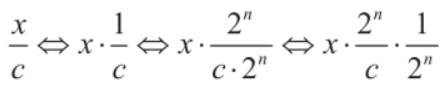

2686 在學習 Andorid 逆向的過程中,發現無論是哪種編譯器,生成哪個平臺的代碼,其優化思路在本質上如出一轍,在 Windwos 平臺所使用的技巧,在安卓平臺仍然適用,不外乎乘法除法計算的優化

2023-02-01 16:25:25 1442

1442 在學習 Andorid 逆向的過程中,發現無論是哪種編譯器,生成哪個平臺的代碼,其優化思路在本質上如出一轍,在 Windwos 平臺所使用的技巧,在安卓平臺仍然適用,不外乎乘法除法計算的優化

2023-02-01 16:25:27 1363

1363

python數字除法包括真除法(/)和floor除法(//),并且跟python版本相關。

2023-03-10 10:03:18 1874

1874 使用IAR IDE仿真RL78內置硬件乘法器和除法器注意事項

2023-10-30 17:04:14 2226

2226

電子發燒友App

電子發燒友App

評論