1、IAR IDE

IAR一直是Renesas強有力的合作伙伴,IAR IDE支持Renesas全系列MCU的開發和調試。IAR Embedded Workbench是一個完整的開發工具鏈,在易于使用的集成開發環境中提供了強大的代碼優化和全面的調試功能。

2、Renesas RL78系列MCU

Renesas RL78系列MCU是Renesas 16-bit低功耗產品線,專為超低功耗設計,可以為客戶提供以較低的成本建立高集成度和高效節能的應用平臺。

RL78系列MCU有三大主要特點:

1)低功耗:最低46uA/MHz

2)可擴展性:1KB~512KB Flash

3)高效:最高1.39DMIPS/MHz

此外,RL78系列MCU具有超級全面的產品線,同時也在不斷地推進新產品的開發,以滿足客戶未來的產品升級需求。

3、使用IAR IDE仿真RL78內置硬件乘法器 除法器注意事項

在使用IAR IDE進行RL78系列MCU仿真調試時,可執行硬件仿真或軟件仿真(Simulator),但是,如果需要應用硬件乘法器/除法器,則必須使用硬件仿真,不能使用軟件仿真(Simulator),軟件仿真(Simulator)不支持MCU內部的硬件乘法器/除法器。

當執行硬件仿真時,如果不勾選“Disable Hardware Multiplier/Divider Unit”:

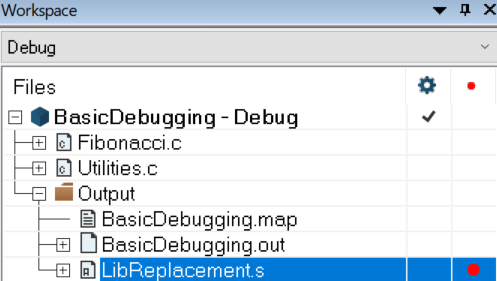

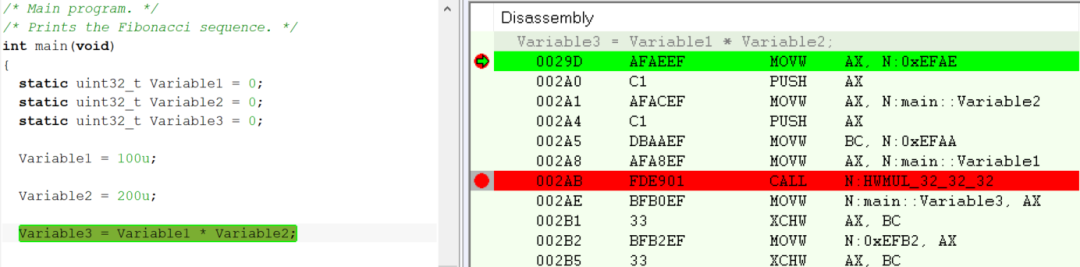

對應的乘法操作會調用函數HWMUL_32_32_32,(HWMUL_32_32_32存在于工具自動生成的文件LibReplacement.s中,當不勾選“Disable Hardware Multiplier/Divider Unit”時,會自動在Output文件夾生成LibReplacement.s文件),例如:

在程序中可以看到:

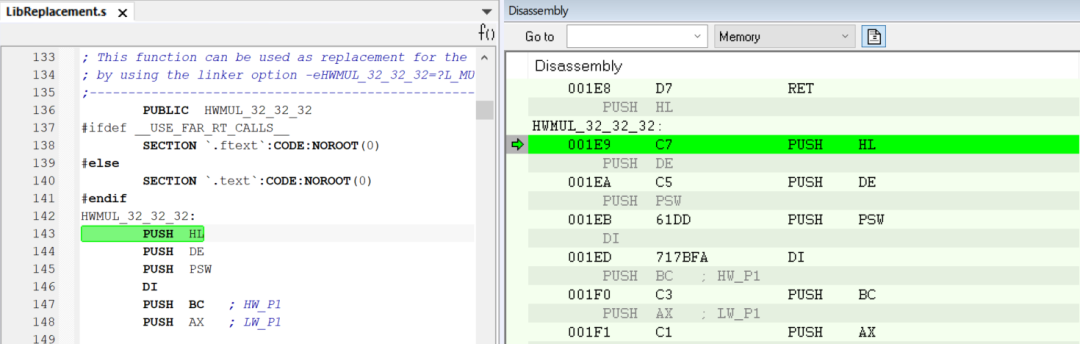

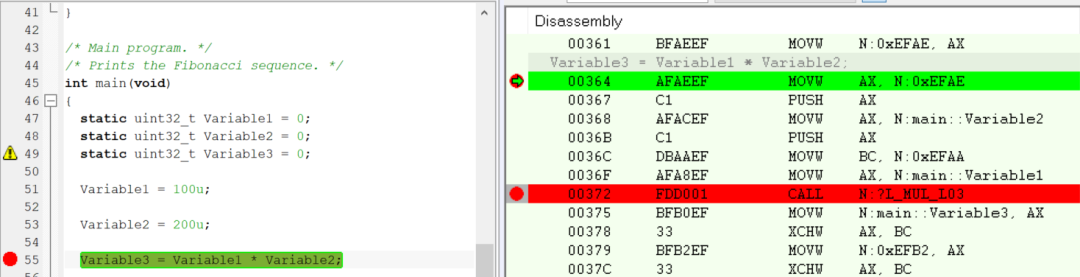

當勾選“Disable Hardware Multiplier/Divider Unit”時,編譯器會選擇對應的軟件乘法庫函數L_MUL_L03來實現乘法操作:

需要注意的是,軟件乘法庫函數L_MUL_L03相對于HWMUL_32_32_32函數會需要更多的資源及運行時間。

來源:瑞薩MCU小百科

審核編輯:湯梓紅

-

mcu

+關注

關注

147文章

19036瀏覽量

401453 -

仿真

+關注

關注

55文章

4518瀏覽量

138576 -

IAR

+關注

關注

5文章

414瀏覽量

38632 -

IDE

+關注

關注

0文章

368瀏覽量

49177 -

除法器

+關注

關注

2文章

15瀏覽量

14141

發布評論請先 登錄

硬件乘法器的相關資料分享

并行除法器 ,并行除法器結構原理是什么?

進位保留Barrett模乘法器設計

使用verilogHDL實現乘法器

乘法器原理_乘法器的作用

使用IAR IDE仿真RL78內置硬件乘法器和除法器注意事項

使用IAR IDE仿真RL78內置硬件乘法器和除法器注意事項

評論