一門知識。 設(shè)計原理: 本次的設(shè)計主要是一個簡單的二選一數(shù)據(jù)選擇器,我們的設(shè)計主 二進制中只有 0 和 1 兩個狀態(tài),可以表示 0、1 兩種狀態(tài)的電 子器件很多,如開關(guān)的接通和斷開, 晶體管 的導(dǎo)通和截止、磁元 件的正負剩磁、電位電

2018-09-20 09:38:39 17151

17151

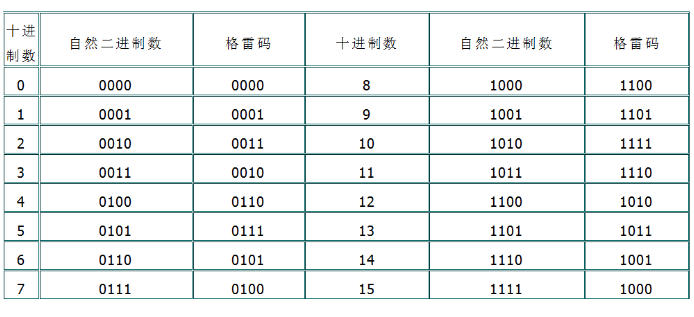

其中采用循環(huán)二進制編碼的絕對式編碼器,其輸出信號是一種數(shù)字排序,不是權(quán)重碼,每一位沒有確定的大小,不能直接進行比較大小和算術(shù)運算,也不能直接轉(zhuǎn)換成其他信號,要經(jīng)過一次碼變換,變成自然二進制碼。

2020-09-23 16:23:04 7514

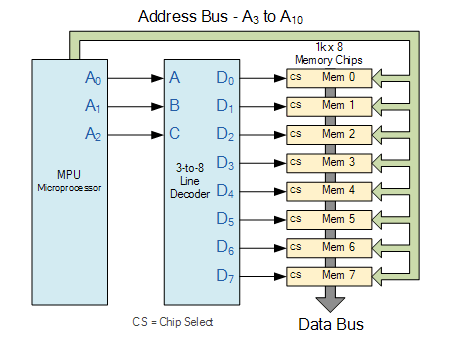

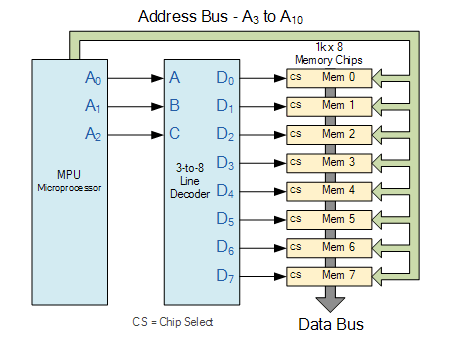

7514 二進制解碼器是由單獨的邏輯門構(gòu)成的另一種組合邏輯電路,與編碼器完全相反。名稱“解碼器”是指將編碼信息從一種格式轉(zhuǎn)換或解碼為另一種格式,因此二進制解碼器使用2 n個輸出將“ n”個二進制輸入信號轉(zhuǎn)換

2020-12-29 12:10:32 12415

12415

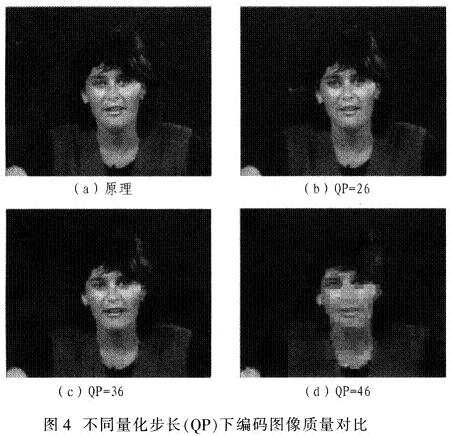

物體的形狀,于是,在每個宏塊中可包含有1、2、4、8或16個運動矢量。 多參數(shù)幀估計 在H.264中,可采用多個參數(shù)幀的運動估計,即在編碼器的緩存中存有多個剛剛編碼好的參數(shù)幀,編碼器從其中選擇一個給出

2008-06-04 14:29:02

h.264協(xié)議中文版下載 訪問單元:AC變換系數(shù):自適應(yīng)二進制算術(shù)解碼過程:自適應(yīng)二進制算術(shù)編碼過程...中英文版,直接翻譯的。。還能讓你學(xué)習(xí)學(xué)習(xí)英語。。。不錯哦。。。。下了記得頂一頂了

2008-05-30 17:48:51

。而絕對式編碼器是直接輸出數(shù)字量的傳感器,它是利用自然二進制或循環(huán)二進制(格雷碼)方式進行光電轉(zhuǎn)換的,編碼的設(shè)計一般是采用自然二進制碼、循環(huán)二進制碼、二進制補碼等。特點是不要計數(shù)器,在轉(zhuǎn)軸的任意位置

2011-03-08 14:16:59

/davinciedu.html成都宇鴻科技是一家在TI DAVINCI 平臺專注3G和視頻編解碼算法優(yōu)化和實現(xiàn)的公司,是國內(nèi)少數(shù)能整體提供嵌入式3G, H.264超低碼率編碼器,基于VPN的視頻聯(lián)網(wǎng)傳輸平臺的公司之一

2009-12-02 14:10:03

用verilog實現(xiàn)變量flag為1表示變量a的數(shù)值中二進制1的個數(shù)是奇數(shù),flag為0表示變量a的數(shù)值中二進制1的個數(shù)是偶數(shù),比如:a為8’b1111_0000,則二進制1的個數(shù)為4,即偶數(shù)

2023-08-15 10:42:24

文件名 -coding 7 -t 2 -w 320 -h 240其中-t 2是表示進行編碼動作。這是編譯好的二進制文件,可以直接push進系統(tǒng)測試。你猜對了,這個文件也一樣具有之前帖子提到的裸碼流解碼功能。

2015-02-10 18:02:25

在LABVIEW中使用二進制讀寫節(jié)點時,遇到一個奇怪的問題,當(dāng)我通過新建文件創(chuàng)建二進制文件(見第一張圖),之后將數(shù)據(jù)寫入到二進制文件中(見第二張圖),最后讀取二進制文件(見第三張圖)。現(xiàn)在問題是當(dāng)我

2017-09-30 15:03:01

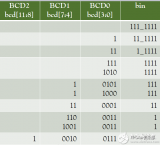

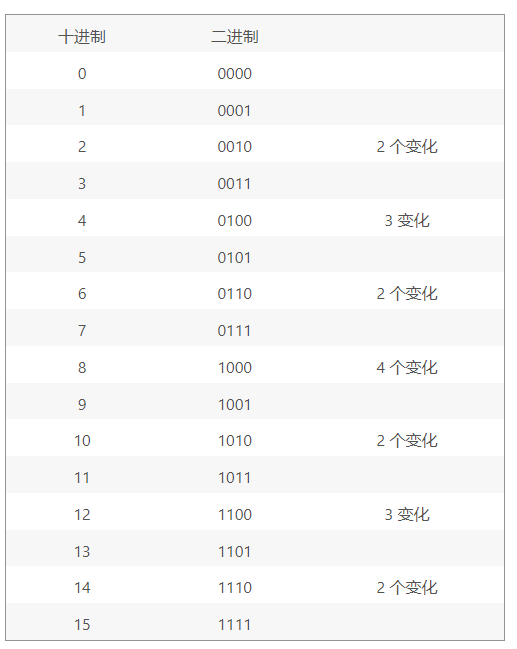

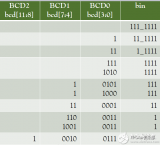

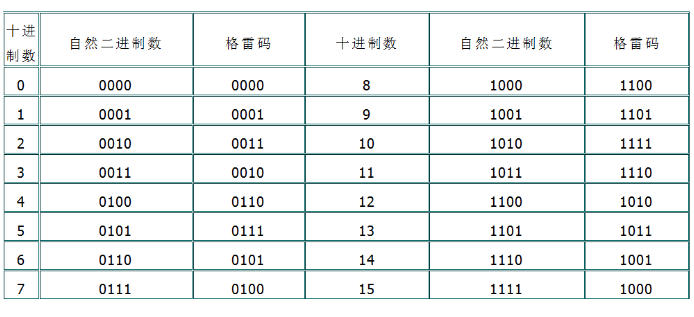

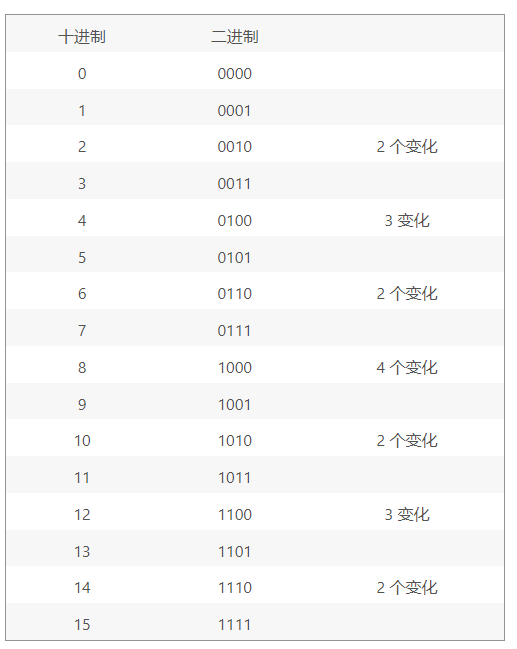

字邏輯設(shè)計課程中,我們已經(jīng)學(xué)過了BCD碼的相關(guān)知識,它用4位二進制數(shù)來表示1位十進制數(shù)中的09,是二進制編碼的十進制代碼,常見的BCD碼有8421BCD碼,2421BCD碼,5421BCD碼,余3碼以及格雷

2022-07-12 16:41:42

制。遞歸算法,如 IIR 濾波、MPEG 1/2/4 中的變長編碼(VLC)、上下文自適應(yīng)變長編碼(CAVLC),以及 H.264/AVC 中的上下文自適應(yīng)二進制算術(shù)編碼(CABAC),當(dāng)映射到這些可編程

2008-06-25 11:33:26

在C語言中二進制表示是0bxxx開頭的,

為什么給寄存器賦值GpioCtrlRegs.GPAMUX2.bit.GPIO16??=?0b00;? 會出錯??

2018-05-14 07:02:41

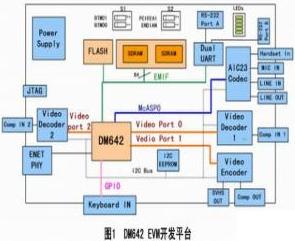

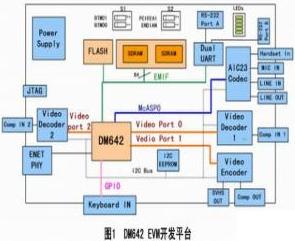

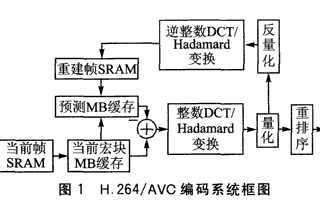

平臺總體框架圖 圖3 H.264編碼模塊圖 2 H.264編碼器的優(yōu)化 2.1 總體優(yōu)化 [td] 總體優(yōu)化主要包括兩部分內(nèi)容:程序模塊化的設(shè)計及數(shù)據(jù)結(jié)構(gòu)的設(shè)計。 程序模塊化設(shè)計時,既要考慮

2011-07-13 17:12:01

一個8位二進制數(shù)經(jīng)過二進制LDPC編碼器編碼后等到一個幾位二進制的數(shù),怎么計算的?

2017-03-14 13:07:56

什么是H.264視頻編碼技術(shù)?如何去實現(xiàn)并優(yōu)化一種H.264視頻編碼器?

2021-06-03 07:00:52

在DSP平臺上進行視頻產(chǎn)品開發(fā)有什么優(yōu)勢?怎么實現(xiàn)基于ADSP-BF561的H.264編碼器設(shè)計?

2021-06-07 06:46:01

足H.264標(biāo)準的編解碼運算速度要求。因此,在穩(wěn)定的媒體處理器平臺上實現(xiàn)H.264標(biāo)準有著較好的工程意義和應(yīng)用前景。

2019-09-04 06:19:09

一種基于NiosII的低碼率實時H.264視頻編碼器設(shè)計

2021-06-07 07:06:49

H.263和MPEG一4可以節(jié)省20%~50%的碼率。就其基本檔次而言,編碼器的復(fù)雜度是H.263的10倍左右。H.264良好的網(wǎng)絡(luò)親和性和優(yōu)異的壓縮性能使其成為視頻應(yīng)用的首選,但其巨大的運算量

2019-07-29 06:52:57

Changes for Version JM7.3 to JM 7.2h.264編碼器源代碼,帶有H.264編碼器流程圖。Bug fixes- encoder: DPB for field

2008-06-25 11:46:18 164

164 H.264三大開源編碼器之評測報告Peter Lee 2005.6.19 Outline1、三大開源編碼器介紹2、實驗條件3、實驗結(jié)果4、實驗結(jié)論plus:增加t264 high quality mode的實驗結(jié)果note: 新

2008-08-25 13:07:10 51

51 闡述H.264/AVC 二進制算術(shù)編碼的原理,論述此編碼的IP 核設(shè)計方案及其FPGA 驗證。整個設(shè)計使用VerilogHDL 語言描述,在 ALDEC 的Active_HDL6.2 平臺上進行時序仿真,在 Synplicity 的Synplify7.0平

2009-09-03 09:11:20 25

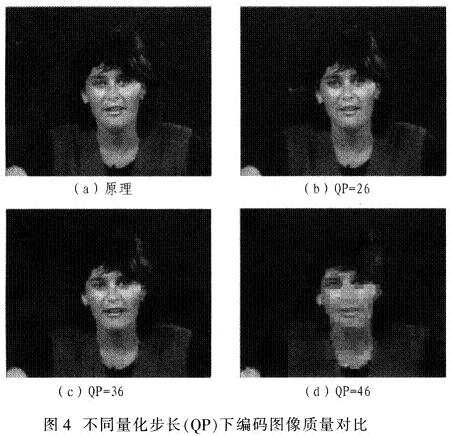

25 設(shè)計并實現(xiàn)了基于DSP 芯片TMS320DM642 的H.264 編碼器。詳細介紹了H.264 算法在DSP上的移植和優(yōu)化。為使編碼器達到實時應(yīng)用的要求,采用基于C64x CPU 的軟件優(yōu)化技術(shù),對H.264的一些核

2009-09-03 14:30:34 23

23 提出了H.264/AVC 硬件編碼器的一種3 級流水結(jié)構(gòu),以此來提高硬件加速電路的處理能力和利用效率。鑒于H.264 編碼芯片驗證的復(fù)雜性,還提出了一種基于ADSP-BF537的新型多媒體SoC 驗

2009-12-15 14:28:34 18

18 H.264 實時編碼器的研究和實現(xiàn)是目前視頻通信研究領(lǐng)域的一個熱點問題,本文介紹了基于TMS320DM642 平臺的H.264 編碼器的優(yōu)化,重點介紹了基于DM642 的整數(shù)DCT 變換、量化和匹配

2009-12-18 12:13:37 19

19 為了在改進的H.264 上實現(xiàn)無再損幀內(nèi)編碼,該文提出了一種新的基于整數(shù)線性規(guī)劃的優(yōu)化clip 算法及改進算法,解決了H.264 多次編碼中由當(dāng)前clip 模塊和幀內(nèi)預(yù)測運算引入的視頻畸

2010-02-09 14:28:11 35

35 基于ADSP-BF561的H.264視頻編碼器的實現(xiàn)

H.264/AVC是ITU-T VCEG和ISO/IECMPEG聯(lián)合制定的最新視頻編碼國際標(biāo)準,是目前圖像通信研究領(lǐng)域的熱點技術(shù)之一。H.264的視頻編碼層(VCL)

2008-12-26 14:43:44 863

863 H.264視頻編碼基本知識

一、 視頻編碼技術(shù)的發(fā)展歷程

視頻編碼技術(shù)基本是由ISO/IEC制定的MPEG-x和ITU-T制

2008-12-29 11:41:15 3485

3485 二進制

二進制與十進制的區(qū)別在于數(shù)碼的個數(shù)和進位規(guī)律有很大的區(qū)別,顧名思義,二進制的計數(shù)規(guī)律為逢二進一,是以2為基數(shù)的計數(shù)體制。10這個數(shù)在二進

2009-04-06 23:48:01 8831

8831

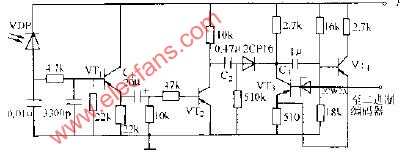

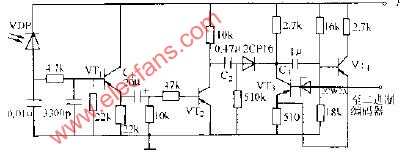

配用二進制編碼器的光控電路圖

2009-06-06 09:30:38 776

776

同步二進制計數(shù)器

1. 同步與異步二進制加法計數(shù)器比較態(tài)序表和工作波形一樣電路結(jié)構(gòu)不同: 異步二進制加法

2009-09-30 18:37:29 12854

12854

二進制編碼和二進制數(shù)據(jù)

二進制編碼是計算機內(nèi)使用最多的碼制,它只使用兩個基本符號"0"和"1",并且通過由這兩個符號組成的

2009-10-13 16:22:51 5150

5150 二進制數(shù)的運算規(guī)則 二進制數(shù)之間可以執(zhí)行算術(shù)運算和邏輯運算,其規(guī)則簡單,容易實現(xiàn)。 (1) 加法運算規(guī)則 0 + 0 = 0 例如:

2009-10-13 16:24:15 23784

23784 基于TMS320DM6446的H.264編碼器實現(xiàn)與優(yōu)化

1 引言

H.264是ITU-T的視頻編碼專家組(VCEG)和ISO/IEC的活動圖像專家組(MPEG)聯(lián)合制定的視頻壓縮標(biāo)準。

2010-02-10 09:20:11 1733

1733

什么是二進制計數(shù)器,二進制計數(shù)器原理是什么?

計數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數(shù),還可以實現(xiàn)

2010-03-08 13:16:34 31861

31861 二進制電平,什么是二進制電平

在二進制數(shù)字通信系統(tǒng)中,每個碼元或每個符號只能是“1”和“0”兩個狀態(tài)之一。若將每個碼元可能取的狀態(tài)增

2010-03-17 16:51:58 2671

2671 數(shù)字化信息編碼的概念和二進制編碼的知識

一、數(shù)字化信息編碼的概念

1.信息: 計算機能夠處理的如數(shù)值、文字、符號、語音、圖形等數(shù)據(jù)稱為信息。

2010-04-15 14:28:03 3446

3446 二進制數(shù)值數(shù)據(jù)的編碼與運算算法

一、原碼、反碼、補碼的定義

1、原碼的定義

2、補碼的定義

2010-04-15 14:42:03 3408

3408 十進制數(shù)的二進制編碼

在人機交互過程中,為了既滿足系統(tǒng)中使用二進制數(shù)的要求,又適應(yīng)人們使用十進制數(shù)的習(xí)慣

2010-05-02 19:04:06 10659

10659 Jointwave發(fā)布的H.264編碼器可實現(xiàn)1080p

Jointwave發(fā)布的H.264編碼器技術(shù)提供了單芯片HD和超低功耗廣播級視頻— 針對65nm處理器60mW可實現(xiàn)1080p。

正如在強調(diào)Jointwave的H.26

2010-01-04 08:41:20 1383

1383 摘要:在DM642 EVM平臺上實現(xiàn)了 H.264視頻編碼器,并從內(nèi)存分配、Cache優(yōu)化、代碼優(yōu)化以及匯編程序級優(yōu)化等幾個方面對編碼

2011-01-10 14:12:14 3715

3715

H.264是一種高效的視頻編碼壓縮標(biāo)準,它集中了以往標(biāo)準的優(yōu)點。基于H.264的高效編碼壓縮技術(shù),文章研究了塊基立體視頻編碼方法,并對基于H.264, 和基于H.264的立體視頻編碼方案進行了

2011-06-10 16:34:09 43

43 H.264 獲得出色壓縮效果和質(zhì)量的代價是壓縮編碼算法復(fù)雜度的增加。為了尋求更高的編碼速度,集群并行計算被運用到H.264的視頻編碼計算中。分析H.264可實現(xiàn)并行計算的任務(wù)單元選擇;

2011-07-27 15:56:16 0

0 介紹了基于嵌入式平臺PXA255的h.264視頻編碼器的實現(xiàn)。在描述了視頻編碼器的硬件結(jié)構(gòu)設(shè)計及視頻采集軟件的實現(xiàn)的基礎(chǔ)上,詳細介紹了h.264對視頻編碼標(biāo)準的一些改進以及基于PXA2

2011-09-02 16:41:57 87

87 為了實現(xiàn)基于DSP的H.264視頻編碼器的實時性能,提出了一系列優(yōu)化實現(xiàn)方法。首先結(jié)合TMS320DM6437硬件特點,描述了X264代碼向TMS320DM6437平臺的移植過程和優(yōu)化方法,重點介紹了整數(shù)DCT變換

2012-05-22 15:10:25 63

63 二維離散余弦(DCT)在H.264視頻編碼中承擔(dān)者信號從時域到頻域變換的作用。在現(xiàn)場可編程邏輯門陣列(FPGA)上設(shè)計了高效的采用流水線結(jié)構(gòu)的H.264 DCT硬件電路。首先,把二維4×4 D

2012-07-31 15:26:39 6660

6660

CAST半導(dǎo)體公司提供基于FPGAs和ASICs的H.264High Profile視頻編碼器IP核具有出眾的視頻效果、極佳的播放性能及便捷的系統(tǒng)集成等特性。

2012-12-05 09:28:09 2955

2955 提出了一種在TI公司高性能數(shù)字信號處理器TMS320DM3730上進行H.264編碼器(即x264編碼器)移植與優(yōu)化的方法,詳細描述了在CCS4.2開發(fā)平臺上進行x264編碼器移植工作的基本原理和需要注意的

2013-01-08 18:27:14 69

69 二進制加法程序【匯編版】二進制加法程序【匯編版】二進制加法程序【匯編版】二進制加法程序【匯編版】

2015-12-29 11:02:06 0

0 基于PowerPC的H.264編碼器中斷處理程序解析

2016-01-04 15:26:58 6

6 SAR開關(guān)時序的非二進制結(jié)構(gòu)

2017-04-05 16:08:27 5

5 基于DM642的H.264編碼算法優(yōu)化與實現(xiàn)

2017-05-18 09:22:58 1

1 隨著編碼視頻在網(wǎng)絡(luò)流量中占比的不斷增長,視頻傳輸機制的性能評估變得越來越重要。論文提出來一個基于H.264視頻編碼標(biāo)準機制的視頻傳輸網(wǎng)絡(luò)跟蹤綜合評價方法,對視頻網(wǎng)絡(luò)傳輸?shù)男阅茉u估主要從兩方面提出,即

2017-12-21 15:30:24 0

0 格雷碼,又叫循環(huán)二進制碼或反射二進制碼,格雷碼是我們在工程中常會遇到的一種編碼方式,它的基本的特點就是任意兩個相鄰的代碼只有一位二進制數(shù)不同,這點在下面會詳細講解到。格雷碼的基本特點就是任意兩個相鄰的代碼只有一位二進制數(shù)不同。

2018-03-02 15:48:53 19587

19587

BCD碼亦稱二進碼十進數(shù)或二-十進制代碼。用4位二進制數(shù)來表示1位十進制數(shù)中的0~9這10個數(shù)碼。它是一種二進制的數(shù)字編碼形式,用二進制編碼的十進制代碼。BCD碼這種編碼形式利用了四個位元來儲存一個十進制的數(shù)碼,使二進制和十進制之間的轉(zhuǎn)換得以快捷的進行。

2018-03-14 10:15:42 7346

7346 目前的視頻監(jiān)控行業(yè),基于DSP的H.264編碼器解決方案占有絕對優(yōu)勢的市場份額,這是由DSP方案開發(fā)周期相對較短的特性決定的。在ASIC或FPGA方案仍處于研發(fā)階段時,DSP方案已捷足先登,并較好地解決了視頻監(jiān)控行業(yè)中H.264編碼器方案從無到有的過程,為H.264在監(jiān)控應(yīng)用中走向成熟立下了汗馬功勞。

2018-10-29 08:21:00 13575

13575 H.264高效的編碼效率是以其高復(fù)雜性為代價的,因此制約了它在高分辨率、實時處理等方面的應(yīng)用。而FPGA器件采用流水控制策略和并行處理方式,可為H.264復(fù)雜的編碼模塊提供硬件加速引擎。變換量化模塊在H.264編碼算法中被頻繁調(diào)用。

2019-08-01 08:04:00 3026

3026 H.264以其高復(fù)雜度為代價獲得了優(yōu)異的編碼效率, 其中除部分控制流程的復(fù)雜模塊外,H.264中的很多模塊適合用硬件實現(xiàn)。應(yīng)用中通常使用CPU+FPGA結(jié)構(gòu),將耗時較多的模塊用FPGA實現(xiàn),CPU僅負責(zé)一些低復(fù)雜度的算法和編碼流程參數(shù)的設(shè)置。

2019-09-24 07:58:00 3358

3358 諸多方面都超越了以往的視頻標(biāo)準。H.264有兩種熵編碼方案:一種是從可變長編碼方案發(fā)展而來的基于上下文的自適應(yīng)可變長編碼CAVLC;另一種是從算術(shù)編碼發(fā)展而來的基于上下文的自適應(yīng)二進制算術(shù)編碼CABAC。與CAVLC相比,CABAC可以節(jié)省約7%的碼流,但增加了10%的計算時間

2018-11-05 09:55:01 1042

1042 開會的可能。視頻會議系統(tǒng)相比傳統(tǒng)的電話會議更充分利用了互聯(lián)網(wǎng)資源,從而降低了運營成本。 視頻編碼器是視頻會議系統(tǒng)的主要構(gòu)成部分。目前視頻壓縮標(biāo)準有H.261、H.263、MPEG4和H.264等。新一代視頻編碼標(biāo)準H.264與以往標(biāo)準相比具有壓縮率高,網(wǎng)絡(luò)親

2018-11-28 12:24:01 749

749 系統(tǒng)。在相同的圖像質(zhì)量情況下,H.264比H.263和MPEG一4可以節(jié)省20%~50%的碼率。就其基本檔次而言,編碼器的復(fù)雜度是 H.263的10倍左右。H.264良好的網(wǎng)絡(luò)親和性和優(yōu)異的壓縮性能使其成為視頻應(yīng)用的首選,但其巨大的運算量成為許多應(yīng)用的瓶頸。筆者基于 NiosII設(shè)

2019-02-27 07:04:01 848

848

二進制編碼小數(shù)的主要優(yōu)點是它允許在decimal(base-10)和binary(base-2)表單之間輕松轉(zhuǎn)換。但是,缺點是BCD代碼是浪費的,因為不使用 1010 (十進制10)和 1111 (十進制15)之間的狀態(tài)。然而,二進制編碼的十進制有許多重要的應(yīng)用,特別是使用數(shù)字顯示。

2019-06-24 09:31:19 16029

16029

二進制解碼器是另一種由各個邏輯門構(gòu)成的組合邏輯電路,與編碼器完全相反。

2019-06-22 09:41:36 10538

10538

目前很多攝像機采用了H.265的編碼標(biāo)準,H.264編碼的攝像機逐漸減少,為什么H.265會流行?H.264和H.265有何不同?

2020-03-14 15:53:43 31230

31230 我司最近的新產(chǎn)品都能支持H.265,越來越多的輸入視頻信號都采用了H.265的編碼標(biāo)準,H.264編碼的逐漸減少,為什么H.265會流行?H.264和H.265有何不同?今天我們就來給各種施工

2020-05-21 14:56:33 2825

2825 目前高清H.264 攝像機的核心SoC基本上都是ASIC,而FPGA作為近年來發(fā)展迅速的可編程器件,在高清H.264 攝像機的SoC領(lǐng)域如何能有一席之地?這是我們的設(shè)計需要實現(xiàn)的目標(biāo)。

2020-07-27 10:50:01 12

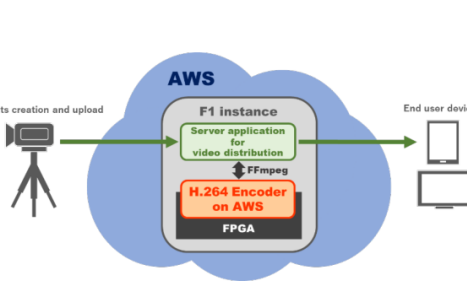

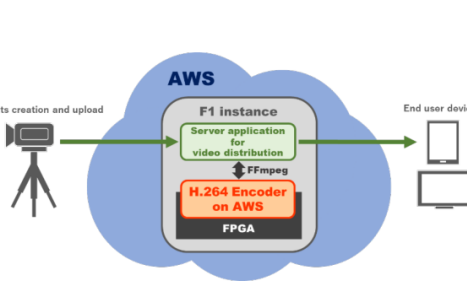

12 SoC設(shè)計與應(yīng)用技術(shù)領(lǐng)導(dǎo)廠商Socionext Inc.(以下“Socionext”)宣布,成功開發(fā)了一款基于Amazon Web Services(以下“AWS”)的高速、高畫質(zhì)視頻編碼器“H.264 Encoder on AWS”。

2020-10-12 13:49:59 3705

3705

二進制解碼器是由單獨的邏輯門構(gòu)成的另一種組合邏輯電路,與編碼器完全相反。名稱“解碼器”是指將編碼信息從一種格式轉(zhuǎn)換或解碼為另一種格式,因此二進制解碼器使用2 n個輸出將“ n”個二進制輸入信號轉(zhuǎn)換為等效代碼。

2021-01-03 17:42:00 7000

7000

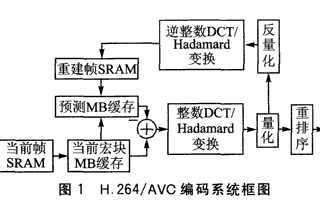

根據(jù)H.264/AVC編碼器原理及結(jié)構(gòu),同時考慮到現(xiàn)有硬件資源的限制以及該設(shè)計的應(yīng)用需求,設(shè)計了圖1所示的H.264/AVC編碼系統(tǒng)結(jié)構(gòu)。

2021-03-16 14:12:54 3207

3207

基于FPGA的二進制相移鍵控設(shè)計方案

2021-05-28 09:36:50 12

12 H264編碼器與AdobeFlashMedia組合使用(嵌入式開發(fā)技術(shù)考試)-H264編碼器與AdobeFlashMedia組合使用? ? ? ? ? ?

2021-07-30 15:19:13 7

7 絕對編碼器中的傳感器輸出格雷碼序列,需要一些復(fù)雜的轉(zhuǎn)換方法才能正確使用。本文展示了如何獲取絕對編碼器使用的格雷碼并將其轉(zhuǎn)換為二進制。

2022-05-05 15:41:49 8254

8254

本方案是一個基于FPGA的二進制時鐘,使用GPS作為時間參考。

2022-05-13 17:41:31 3118

3118

將二進制數(shù)視為元胞自動機可能有助于數(shù)字二進制計數(shù)器的設(shè)計和實現(xiàn)嗎?

2022-07-28 11:47:10 2447

2447

H.264,同時也是 MPEG-4第十部分,是由 ITU-T 視頻編碼專家組(VCEG)和 ISO/IEC

動態(tài)圖像專家組(MPEG)聯(lián)合組成的聯(lián)合視頻組(JVT,Joint Video Team

2022-08-31 15:39:24 2

2 將信息(如數(shù)和字符等)轉(zhuǎn)換成符合一定規(guī)則的二進制代碼。

2023-03-21 11:55:48 16409

16409

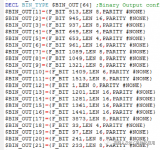

數(shù)值范圍取決于機床數(shù)據(jù)中二進制輸出 $BIN_OUT[...] 的配置(文件 ...STEU\Mada\$custom.dat 中的變量)。

2023-07-27 10:05:17 1124

1124

如何實現(xiàn)二進制和BCD碼數(shù)據(jù)的相互轉(zhuǎn)變? 二進制碼是將十進制數(shù)字表示為二進制數(shù)和十進制數(shù)的一種表示方法。在計算機系統(tǒng)中,二進制數(shù)是最基本的數(shù)制表示方法,而BCD碼則是用于將數(shù)字直接轉(zhuǎn)換為二進制數(shù)

2024-02-18 14:51:58 6597

6597 在數(shù)字電路設(shè)計中,計數(shù)器是一種非常關(guān)鍵的組件,用于測量時間、計數(shù)事件或跟蹤狀態(tài)變化等。其中,二進制串行計數(shù)器作為一種常用的計數(shù)器類型,在多種應(yīng)用場景中都發(fā)揮著重要作用。本文將對二進制串行計數(shù)器

2024-05-28 15:52:09 1987

1987 電子發(fā)燒友網(wǎng)站提供《TMS320DM365 H.264編碼器的應(yīng)用程序參數(shù)設(shè)置.pdf》資料免費下載

2024-10-14 11:37:18 0

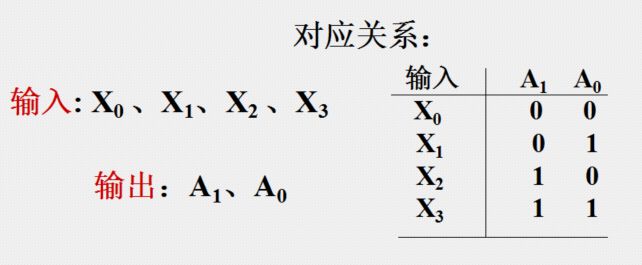

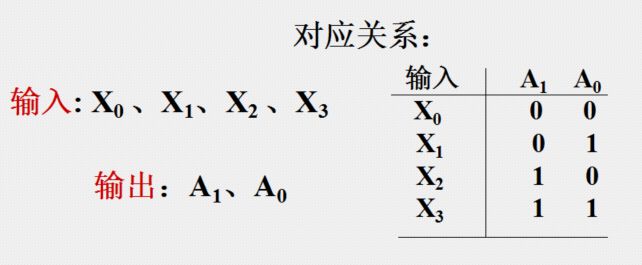

0 二進制編碼器是一種數(shù)字電路,它將輸入的二進制代碼轉(zhuǎn)換為對應(yīng)的輸出信號。在數(shù)字系統(tǒng)中,編碼器用于將數(shù)據(jù)從一種形式轉(zhuǎn)換為另一種形式,以便于處理和傳輸。 二進制編碼器工作原理 輸入與輸出關(guān)系 : 二進制

2024-11-06 09:44:16 3558

3558 編碼器是將信息從一種形式或格式轉(zhuǎn)換為另一種形式的設(shè)備。在數(shù)字和模擬系統(tǒng)中,編碼器扮演著至關(guān)重要的角色。二進制編碼器和模擬編碼器是兩種常見的編碼器類型,它們在不同的應(yīng)用場景中有著各自的優(yōu)勢和局

2024-11-06 09:45:42 1988

1988 二進制編碼器是一種電子電路,用于將二進制信號轉(zhuǎn)換為其他格式,如十進制、格雷碼等。以下是一些常見的二進制編碼器種類及其特點: 優(yōu)先編碼器(Priority Encoder) : 特點 :優(yōu)先編碼器能夠

2024-11-06 09:47:07 2121

2121 隨著科技的不斷進步,機器人技術(shù)已經(jīng)成為現(xiàn)代工業(yè)、服務(wù)業(yè)乃至家庭生活中不可或缺的一部分。機器人的智能化程度不斷提高,這在很大程度上依賴于其傳感器系統(tǒng)。二進制編碼器作為一種傳感器,能夠?qū)⑽锢砹哭D(zhuǎn)換

2024-11-06 09:48:22 1673

1673 二進制編碼器是一種將二進制信號轉(zhuǎn)換為數(shù)字信號的電子設(shè)備,廣泛應(yīng)用于計算機、通信和自動化控制系統(tǒng)中。當(dāng)二進制編碼器出現(xiàn)問題時,有效的故障排除是確保系統(tǒng)正常運行的關(guān)鍵。 1. 初步檢查 1.1 檢查電源

2024-11-06 09:49:36 1666

1666 二進制編碼器是一種將二進制信號轉(zhuǎn)換為數(shù)字信號的電子設(shè)備,廣泛應(yīng)用于自動化領(lǐng)域。 一、二進制編碼器的工作原理 二進制編碼器是一種將二進制信號轉(zhuǎn)換為數(shù)字信號的電子設(shè)備。它通過接收輸入信號,將其轉(zhuǎn)換為相應(yīng)

2024-11-06 09:53:06 1469

1469 編碼器是工業(yè)自動化和機器人技術(shù)中不可或缺的組件,用于將機械位置或運動轉(zhuǎn)換為電信號。二進制編碼器和絕對編碼器是兩種常見的編碼器類型,它們各自有著獨特的特點和應(yīng)用場景。 二進制編碼器 二進制編碼器,也

2024-11-06 09:54:30 1860

1860 在數(shù)字電子系統(tǒng)中,二進制編碼器扮演著至關(guān)重要的角色。它負責(zé)將外部世界的模擬信號轉(zhuǎn)換為計算機可以理解的數(shù)字信號。精度和分辨率是衡量二進制編碼器性能的兩個關(guān)鍵指標(biāo)。 1. 二進制編碼器的基本原理 二進制

2024-11-06 09:56:46 1796

1796 。為此,我們推出了在線二進制編碼器,一個便捷、高效的數(shù)據(jù)轉(zhuǎn)換工具。 在線二進制編碼器以其簡潔直觀的界面和強大的功能,為用戶提供了數(shù)據(jù)轉(zhuǎn)換的快捷通道。用戶只需輸入待轉(zhuǎn)換的數(shù)據(jù),選擇轉(zhuǎn)換方向(如十進制到二進制、二進

2024-11-15 09:01:23 2877

2877 直接對應(yīng)于我們?nèi)粘J褂玫氖?b class="flag-6" style="color: red">進制數(shù)字系統(tǒng)。以下是BCD編碼的一些應(yīng)用和它與二進制編碼的區(qū)別: BCD編碼的應(yīng)用 數(shù)字顯示設(shè)備 :在數(shù)字鐘表、計算器和其他需要顯示十進制數(shù)字的設(shè)備中,BCD編碼可以直接用于顯示數(shù)字,無需額外的轉(zhuǎn)換。 金融和會計系統(tǒng) :在處理貨幣和會計數(shù)

2024-12-20 17:11:11 4699

4699 在數(shù)字技術(shù)席卷全球的今天,二進制編碼器作為連接物理世界與數(shù)字系統(tǒng)的“橋梁”,正以不可替代的姿態(tài)滲透到工業(yè)制造、智能家居、無人駕駛等核心領(lǐng)域。它不僅是自動化產(chǎn)線的“神經(jīng)中樞”,更是推動人工智能、物聯(lián)網(wǎng)

2025-10-14 08:35:54 375

375

電子發(fā)燒友App

電子發(fā)燒友App

評論