AD9054 高速A/D采集技術(shù)已在許多領(lǐng)域得到愈來愈廣泛的應(yīng)用,本文將詳細論述采用CPLD技術(shù)來實現(xiàn)120MHz高速A/D采集卡的設(shè)計方法,該采集卡具有包括負延遲觸發(fā)在內(nèi)的多種觸發(fā)方式,采用

2019-01-07 08:44:00 7102

7102

學(xué)、光電檢測技術(shù)和現(xiàn)代測量技術(shù)中成果累累。隨著CCD技術(shù)的迅猛發(fā)展,針對CCD信號的采集及采集之后的信號如何與計算機進行信息通信就成為CCD應(yīng)用的一個重要問題,而能夠針對CCD每一個象素進行高速采集并

2018-12-03 15:18:20

AD9949是一款CCD信號處理芯片,是的,我的畢業(yè)設(shè)計是完成圖像采集。為角膜地形圖儀的圖像采集部分做知識儲備。該設(shè)備主要應(yīng)用于醫(yī)院,采集人眼的表面形貌信息,為近視眼患者配置一種硬性隱形眼鏡。圖像

2018-11-02 09:33:14

CPLD是什么?CPLD在高速尋址中有哪些應(yīng)用?

2021-05-06 07:40:21

是通過編程MCU 的I/ O端口來獲得CCD 驅(qū)動脈沖信號的。這種方法的靈活性好, 精度也可以很高, 對不同的CCD 器件只需要修改程序即可。由于CCD 的驅(qū)動頻率為MHz 級, 使得選用MCU 器件

2018-11-13 11:13:20

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-08 06:11:56

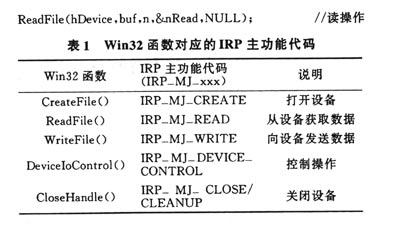

只有一個有效),然后看看EPP的傳輸吧。原理解釋:1.PC想要發(fā)起傳輸。它會插入某個選通信號。如果該傳輸為寫入,那么“寫入”信號為低電平,然后驅(qū)動8bit通道。不然的話“寫入”信號為高電平,而8bit

2019-08-06 05:00:00

。 關(guān)鍵詞:CCD;圖像傳感器;TC237B;圖像采集 1 引言 TC237B是TI公司生產(chǎn)的一款1/3英寸的幀轉(zhuǎn)移方式的電荷耦合器件(CCD)圖像傳感器。它有340000個像素,其中有

2018-12-04 13:48:42

《基于ARM與線性CCD的高速數(shù)據(jù)采集系統(tǒng)》

2012-08-16 14:06:55

高速、超寬帶信號采集技術(shù)在雷達、天文和氣象等領(lǐng)域應(yīng)用廣泛。高采樣率需要高速的模/數(shù)轉(zhuǎn)換器(ADC)。目前市場上單片高速ADC的價格昂貴,分辨率較低,且采用單片超高速ADC實現(xiàn)的數(shù)據(jù)采集對FPGA的性能和PCB布局布線技術(shù)提出了嚴峻的挑戰(zhàn)。

2019-11-08 06:34:52

本文采用了具有較高傳輸速率的增強型并行口協(xié)議(EPP)和FPGA,實現(xiàn)對OV7620CMOS圖像傳感器進行高速數(shù)據(jù)采集,它最高速率可以達到2Mb/s。

2021-05-10 07:01:16

了基于可編程邏輯器件(CPLD)技術(shù),將CCD驅(qū)動電路集成在一塊芯片上,實現(xiàn)了CCD圖像傳感器的驅(qū)動電路,并且結(jié)合Ahera公司的EPM7160SLC84-10完成了硬件電路的設(shè)計。 1 全幀型CCD驅(qū)動

2018-11-15 14:54:53

本文介紹了一個基于ARM的線性CCD高速采集系統(tǒng),系統(tǒng)中選擇了高速線性CCD和高速ADC,因為ADC的采祥速度相對ARM的工作時鐘頻率較慢,所以使用CPLD和FIFO作為A/D和ARM之間的1/0

2023-09-26 07:41:28

] 。 定時控制電路用來設(shè)置傳感器的工作模式,產(chǎn)生工作時序,控制數(shù)據(jù)的輸出等。像素采集到的信號在芯片內(nèi)部就經(jīng)過了放大、AD轉(zhuǎn)換、存儲等處理,最后可輸出需要的數(shù)字信號,也可以輸出模擬信號,這給用戶在設(shè)計時提供了

2018-11-01 17:23:19

。因此,為了采集數(shù)據(jù)量大的圖像數(shù)據(jù),本文采用了具有較高傳輸速率的增強型并行口協(xié)議(EPP)和FPGA,實現(xiàn)對OV7620CMOS圖像傳感器進行高速數(shù)據(jù)采集,它最高速率可以達到2Mb/s。

2020-04-30 07:47:07

基于視頻解碼芯片與CPLD的實時圖像采集系統(tǒng) &

2008-08-29 10:34:55

高速A/D采集卡是什么?如何利用CPLD技術(shù)來設(shè)計120MHz高速A/D采集卡?在設(shè)計的的過程中又有哪些事項需要注意?

2021-04-12 07:03:36

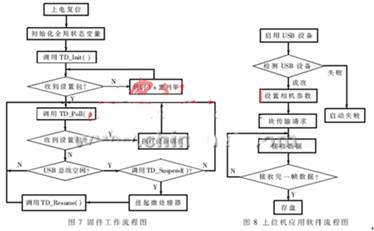

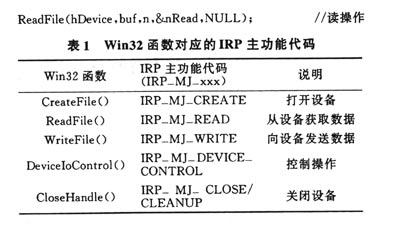

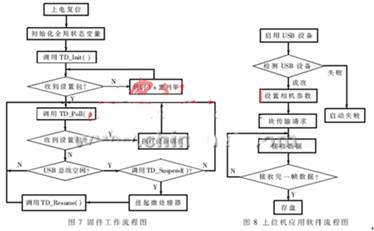

本文介紹了一種采用專用CCD視頻信號處理芯片和CPLD技術(shù)來設(shè)計的CCD視頻信號處理電路,并采用USB接口技術(shù)實現(xiàn)數(shù)據(jù)傳輸。

2021-06-04 07:14:43

設(shè)計一種基于CPLD的可編程高精度CCD信號發(fā)生器,設(shè)計中充分利用CPLD的可編程性,模擬出滿足系統(tǒng)要求的CD信號,輸出信號頻率達到1IMHZ。

2021-04-13 06:44:36

本文將詳細論述采用CPLD技術(shù)來實現(xiàn)120MHz高速A/D采集卡的設(shè)計方法,該采集卡具有包括負延遲觸發(fā)在內(nèi)的多種觸發(fā)方式,采用CPLD復(fù)雜可編程邏輯器件(又稱FPGA)EPM7128SQC100-7和AD公司的高速模數(shù)轉(zhuǎn)換器(A/D)AD9054BST-135來實現(xiàn)。

2021-04-30 06:27:01

設(shè)計的基于CPLD與單片機的高速數(shù)據(jù)采集系統(tǒng)在QUARTUS II軟件中進行了仿真并達到了預(yù)期的控制邏輯。

2021-04-13 06:07:06

EPP技術(shù)和CPLD技術(shù)介紹應(yīng)用CPLD及EPP技術(shù)對CCD信號像素級的高速采集

2021-04-08 06:11:10

如何采用具有較高傳輸速率的增強型并行口協(xié)議(EPP)和FPGA,實現(xiàn)對OV7620CMOS圖像傳感器進行高速數(shù)據(jù)采集,讓它的最高速率可以達到2Mb/s?

2021-04-12 07:08:41

前段時間看到了這個東西,研究了很久都沒有什么大的進展。過來問問大家,希望能夠得到解答。我看到網(wǎng)上賣的ccd攝像頭出來三根線,兩個是電源,一根是模擬(沒有問題吧?)。問題:這個模擬信號,怎么知道

2014-01-04 00:22:48

最近在搞一個項目,用AD9970采集CCD的像素,但是關(guān)于AD9970的配置我有點不明白,CLPOB與PBLK具體是用在一行像素的哪個位置,還有就是如何同步LVDS輸出,與像素的邊界對齊,讓FPGA這邊能采集到完整的一行數(shù)據(jù)

2024-01-10 07:04:38

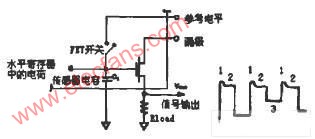

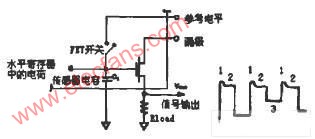

精度。CDS采用兩級高速采樣保持器(S/H),一級用來采集復(fù)位電平,即在復(fù)位脈沖過去之后至信號電荷包到來之前某一時刻的電平;另一級用來采集像元信號電平,即在水平時鐘串?dāng)_后到信號電荷到來前的某一時刻電平

2018-11-15 16:27:46

如何去設(shè)計一個基于FPGA和USB 2.0的高速CCD聲光信號采集系統(tǒng)?

2021-04-29 06:22:30

線陣CCD數(shù)據(jù)采集及LCD顯示 Linear Array CCD Data Acquisition and LCD Display

摘要:以TCD1200D為例,介紹了線陣CCD的一種通用高速數(shù)據(jù)采集方法,詳細介紹了電路組成、數(shù)據(jù)采集軟件實現(xiàn),

2009-01-11 12:08:46 45

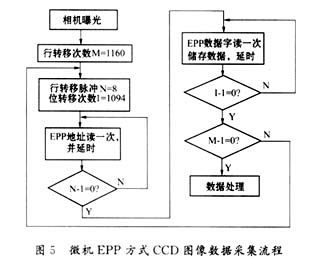

45 通過對微機并行口EPP 模式下數(shù)據(jù)讀取時序的深入實驗分析,研究實現(xiàn)500ksps數(shù)據(jù)連續(xù)采集及傳輸涉及的軟件和硬件相關(guān)因素; 采用CPLD 器件, 結(jié)合大容量SRAM 構(gòu)成FIFO, 實現(xiàn)Win98 環(huán)境

2009-04-16 09:10:59 17

17 采用VHDL 語言設(shè)計,用CPLD 控制模/ 數(shù)轉(zhuǎn)換電路, 完成多路模擬輸入的高速同步數(shù)/ 模轉(zhuǎn)換,具有容錯和自檢能力。CPLD 與處理器之間采用并行接口,具有很好的移植性、可靠性。

2009-04-16 10:44:25 7

7 采用VHDL 語言設(shè)計,用CPLD 控制模/ 數(shù)轉(zhuǎn)換電路, 完成多路模擬輸入的高速同步數(shù)/ 模轉(zhuǎn)換,具有容錯和自檢能力。CPLD 與處理器之間采用并行接口,具有很好的移植性、可靠性。

2009-05-15 13:10:35 18

18 通過對微機并行口EPP 模式下數(shù)據(jù)讀取時序的深入實驗分析,研究實現(xiàn)500ksps數(shù)據(jù)連續(xù)采集及傳輸涉及的軟件和硬件相關(guān)因素; 采用CPLD 器件, 結(jié)合大容量SRAM 構(gòu)成FIFO, 實現(xiàn)Win98 環(huán)境

2009-05-15 15:03:51 13

13 以紡織布坯疵點在線檢測系統(tǒng)為應(yīng)用背景,探討了基于Camera Link接口協(xié)議標(biāo)準(zhǔn)的線陣CCD相機圖像高速采集邏輯控制接口的實現(xiàn)技術(shù)。重點闡述了信號轉(zhuǎn)換接口、基于FPGA的生成幀圖

2009-06-03 09:50:56 23

23 本文介紹FPGA 和EPP(增強型并行口)相結(jié)合技術(shù)對OV7620CMOS 圖像傳感器進行高速數(shù)據(jù)采集,提供一種利用PC 機外設(shè)對圖像采集的解決方案。該設(shè)計方案已應(yīng)用在隧道的平行度檢測的試驗

2009-07-01 11:24:53 43

43 本文介紹了一種基于CPLD的溫度采集系統(tǒng)的設(shè)計方法,設(shè)計分為溫度采集和LED顯示兩個功能模塊。與常用溫度采集系統(tǒng)相比,本設(shè)計采用高精度數(shù)字溫度傳感器MAX6627與CPLD控制芯片E

2009-07-07 13:44:56 22

22 文章介紹了一種基于單片機80C196KB 的線陣CCD 高速采集系統(tǒng)。系統(tǒng)采用線陣CCD 專用A/D 芯片MAX1101 和直接存儲器控制方式解決了高速采集(A/D 變換)與慢速CPU 之間的矛盾。關(guān)鍵詞:

2009-08-04 10:10:08 38

38 基于CPLD 和DSP 設(shè)計了線陣CCD 檢測系統(tǒng),CCD 的時序驅(qū)動由CPLD 實現(xiàn),經(jīng)過運放后的視頻信號由TMS320F2812 進行采集和處理,此檢測系統(tǒng)已成功應(yīng)用于醫(yī)藥包裝行業(yè)的數(shù)粒機系統(tǒng),能夠可

2009-08-13 14:53:46 22

22 本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達高度表高速大容量數(shù)據(jù)采集存儲系統(tǒng),分析了系統(tǒng)組成和設(shè)計思想,著重對CPLD 實現(xiàn)的功能做了介紹并給出了代表信號

2009-09-18 11:09:30 11

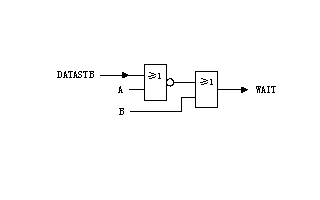

11 本文針對新型匝間耐壓測試儀中需要高速采集數(shù)據(jù)的問題提出了一種結(jié)合CPLD 與單片機的高速數(shù)據(jù)采集系統(tǒng)設(shè)計方案。CPLD 產(chǎn)生A/D 芯片的控制時序以及SRAM 的讀寫控制時序,單片機輸

2009-12-23 14:59:57 88

88 基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速AD采集卡的設(shè)計:介紹了一種基于復(fù)雜可編程邏輯器件高速AD采集卡的設(shè)計方法,給出了這種采集卡的硬件原理電路和主要的軟件設(shè)計思路,采用

2010-01-17 09:37:46 40

40 基于CPLD 的雷達高度表高速大容量數(shù)據(jù)采集存儲系統(tǒng)設(shè)計作者:李貴新 袁嗣杰 轉(zhuǎn)貼自:微計算機信息摘 要:本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達高

2010-01-27 14:18:26 22

22 基于CPLD的120MHz高速A/D采集卡的設(shè)計徐法東 翟正軍 高速A/D采集技術(shù)已在許多領(lǐng)域得到愈來愈廣泛的應(yīng)用,本文將詳細論述采用CPLD技術(shù)來實現(xiàn)120MHz高速A/D采集卡的設(shè)計方法,

2010-02-08 09:49:15 57

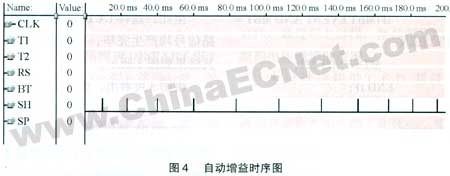

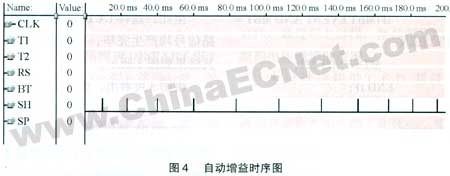

57 摘要本文介紹了一種基于CPLD并具有自動增益調(diào)整功能的CCD驅(qū)動電路。CCD輸出的模擬電壓值與其曝光時間有著密切的關(guān)系,根據(jù)這一原理,對CCD輸出的模擬電壓值進行A/D轉(zhuǎn)換,由CPLD

2010-04-29 08:58:31 39

39 摘 要:本文以日本東芝公司的線陣CCD器件TCD1206SUP為例,在研究了線陣CCD器件工作原理和驅(qū)動電路波形的基礎(chǔ)上,介紹了采用圖形式層次設(shè)計方法,用復(fù)雜可編程邏輯器件(CPLD)設(shè)計線陣CCD

2010-07-15 13:42:30 68

68 針對基于EPP協(xié)議的并行端口設(shè)備開發(fā)的特點與趨勢,開發(fā)了由AD轉(zhuǎn)換器AD1671和FIFO存儲器ID7202構(gòu)成的高速數(shù)據(jù)采集系統(tǒng),并通過IDT7202與EPP 的接口電路實現(xiàn)了采集數(shù)據(jù)的高速回傳。

2010-09-03 15:42:33 17

17 換體DMA高速數(shù)據(jù)采集電路的CPLD實現(xiàn)

介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實現(xiàn)。用CPLD設(shè)計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 1008

1008

CPLD在多路高速同步數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

CPLD(Complex Programmable Logic Device,復(fù)雜可編程邏輯器件)是在傳統(tǒng)的PAL、GAL基礎(chǔ)上發(fā)展而來的,具有多種工作方式

2009-03-28 16:49:00 1302

1302

設(shè)計了以CPLD為核心處理芯片的多路數(shù)據(jù)采集系統(tǒng),整個數(shù)據(jù)采集系統(tǒng)可實現(xiàn)最大采集頻率為800kHz,通道數(shù)為48路的模擬信號的采集。系統(tǒng)中采用了TI公司最新推出的高速低功耗A/D

2009-05-05 20:04:02 2054

2054

介紹了一種基于CPLD(復(fù)雜可編程邏輯器件)和FIFO(先入先出存儲器)的多通道高速A/D數(shù)據(jù)采集系統(tǒng)的設(shè)計方法,并給出了這種數(shù)據(jù)采集方法的硬件原理電路和主要的軟件設(shè)計思路

2009-05-05 20:50:09 1964

1964

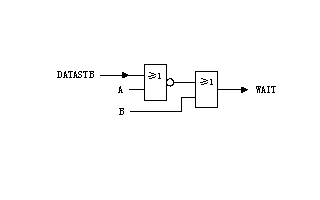

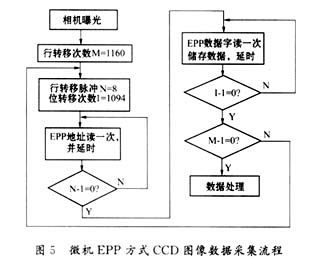

【摘 要】 介紹了微機增強并行口(

EPP)方式及快速線驅(qū)動和接收進行中遠距離數(shù)據(jù)快速

采集的方法,設(shè)計了

CCD相機數(shù)據(jù)傳輸?shù)慕涌陔娐泛蛙浖?/div>

2009-05-14 21:02:57 2204

2204

摘要:介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實現(xiàn)。用CPLD設(shè)計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積大、電路復(fù)雜、不能實現(xiàn)在線

2009-06-20 15:12:07 1203

1203

高速數(shù)據(jù)采集系統(tǒng)中精確時標(biāo)的CPLD實現(xiàn)方法

本文介紹一種利用復(fù)雜可編程邏輯器件給高速數(shù)據(jù)采集系統(tǒng)中的采集數(shù)據(jù)貼上精確時間標(biāo)簽的方法,并

2009-07-20 12:42:23 828

828 CCD信號采集系統(tǒng)的USB接口設(shè)計

CCD(ChargeCoupledDevices)電荷耦合器件是20世紀(jì)70年代初發(fā)展起來的新型半導(dǎo)體集成光電器件。由于CCD器件具有諸多優(yōu)點:靈

2009-09-26 18:04:53 3042

3042

基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計與實現(xiàn)

介紹一種基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng),并詳細闡述了系統(tǒng)的結(jié)構(gòu)和軟硬件的實

2009-10-15 23:46:59 972

972

基于CPLD的CCD驅(qū)動電路自動增益調(diào)整

ccd(charge couple device)是一種電荷藕合式光電轉(zhuǎn)換器件。在物體位移測量系統(tǒng)中,常常以ccd作為位移傳感器。當(dāng)一

2009-12-14 14:04:39 1211

1211

基于增強并行口EPP的便攜式高速數(shù)據(jù)采集系統(tǒng)

針對基于EPP協(xié)議的并行端口設(shè)備開發(fā)的特點與趨勢,開發(fā)了由A/D轉(zhuǎn)換器AD

2010-01-13 09:57:18 1305

1305 基于CPLD/FPGA高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

0 引 言 傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般采用單片機,系統(tǒng)大多通過PCI總線完成數(shù)據(jù)的傳輸。其缺點是數(shù)學(xué)運算能力差;

2010-01-27 09:35:01 791

791

CCD相機的高速數(shù)據(jù)采集系統(tǒng)設(shè)計

CCD(Charge Couple Device)中文名為“電荷耦合器件”,是一種以電荷包的形式存儲和傳遞信息的半導(dǎo)體表面器件。由于CCD相機

2010-03-18 11:19:14 2399

2399

本文設(shè)計了一種基于CPLD的可編程高精度CCD信號發(fā)生器。充分利用CPLD的可編程性.模擬出滿足系統(tǒng)要求的CD信號,輸出信號頻率

2010-06-19 11:14:45 1173

1173

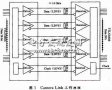

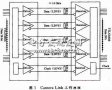

本文介紹了一種基于PXIE總線和Camera Link協(xié)議的高速CCD圖像采集系統(tǒng)的設(shè)計方案。該方案給出了一種Camera Link硬件接口電路的設(shè)計思路,并且選用Xilinx公司的Virtex-5 LX50T型FPGA作為整個采集系

2011-08-17 10:46:17 3814

3814

CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用! 介紹了高速數(shù)據(jù)采集系統(tǒng)的整體框架分析了其中的通用部分CPLD系列產(chǎn)品的特點及其開發(fā)軟件.CPLD根據(jù)高速數(shù)據(jù)采集系統(tǒng)的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26 提出一種基于USB的彩色CCD高清圖像采集系統(tǒng)設(shè)計方案。圖像數(shù)據(jù)的來源采用的是SONY公司的 ICX205AK芯片,結(jié)合USB2.0接口,復(fù)雜可編程邏輯器件CPLD設(shè)計了一個高速的彩色CCD圖像采集系統(tǒng)。

2012-03-22 12:11:30 73

73 本文結(jié)合實際應(yīng)用需要,設(shè)計了基于復(fù)雜可編程邏輯器件(CPLD)的線陣CCD數(shù)據(jù)采集系統(tǒng)。著重介紹了數(shù)據(jù)采集的特點及該系統(tǒng)軟、硬件設(shè)計和最后的性能評價。

2012-05-14 09:53:41 1773

1773

本文設(shè)計了一種基于CPLD(復(fù)雜可編程邏輯器件)+FX2(單片機CY7C68013)的便攜式高速數(shù)據(jù)采集系統(tǒng),采用了數(shù)據(jù)流驅(qū)動多模塊并行技術(shù)和USB2.0接口。實踐證明,該方案結(jié)構(gòu)簡單,成本低廉

2012-05-25 09:53:19 1954

1954

虛擬儀器技術(shù)以其開發(fā)高效、投入成本低等優(yōu)點,在動態(tài)測試及控制領(lǐng)域應(yīng)用越來越廣泛。文中基于虛擬儀器技術(shù)設(shè)計的的高速多通道信號采集系統(tǒng),用于爆炸應(yīng)力波測試,能夠同時測

2012-07-16 16:12:03 39

39 基于CPLD的多路音頻采集系統(tǒng),有需要的下來看看。

2016-01-21 11:07:07 29

29 Xilinx FPGA工程例子源碼:基于FPGA_CPLD和USB技術(shù)的無損圖像采集卡

2016-06-07 15:07:45 4

4 基于FPGA的新型高速CCD圖像數(shù)據(jù)采集系統(tǒng)

2016-09-22 13:05:38 22

22 基于CPLD高速數(shù)據(jù)采集系統(tǒng)設(shè)計_鮮果

2017-03-19 11:45:23 3

3 本文實現(xiàn)了一種基于CPLD控制的視頻采集模塊。CPLD主要通過視頻A/D的輸出狀態(tài)信號以及TMS320C6x DSP的相應(yīng)輸出控制信號生成FIFO的控制信號,實現(xiàn)視頻數(shù)據(jù)流的傳輸通路。這種純硬件實現(xiàn)

2017-10-20 11:11:48 31

31 CCD電荷耦合元件。可以稱為CCD圖像傳感器,也叫圖像控制器。CCD是一種半導(dǎo)體器件,能夠把光學(xué)影像轉(zhuǎn)化為電信號。 CCD上植入的微小光敏物質(zhì)稱作像素。一塊CCD上包含的像素數(shù)越多,其提供的畫面分辨率也就越高。

2017-12-14 16:46:54 34138

34138 圖1為基于FPGA和EPP技術(shù)對OV7620CMOS圖像傳感器的高速數(shù)據(jù)采集系統(tǒng)原理框圖,它主要由三部分組成:OV7620的參數(shù)配置電路、圖像采樣電路以及PC讀取數(shù)據(jù)電路。

2018-10-08 09:10:00 3973

3973 在對某多通道高速CCD相機輸出圖像信號的采集系統(tǒng)設(shè)計過程當(dāng)中,我們需要對此系統(tǒng)在正式使用之前進行調(diào)試,來測試它能否正常工作。本文利用CPLD和LVDS嚴格對CCD相機的輸出接口進行了模擬,并且以LVDS方式輸出圖像信號。

2018-10-08 08:30:00 4213

4213 關(guān)鍵詞:CPLD , 實時 , 視頻 , 圖像 , 芯片 圖像采集是實時圖像處理的重要步驟。目前,圖像傳感器件主要有CCD(Charge Coupled Device)和CMOS

2019-02-05 22:11:02 745

745 關(guān)鍵詞:光學(xué) , 光學(xué)技術(shù) , 光學(xué)材料 CCD 是一種半導(dǎo)體器件,能夠把光學(xué)影像轉(zhuǎn)化為數(shù)字信號。CCD 上植入的微小光敏物質(zhì)稱作像素(Pixel)。一塊 CCD 上包含的像素數(shù)越多,其提供的畫面

2019-02-08 09:08:01 11726

11726 ,廣泛地應(yīng)用于攝像器材、氣象、航天航空、軍事、醫(yī)療以及工業(yè)檢測等眾多領(lǐng)域。 在對某多通道高速CCD相機輸出圖像信號的采集系統(tǒng)設(shè)計過程當(dāng)中,我們需要對此系統(tǒng)在正式使用之前進行調(diào)試,來測試它能否正常工作。本文利用CPLD和LVDS嚴格對CCD相機的輸出接口進行了模

2019-02-12 09:01:01 883

883 優(yōu)化相關(guān)雙采樣( CDS) 控制參數(shù)可以提高電荷耦合器件( CCD) 輸出信噪比,但是高速CCD 的CDS 控制參數(shù)很難通過實驗確定。為了得到較好的CCD 輸出信噪比,提出了一種CDS 控制參數(shù)

2019-02-21 15:33:23 2

2 、高增益、實時并行處理等特點外,還具有容量大,體積小,功耗低等優(yōu)點。因而,采用聲光信號處理技術(shù)解決帶寬、高增益和實時并行處理問題具有重要意義,聲光信號的采集系統(tǒng)的設(shè)計是整個聲光系統(tǒng)關(guān)鍵之一。這里設(shè)計了一個基于FPGA和USB 2.0的高速CCD聲光信號采集系統(tǒng),為聲光信號采集提供了硬件平臺。

2019-03-12 08:45:17 2273

2273

設(shè)計了基于FPCA的CCD高速數(shù)據(jù)采集與處理系統(tǒng)。FPGA采用ALTERA公司EPlC6Q240C8,采用AD574實現(xiàn)模/數(shù)轉(zhuǎn)換,給出了其在QuartuslI環(huán)境下的仿真結(jié)果。實驗證明,該硬件電路結(jié)構(gòu)簡單、成本低廉、可靠性高、功耗較低,滿足了工程項目模塊化的要求。

2019-10-23 15:07:00 10

10 設(shè)計了一套高速線陣CCD信號采集系統(tǒng),采用FPGA+DSP的數(shù)字處理方案,能滿足光信號的實時識別和處理,可用于研究靜態(tài)和動態(tài)小粒子的光散射彩虹特性。

2019-11-21 17:32:39 27

27 介紹了基于CPLD的線陣CCD數(shù)據(jù)采集系統(tǒng)的硬、軟件構(gòu)成,工作原理及設(shè)計方案。采用TOSHIBA公司近年來推出的高速線陣CCD芯片TCD1209D,針對其驅(qū)動時序的要求,選用XILINX公司的復(fù)雜

2019-11-28 16:23:00 24

24 線型CCD圖像傳感器在工業(yè)檢測、圖像測量和機器視覺等方面有著廣泛的應(yīng)用。本文針對CCD測量應(yīng)用系統(tǒng)中的前端處理、驅(qū)動控制和信號采集,設(shè)計制作了一款基于FPGA的高速驅(qū)動采集一體化控制板。該控制板選用

2019-11-29 17:47:00 16

16 10ksps(samples per second)的連續(xù)數(shù)據(jù)

采集和傳輸而不丟失數(shù)據(jù),若要達到更

高速率的數(shù)據(jù)

采集,可以通過并行口通訊方式實現(xiàn)。當(dāng)前微機均可通過配置CMOS,將基地址為 378H的并行口設(shè)置為

EPP模式以支持通過數(shù)據(jù)口雙向傳輸通訊,并由芯片硬件自動產(chǎn)生握手

信號,實現(xiàn)

高速傳輸?shù)哪康摹?/div>

2020-04-08 10:21:18 1144

1144

為了提高數(shù)據(jù)采集卡的速度,同時降低成本,設(shè)計一種并行數(shù)據(jù)采集系統(tǒng),要求并行采集速度大于10 Mb/s。整個系統(tǒng)由AVR與CPLD控制實現(xiàn),通過MAXl308完成模數(shù)轉(zhuǎn)換,并設(shè)計搭建了其外圍電路。采用

2020-07-20 17:17:02 11

11 一、CCD簡介及CCD工作過程描述 CCD,中文全名:電荷耦合元件。可以稱為CCD圖像傳感器。CCD廣泛用于數(shù)字攝影,天文學(xué),尤其是光學(xué)遙測,光學(xué)和光譜望遠鏡以及高速攝影技術(shù)。CCD器件及其應(yīng)用技術(shù)

2020-11-30 14:46:36 15077

15077 介紹一種基于Actel公司Fusion StartKit FPGA的線陣CCD圖像數(shù)據(jù)采集系統(tǒng)。以FPGA作為圖像數(shù)據(jù)的控制和處理核心,通過采用高速A/D、異步FIFO、UART以及電平轉(zhuǎn)換、放大

2021-02-02 17:12:32 8

8 如何提升科研級CCD相機成像信噪比? 如果希望提升科研級CCD相機成像的信噪比,改善信號較弱時的成像質(zhì)量,在相機選型、使用中我們要注意哪些因素呢?大致可以從以下6個方面來綜合考慮:曝光時間,光學(xué)系統(tǒng)

2025-06-09 07:55:10 1019

1019

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論