介紹一種基于CPLD和嵌入式系統的高速數據采集系統,并詳細闡述了系統的結構和軟硬件的實現方案。

關鍵詞:高速數據采集;CPLD;嵌入式系統

Design and Implementation of High?speed Data Sampling System Ba sed on

CPLD and Embedded System

CPLD and Embedded System

LIN Dehui, DAO Kegang, DENG Yonggang, CHEN Sen

(Dept. of Information Engineering, China Institute of Metrology, Hang zhou 310018, China)

Key words: high?speed data sampling; CPLD; embedded system

1系統結構

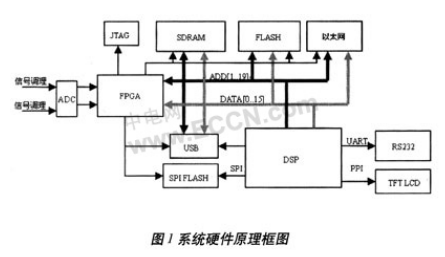

高速數據采集系統由高速ADC、CPLD、FIFO和嵌入式系統組成,系統結構如圖1所示。

高速數據采集系統由高速ADC、CPLD、FIFO和嵌入式系統組成,系統結構如圖1所示。

2.1嵌入式操作系統—Linux

Linux作為嵌入式操作系統有以下幾大優點:

(1)可應用于多種硬件平臺;(2)源代碼公開;(3)微內核直接提供網絡支持;(4)高度模塊化使添加部件非常簡單。

2.2硬件設計

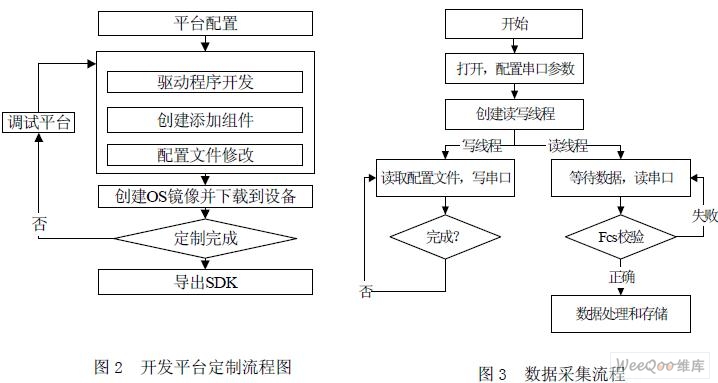

整個數據采集板采用雙層設計,上層是嵌入式系統的核心板,包括嵌入式系統CPU、FLASH和SDRAM等系統基本配置。MPC860的控制總線與數據總線通過核心板100線×3的接口插座與下面的擴展板各芯片通訊。硬件的結構框圖見圖2。

Linux作為嵌入式操作系統有以下幾大優點:

(1)可應用于多種硬件平臺;(2)源代碼公開;(3)微內核直接提供網絡支持;(4)高度模塊化使添加部件非常簡單。

2.2硬件設計

整個數據采集板采用雙層設計,上層是嵌入式系統的核心板,包括嵌入式系統CPU、FLASH和SDRAM等系統基本配置。MPC860的控制總線與數據總線通過核心板100線×3的接口插座與下面的擴展板各芯片通訊。硬件的結構框圖見圖2。

嵌入式系統的CPU選用Motorola的MPC860芯片。它內部集成了微處理器和一些控制領域的常用外圍組件,特別適用于互聯網絡和數據通信。MPC860 PowerQUICC通信處理器可以根據用戶的不同要求提供2~4個串行通信控制器、數據緩存,各種級別的網絡協議支持。該處理器專為寬帶接入設備如路由器、集線器、交換機和網關等設計。

2.2.2系統內存

系統內存由3部分組成,MPC860內部集成了4KB數據Cache,以及片外擴展的Flash和SDRAM。Flash為2片Am29LV160D,總容量為4MB×8bit,用來存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,總容量為16MB×8bit。

2.2.3通用外設

MPC860的4個串行通信控制器(SCC)支持以太網、HDLC/SDLC、HDLC總線(用以實現基于HDLC的局域網)、AppleTalk、UART、比特流透明傳輸、基于幀的透明傳輸(CRC可選)、支持PPP(Point to Point Protocol)的異步HDLC等標準協議,只需很少的外圍芯片就可以實現串行口和USB Slave接口。MPC860外擴一片LXT905PC就方便地實現了一個10BASE?T的以太網接口。

2.2.4嵌入式系統調試

MPC860處理器支持BDM(背景調試模式),完成板卡硬件檢測、下載、運行、燒寫FLASH、內核調試、單步調試等最底層的調測功能。在背景調試模式下,通過向CPU發送命令,可以實現對寄存器、系統存儲器的訪問。

另外,在調試時還可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC編譯環境在windows下進行應用程序的開發和調試。

2.2.5A/D轉換和CPLD電路

A/D采樣采用的器件為ADC08200,精度為8位,采樣頻率由20MSps至200MSps,本電路中的A/D采樣頻率為100MSps。CPLD芯片采用EPM3128ATC144-5,具有128個宏單元,可以提供2500個邏輯門,計數頻率上限為192.3MHz。A/D采樣時鐘由CPLD提供。晶振頻率為100MHz,直接接入到CPLD中,由CPLD產生累加電路的其他信號。

2.2.6CPLD器件的編程與調試

CPLD器件的編程采用VHDL語言。程序經過邏輯綜合(邏輯綜合的軟件為Altera公司的QuartusⅡ 4.0)后即可利用下載線通過JTAG(聯合測試行動組)接口將邏輯綜合生成的*.pof文件燒寫到CPLD器件中,然后即可測試芯片的功能。

2.2.7FIFO數據緩存電路

從圖1可以看出,系統中包含兩級FIFO。第一級FIFO芯片采用1片CY7C4251,容量為8KB×9bit,工作頻率為100MHz。第二級FIFO采用2片CY7C4255并聯,容量為8KB×36bit,但實際上只用了24bit數據寬度,因為8bit的A/D轉換數據累加10000次,24bit就能滿足系統的功能要求。

2.3軟件開發

該數據采集系統的軟件編程包括兩部分,一部分是MPC860嵌入式系統的編程;另一部分是CPLD的編程。關于CPLD的編程模式見2.2.6,這里只介紹嵌入式系統的軟件開發模式。

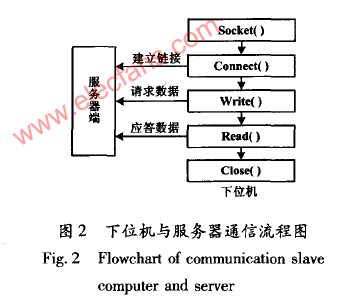

本系統采用交叉編譯的方式進行Linux應用程序的開發和調試,先將應用程序在宿主機上調試通過后,再移植到目標板。這種模式適合于大型復雜的應用,優點是程序調試方便但移植需要做一些工作。其開發流程如圖3所示。

2.2.2系統內存

系統內存由3部分組成,MPC860內部集成了4KB數據Cache,以及片外擴展的Flash和SDRAM。Flash為2片Am29LV160D,總容量為4MB×8bit,用來存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,總容量為16MB×8bit。

2.2.3通用外設

MPC860的4個串行通信控制器(SCC)支持以太網、HDLC/SDLC、HDLC總線(用以實現基于HDLC的局域網)、AppleTalk、UART、比特流透明傳輸、基于幀的透明傳輸(CRC可選)、支持PPP(Point to Point Protocol)的異步HDLC等標準協議,只需很少的外圍芯片就可以實現串行口和USB Slave接口。MPC860外擴一片LXT905PC就方便地實現了一個10BASE?T的以太網接口。

2.2.4嵌入式系統調試

MPC860處理器支持BDM(背景調試模式),完成板卡硬件檢測、下載、運行、燒寫FLASH、內核調試、單步調試等最底層的調測功能。在背景調試模式下,通過向CPU發送命令,可以實現對寄存器、系統存儲器的訪問。

另外,在調試時還可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC編譯環境在windows下進行應用程序的開發和調試。

2.2.5A/D轉換和CPLD電路

A/D采樣采用的器件為ADC08200,精度為8位,采樣頻率由20MSps至200MSps,本電路中的A/D采樣頻率為100MSps。CPLD芯片采用EPM3128ATC144-5,具有128個宏單元,可以提供2500個邏輯門,計數頻率上限為192.3MHz。A/D采樣時鐘由CPLD提供。晶振頻率為100MHz,直接接入到CPLD中,由CPLD產生累加電路的其他信號。

2.2.6CPLD器件的編程與調試

CPLD器件的編程采用VHDL語言。程序經過邏輯綜合(邏輯綜合的軟件為Altera公司的QuartusⅡ 4.0)后即可利用下載線通過JTAG(聯合測試行動組)接口將邏輯綜合生成的*.pof文件燒寫到CPLD器件中,然后即可測試芯片的功能。

2.2.7FIFO數據緩存電路

從圖1可以看出,系統中包含兩級FIFO。第一級FIFO芯片采用1片CY7C4251,容量為8KB×9bit,工作頻率為100MHz。第二級FIFO采用2片CY7C4255并聯,容量為8KB×36bit,但實際上只用了24bit數據寬度,因為8bit的A/D轉換數據累加10000次,24bit就能滿足系統的功能要求。

2.3軟件開發

該數據采集系統的軟件編程包括兩部分,一部分是MPC860嵌入式系統的編程;另一部分是CPLD的編程。關于CPLD的編程模式見2.2.6,這里只介紹嵌入式系統的軟件開發模式。

本系統采用交叉編譯的方式進行Linux應用程序的開發和調試,先將應用程序在宿主機上調試通過后,再移植到目標板。這種模式適合于大型復雜的應用,優點是程序調試方便但移植需要做一些工作。其開發流程如圖3所示。

系統總的工作過程為:由MPC860發送一個START高電平給EPM3128,EPM3128接收到此信號后,產生2000個10ns的脈沖信號給ADC08200,采樣后的數據存放在CY7C4251中。EPM3128產生CY7C4251的讀脈沖依次讀取FIFO中的數據并將其與從CY7C4255中取來的24位數據相加后再送回到CY7C4255中,每次累加在40ns中完成。這樣循環10000次,就完成了數據的累加。累加完成后,EPM3128發送IRQ中斷請求信號至MPC860,MPC860響應中斷在IO口上產生READ低電平讀信號,CPLD產生CY7C4255的讀使能信號將數據讀出送至三態緩沖器74F245,MPC860讀取數據時發送OE信號選通數據三態緩沖器74F245將數據讀出至MPC860數據總線,接收完數據通過 網口將數據發送給上位機處理。累加結果的讀取過程如圖4所示。

?

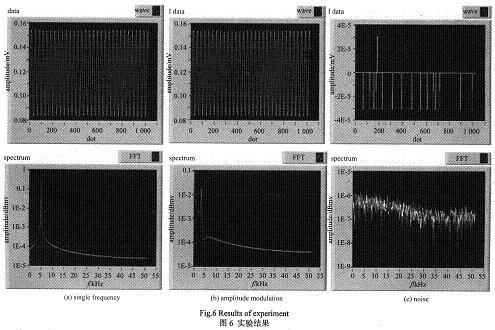

? 本文介紹的高速數據采集系統實現了分布式光纖溫度傳感器測溫系統中噪聲的有效抑制,具 有速度快、可靠性高的特點。另外由于CPLD的可編程性,可以對該電路板加以改造用在其他 的高速數據采集場合。

- 數據采集(120265)

相關推薦

熱點推薦

嵌入式系統采集圖像數據的遠程測量有什么優點?

隨著后PC時代的到來和嵌入式的蓬勃發展,運用嵌入式系統實現遠程數據采集已成為社會需求的趨勢。本文采用嵌入式系統采集圖像數據實現加工零件的遠程測量,代替傳統的人工檢測。其特點有:網絡化,準確性高,節約人力和物力。

2019-08-30 07:23:15

嵌入式系統怎么實現遠程監控和升級?

通用分組無線服務技術GPRS(General Packet Radio Service)是一種移動數據業務,該技術能滿足日常網絡行為,具有廣域覆蓋、高速傳輸等優點。野外作業的數據采集嵌入式系統工作于

2019-08-02 06:49:24

嵌入式單片機視頻報警系統的工作原理是什么?

利用以單片機應用系統為中心的小型嵌入式設備進行數據采集,并通過網絡有效傳輸數據,已成為數據采集領域的研究焦點。由于嵌入式單片機系統集單片機和嵌入式系統為一體,因此嵌入式單片機系統廣泛應用于那些對實時

2019-10-21 08:31:14

嵌入式多路信號數據采集系統有什么功能?

由于人們對數字形式信息的需求量越來越大,數據采集及其應用技術受到了越來越廣泛的關注和應用。隨著技術的發展,數據采集系統正向著高精度、高速度、穩定可靠和集成化的方向發展。目前,大多數的數據采集監控系統

2020-03-17 08:24:26

嵌入式電能計量及查詢系統有什么功能?

本文設計了一個既能接入宿舍電量采集系統又能接入校內 Intranet 信息網絡的嵌入式電能計量及查詢系統,在電能數據采集終端 (ERTU)采用嵌入式ARM2410 芯片和嵌入式實時操作系統Linux

2019-09-26 07:08:15

嵌入式視覺系統開發過程有什么技巧?

目前,關于視覺系統的研究已經成為熱點,也有開發出的系統可供參考。但這些系統大多是基于PC機的,由于算法和硬件結構的復雜性而使其在小型嵌入式系統中的應用受到了限制。上述系統將圖像數據采集后,視覺處理

2019-08-15 06:15:37

數據采集卡/分布式采集模塊/無線通訊采集模塊/嵌入式系統

無線通訊數據采集模塊:GPRSZIGBEE4. 嵌入式系統:嵌入式主板平板電腦工控一體機QQ2693330939郵箱2693330939@qq.com 電話:*** 聯系人江莽

2014-08-21 10:05:12

高速數據采集系統的硬件結構,CPLD在高速數據采集系統中的應用

高速數據采集系統的硬件結構MAX7000系列CPLD及其開發平臺介紹CPLD在高速數據采集系統中的應用

2021-04-08 06:11:56

ARM如何運用WINCE進行嵌入式視頻數據采集

設計、具有豐富的API等特點,廣泛用于嵌入式實時操作系統。這里提出的嵌入式圖像數據采集系統是某“納米技術與微系統”實驗室開發的“嵌入式傳感測控系統”中實現圖像采集功能的子系統,該系統是以S3C2440為硬件

2019-08-06 08:30:15

【Aworks申請】高速數據采集系統

的硬件支持,以及高效的嵌入式軟件支持,實現數據的高速采集與傳輸。步驟:基于高速CPU的ARM開發板,嵌入Linux,并且加入AD采集模塊與攝像頭模塊,以及無線傳輸模塊。確定相關功能,云共享,無線傳輸,快速采集,實時顯示,制定方案和計劃。

2015-07-17 14:43:58

【NanoPi2申請】fpga與嵌入式相結合的多媒體數據采集系統

優勢。項目描述:而要做高速信號處理,不得不借助于FPGA或DSP。最近在研究基于FPGA的數據采集系統,鑒于fpga在復雜時序上難以實現的瓶頸,故結合嵌入式的多媒體優勢,來實現FPGA采集信號,嵌入式驅動液晶以及其他多媒體設備的響應輸出。

2015-12-02 16:06:25

【OK210申請】嵌入式系統開發

申請理由:本次申請主要是為了熟悉嵌入式開發過程,以及嵌入式系統開發的深層次應用,如TCP協議,門禁系統,高速信息采集系統,物聯網應用等。項目描述:高速數據采集系統原理:利用開發板搭建的系統,加上

2015-07-17 14:21:27

一種基于嵌入式WinCE的遠程數據采集系統結構介紹

的使用前景[1]。本文以基于 WinCE 的嵌入式設備為核心,取代傳統意義上的PC 機,采用TCP/IP 通信機制搭建的遠程 數據采集系統,結合嵌入式設備和網絡技術的優點,將信號采集、信號傳輸和數據處理相對

2019-07-29 06:28:28

使用 ARM 和 CPLD 共同實現嵌入式數字圖像處理系統

的數字圖像處理平臺作為嵌入式機器人控制系統的一個子系統。我們采用一種ARM+CPLD+RAM結合的結構,在提供一定的控制能力的基礎上,保證了數據采集的快速和完整性。嵌入式數字圖像處理系統結構圖如下:該結構

2019-12-10 17:55:03

基于嵌入式Web Server的無線數據采集系統

與傳輸的應用范圍非常廣,涉及行業有電力、水利、公安、交通、石油、安防和金融等。上述設計實現了基于嵌入式Web Server的無線數據采集,主要用于車輛遙測、遠程無線抄表、工業數據采集系統、非接觸RF智能卡

2008-09-11 10:50:44

基于ARM與線性CCD的高速數據采集系統設計

接口,它使電路工作在更加平穩、簡潔而易丁控制,同時也提高了ARM的工作效率。為了提高通信速度,這里采用通用申行總線(USB)技術米與PC進行通信。ARM是用來控制主處理器的數據采集,數據的計算和數據傳輸。結果證明,整個系統能高效運作。該系統可應用于高速數據采集及多路模擬信號的工作環境下。

2023-09-26 07:41:28

如何實現基于Linux操作系統的嵌入式數據采集模塊的設計

湖南大學碩士學位論文基于Linux操作系統的嵌入式數據采集模塊設計與實現姓名:易斌申請學位級別:碩士專業:電路與系統指導教師:戴瑜興基于 Linux 操作系統的嵌入式數據采集模塊設計與實現摘要數據

2021-11-09 07:47:28

如何利用ARM7嵌入式單片機設計視頻報警系統?

利用以單片機應用系統為中心的小型嵌入式設備進行數據采集,并通過網絡有效傳輸數據,已成為數據采集領域的研究焦點。由于嵌入式單片機系統集單片機和嵌入式系統為一體,因此嵌入式單片機系統廣泛應用于那些對實時

2019-08-01 07:32:30

如何利用FPGA實現高速連續數據采集系統設計?

高速連續數據采集系統的背景及功能是什么?如何利用FPGA實現高速連續數據采集系統設計?FPGA在高速連續數據采集系統中的應用有哪些?

2021-04-08 06:19:37

如何去實現一種基于NAND FLASH的高速嵌入式系統設計呢

NAND Flash芯片系統可分為哪幾個區呢?如何去實現一種基于NAND FLASH的高速嵌入式系統設計呢?

2021-12-27 06:31:01

怎么實現串行閃存小體積的數據采集系統設計?

本文介紹了一種基于AD、CPLD、串行閃存來實現的小體積的數據采集系統。與其他數據采集系統相比,該系統體積小,存儲器便于控制,易于升級存儲器的容量,能夠滿足一般的信號采集。不足是系統的采樣頻率不夠高,只能達到250kHz/S,不適于高頻信號的采集。

2021-04-07 06:48:52

怎么實現基于Nios軟核的嵌入式Internet系統設計?

介紹如何在Altera開發平臺上,使用Nios軟核CPU來構建嵌入式Internet系統;并結合以太網遠程數據采集系統的實例,介紹此類系統硬件,軟件的設計方法。

2021-06-04 07:05:47

怎樣使用ZYNQ做一個高速數據采集系統

關注、星標嵌入式客棧,精彩及時送達[導讀] 最近使用ZYNQ做一個高速數據采集,需要訪問一個ADI的高速模數采樣芯片,該芯片是利用三線制實現讀以及寫的功能。三線制實現寫通信或許大家都經常...

2022-02-17 06:33:06

用ARM和FPGA怎么設計便攜式人工地震數據采集系統?

Linux技術,實現一種小型化、移動性強、網絡耦合度高的便攜式人工地震數據采集系統。該系統以滿足人工地震觀測的需要、減小儀器尺寸和重量、降低功耗、降低野外工作強度和提高數據采集工作效率為目標。

2020-03-05 06:20:45

采用ADC技術實現MCU系統數據采集方案

使用MCU的系統設計人員受益于摩爾定律,即通過更小封裝、更低成本獲得更多的豐富特性功能。嵌入式系統設計人員和MCU廠商關心數據采集系統的三個基本功能:捕獲、計算和通信。理解全部功能對設計大有幫助,本文將主要關注數據采集系統的捕獲階段。

2019-07-17 07:21:16

采用PCI總線流水式高速數據采集系統設計

采用PCI總線流水式高速數據采集系統設計摘要:目前基于PCI總線的高速數據采集系統,大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設計,其通用性、靈活性差,不能

2009-10-30 15:09:49

USB- HOST實時數據采集嵌入式模塊的實現

提出利用SL811HS 和8 位單片機實現USB-Host 實時數據采集嵌入式模塊。該系統的數據傳輸,遵守大規模存儲協議和USB 1.1協議規范,可作為嵌入式設備的數據輸入輸出模塊。它以文件的形

2009-04-15 09:24:19 13

13

13

13基于uCLinux的嵌入式實時遠程數據采集系統

提出一種基于嵌入式操作系統的可遠程監測的新型數據采集系統的設計方案. 本系統以嵌入式處理器芯片S3C44B0X作為數據采集及存儲的控制核心,并引入了uClinux多任務操作系統. 具

2009-04-24 10:45:44 22

22

22

22USB- HOST 實時數據采集嵌入式模塊的實現

提出利用SL811HS 和8 位單片機實現USB-Host 實時數據采集嵌入式模塊。該系統的數據傳輸,遵守大規模存儲協議和USB 1.1協議規范,可作為嵌入式設備的數據輸入輸出模塊。它以文件的形

2009-05-16 14:57:48 13

13

13

13基于嵌入式TCP/IP 技術的海水數據采集系統

介紹基于嵌入式TCP/IP 技術的海水實時數據采集系統。網絡接口模塊和數據采樣控制模塊分別由單片機實現,兩者通過高速FIFO 緩存技術在本地進行無縫連接,以滿足高速數據采集時

2009-05-30 09:02:54 26

26

26

26基于Linux的嵌入式數據采集系統

數據采集系統是集計算機、通信及電子技術、工業控制為一體的綜合探測系統。本文介紹了基于嵌入式Linux 的數據采集系統的硬件結構和軟件設計。為提高系統的實時響應性能和

2009-06-20 09:55:17 28

28

28

28基于嵌入式網絡模塊的HTTP 數據采集方案

基于嵌入式網絡模塊的HTTP 數據采集方案:摘要:本文提出了一種在單片機系統中實施基于HTTP 協議的數據采集的方案,利用嵌入式網絡模塊實現串口到以太網數據的轉換,使用采集

2009-06-21 22:39:44 18

18

18

18基于PCI總線的高速數據采集卡系統設計與實現

基于PCI總線的高速數據采集卡系統設計與實現:本文介紹一種基于PCI總線的高速數據采集卡系統的設計方法,討論了設計高速數據采集系統的關鍵技術,給出了系統整體設計方案和P

2009-06-22 19:04:54 55

55

55

55基于TTL串口的嵌入式USB主機系統的設計和實現

本文介紹了一種基于TTL 串口的嵌入式USB 主機系統。介紹了該系統的硬件實現,以及USB 主機的底層驅動軟件的實現,并簡要介紹其在數據采集系統領域中的應用。關鍵字:嵌入式

2009-08-15 08:23:47 29

29

29

29嵌入式大容量數據采集系統設計

設計了一種基于AT91RM9200 微處理器的工業監控現場嵌入式大容量數據采集系統,簡化了現場設備層的布線難度,減小了現場設備模擬信號在傳輸過程中的衰減程度,為后期設備故

2009-08-22 10:17:08 9

9

9

9基于嵌入式網絡模塊的HTTP數據采集方案

本文提出了一種在單片機系統中實施基于HTTP 協議的數據采集的方案,利用嵌入式網絡模塊實現串口到以太網數據的轉換,使用采集板將數據封裝成HTTP 包.該方案靈活方便,實現簡單

2009-08-26 15:11:27 16

16

16

16基于嵌入式操作系統的數據采集系統

提出了一種以ARM7 處理器LPC2210 和實時嵌入式操作系統uc/os-II 為基礎的數據采集方案。該方案采用模塊化結構和合理任務分配策略,使得系統軟件便于編制和調節,實現了多通道高速

2009-09-03 15:46:21 18

18

18

18基于CPLD的雷達高度表數據采集系統設計

本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達高度表高速大容量數據采集存儲系統,分析了系統組成和設計思想,著重對CPLD 實現的功能做了介紹并給出了代表信號

2009-09-18 11:09:30 11

11

11

11基于CPLD與單片機的高速數據采集系統

本文針對新型匝間耐壓測試儀中需要高速采集數據的問題提出了一種結合CPLD 與單片機的高速數據采集系統設計方案。CPLD 產生A/D 芯片的控制時序以及SRAM 的讀寫控制時序,單片機輸

2009-12-23 14:59:57 88

88

88

88基于嵌入式Linux的遠程數據采集系統

提出一種基于嵌入式Linux 系統的遠程數據采集的設計方案,采用ARM9 體系結構的嵌入式處理芯片S3C2410X 作為系統的控制芯片、高實時性的嵌入式Linux 多任務實時操作系統和Qt/Embedded

2009-12-31 14:04:41 17

17

17

17基于嵌入式WinCE的遠程數據采集系統

設計了一種基于嵌入式WinCE 的遠程數據采集系統。利用分層技術在PB(PlatformBuilder)集成開發環境中定制基于WinCE 的開發平臺,分別采用Host Link 協議和自定義協議設計了采集器與P

2009-12-31 14:29:11 21

21

21

21基于Xscale的嵌入式農田數據采集系統

在精細農業技術體系中,農田數據采集是基礎性工作,也是我國相關研究的薄弱環節。針對這種需求,本文設計了一種嵌入式農田數據采集系統。本系統能夠完成農田空間信息采

2010-01-07 11:45:34 11

11

11

11嵌入式實時數據采集系統的設計與實現

設計了一種基于ARM9 與Linux 的嵌入式實時數據采集系統。通過對數據采集實時理論的研究和對系統應用需求的分析選擇設計了系統的軟硬件,其中主要包括基于AD7892的采集模塊硬

2010-01-13 15:45:11 29

29

29

29基于FPGA的超高速數據采集與處理系統

介紹了一種基于FPGA 的超高速數據采集與處理系統,給出了系統實現的方案,并詳細闡述了各硬件電路的具體構成。對系統軟件功能做了簡要介紹,并利用嵌入式邏輯分析儀對該超高

2010-01-20 16:03:27 58

58

58

58基于ARM+μC/OS-II的嵌入式數據采集系統設計

基于ARM+μC/OS-II的嵌入式數據采集系統設計摘 要:比較了常見的幾種數據采集系統方案,說明了基于ARM 的嵌入式系統方案的優勢。通過移植μC/OS-II 操作系統到

2010-05-30 17:06:27 36

36

36

36銀河數據采集分析系統

驅動系統綜合測試儀等硬件設備完成數據的高速采集,實時上傳用戶自定義的波形數據和特征值數據。數據采集系統可以同時監控局域網內的1臺或多臺設備的測量數據,并進行數據的

2024-10-08 13:33:21

換體DMA高速數據采集電路的CPLD實現

換體DMA高速數據采集電路的CPLD實現

介紹了換體DMA高速數據采集電路原理及其CPLD實現。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 1008

1008

1008

1008

CPLD在多路高速同步數據采集系統中的應用

CPLD在多路高速同步數據采集系統中的應用

CPLD(Complex Programmable Logic Device,復雜可編程邏輯器件)是在傳統的PAL、GAL基礎上發展而來的,具有多種工作方式

2009-03-28 16:49:00 1302

1302

1302

1302

利用CPLD實現多路數據采集

設計了以CPLD為核心處理芯片的多路數據采集系統,整個數據采集系統可實現最大采集頻率為800kHz,通道數為48路的模擬信號的采集。系統中采用了TI公司最新推出的高速低功耗A/D

2009-05-05 20:04:02 2054

2054

2054

2054

基于CPLD和FIFO的多通道高速數據采集系統的研究

介紹了一種基于CPLD(復雜可編程邏輯器件)和FIFO(先入先出存儲器)的多通道高速A/D數據采集系統的設計方法,并給出了這種數據采集方法的硬件原理電路和主要的軟件設計思路

2009-05-05 20:50:09 1964

1964

1964

1964

高速數據采集系統中精確時標的CPLD實現方法

高速數據采集系統中精確時標的CPLD實現方法

本文介紹一種利用復雜可編程邏輯器件給高速數據采集系統中的采集數據貼上精確時間標簽的方法,并

2009-07-20 12:42:23 828

828

828

828基于CPLD/FPGA高速數據采集系統的設計

基于CPLD/FPGA高速數據采集系統的設計

0 引 言 傳統的數據采集系統一般采用單片機,系統大多通過PCI總線完成數據的傳輸。其缺點是數學運算能力差;

2010-01-27 09:35:01 791

791

791

791

基于LabVIEW和ARM嵌入式數據采集與遠程傳輸控制系統

基于LabVIEW和ARM嵌入式數據采集與遠程傳輸控制系統

基于嵌入式網絡的遠程數據采集系統具有不受地理環境、氣候、時間的影響,小型便攜,使用靈活方便,交互操作

2010-03-10 11:33:18 4836

4836

4836

4836

基于嵌入式WinCE的遠程數據采集系統

基于嵌入式WinCE的遠程數據采集系統

摘要:設計了一種基于嵌入式WinCE的遠程數據采集系統。利用分層技術在PB(Platform. Builder)集成開發環境中

2010-04-01 15:47:26 1098

1098

1098

1098

嵌入式LabVIEW調用DLL實現數據采集

為了實現便攜式高精度檢波器測試儀的數據采集和信號處理,本文研究了嵌入式系統中開發LabVIEW 應用程序的方法。本文以ARM+Windows CE 為平臺進行了檢波器測試儀的軟硬件設計。分析了

2011-05-24 18:17:17 73

73

73

73基于嵌入式USB接口的數據采集系統的設計

USB接口 的通用性和簡便性使其成為數據采集系統與嵌入式系統進行數據傳輸的理想選擇。因此,設計一款以單片機控制 MAX197 芯片進行模數轉換,以及通過USB接口芯片PDIUSBD12進行數據傳

2011-06-08 16:22:55 53

53

53

53嵌入式多路信號數據采集系統

隨著技術的發展,數據采集系統正向著高精度、高速度、穩定可靠和集成化的方向發展。目前,大多數的數據采集監控系統都是獨立的系統,只能進行數據的現場采集或存儲,已不能滿

2011-09-08 16:39:44 2382

2382

2382

2382

基于IPV6的嵌入式數據采集系統設計

本文以工業生產中的“網絡化數據采集系統”這一實際應用為討論研究對象,借此來說明基于IPv6協議的嵌入式Internet系統的硬件與軟件設計。在本設計中,系統研制過程中設計的技術主要有

2011-10-13 15:12:05 1412

1412

1412

1412

高速數據采集系統中CPLD的應用

CPLD在高速數據采集系統中的應用! 介紹了高速數據采集系統的整體框架分析了其中的通用部分CPLD系列產品的特點及其開發軟件.CPLD根據高速數據采集系統的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26

26

26基于CPLD的高速數據采集系統的實現

本文設計了一種基于CPLD(復雜可編程邏輯器件)+FX2(單片機CY7C68013)的便攜式高速數據采集系統,采用了數據流驅動多模塊并行技術和USB2.0接口。實踐證明,該方案結構簡單,成本低廉

2012-05-25 09:53:19 1954

1954

1954

1954

基于32位低端嵌入式系統的圖像采集模塊

本文介紹了一個在低端嵌入式系統中增加圖像采集功能的實現方案。MT9V011 CMOS數字圖像傳感器應用于基于飛利浦低端ARM7處理器的嵌入式系統中,系統通過1片CPLD讀取MT9V011采集的圖像,并

2012-05-29 14:11:28 1729

1729

1729

1729

Windows CENET在高速實時數據采集系統中可移植性的研究

本文在現有產品的基礎上提出了在高速實時數據采集系統中采 用“數字信號處理芯片嵌入式中央處理器”的設計思路,即將高速實時數據采集系統分成基于三星公司的S3C2410精簡指令處理器的核心板和基于現場

2016-04-18 10:02:17 0

0

0

0嵌入式高速實時數據采集系統設備驅動程序的研究

在高速實時數據采集系統設計中 我們采用了“數字信號處理芯片 + 嵌入式中央處理器”的設計思路即將高速實時數據采集系統分成基于三星公司的S3C2410精簡指令處理器的核心板和基于現場可編程門陣列的高速

2016-04-18 14:12:30 1

1

1

1高速數據采集卡和嵌入式PC

Innovative Integration公司推出了基于新一代嵌入式計算機架構VPX的超高速數據采集產品。它符合OpenVPX(VITA65)標準。它采用PCIe2代的標準,每個Lane可以達到5Gbps。

2017-09-19 16:51:59 10

10

10

10基于嵌入式系統的圖像數據采集系統設計

隨著后PC時代的到來和嵌入式的蓬勃發展,運用嵌入式系統實現遠程數據采集已成為社會需求的趨勢。本文采用嵌入式系統采集圖像數據實現加工零件的遠程測量,代替傳統的人工檢測。其特點有:網絡化,準確性高,節約人力和物力。

2019-11-04 16:58:50 2981

2981

2981

2981

如何使用AVR和CPLD實現高速數據采集系統的設計

為了提高數據采集卡的速度,同時降低成本,設計一種并行數據采集系統,要求并行采集速度大于10 Mb/s。整個系統由AVR與CPLD控制實現,通過MAXl308完成模數轉換,并設計搭建了其外圍電路。采用

2020-07-20 17:17:02 11

11

11

11剖析Blackfin及嵌入式ktClinux在數據采集系統中的應用

本文介紹了一款高性價比的嵌入式處理器,并提供了帶USB、以太網、TFT LCD的嵌入式數據采集系統解決方案,以及BT5

2021-04-06 11:11:59 2186

2186

2186

2186

基于PIC總線的高速數據采集系統

本文詳細介紹了一種基于 PCI 總線的高速數據采集系統的原理、組成和功能以及在 Windows 2000 環境下進行數據采集和存儲的方法。該系統用于某型號衛星下行的高速數據采集。系統設計與技術的通用性可應用于其它類似的高速數據采集與處理系統中。

2021-04-14 14:29:30 13

13

13

13基于嵌入式linux的數據采集系統設計與實現,基于linux操作系統的嵌入式數據采集模塊設計與實現.docx...

湖南大學碩士學位論文基于Linux操作系統的嵌入式數據采集模塊設計與實現姓名:易斌申請學位級別:碩士專業:電路與系統指導教師:戴瑜興基于 Linux 操作系統的嵌入式數據采集模塊設計與實現摘要數據

2021-11-03 20:36:05 9

9

9

9 電子發燒友App

電子發燒友App

評論