在最近幾年中日益流行在高性能嵌入式應(yīng)用中使用現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)。FPGA已經(jīng)被證明有能力處理各種不同的任務(wù),從相對(duì)簡(jiǎn)單的控制功能到更加復(fù)雜的算法操作。雖然FPGA在某些功能上比ASIC硬件具有時(shí)間和成本上的優(yōu)勢(shì),但在面向軟件應(yīng)用中的FPGA比傳統(tǒng)處理器和DSP的優(yōu)勢(shì)并沒(méi)有體現(xiàn)出來(lái)。這很大程度上是由于過(guò)去割裂了硬件和軟件開(kāi)發(fā)工具和方法之間的關(guān)系。

然而最近FPGA在軟件設(shè)計(jì)工具方面的發(fā)展,及器件容量的持續(xù)增加為軟件開(kāi)發(fā)者創(chuàng)造了新的環(huán)境。在這種環(huán)境下,F(xiàn)PGA可視為軟件編譯器的一個(gè)可能的目標(biāo)。現(xiàn)在,工具能夠幫助軟件工程師利用FPGA平臺(tái),同時(shí)在結(jié)合了傳統(tǒng)處理器(或軟處理器核)和FPGA的單一目標(biāo)平臺(tái)上,幫助這些開(kāi)發(fā)者利用其所具有的高度算法并行性。

基于FPGA的計(jì)算平臺(tái),尤其是那些具有嵌入式“軟”處理器的平臺(tái),有能力實(shí)現(xiàn)非常高性能的應(yīng)用。通過(guò)使用最新一代的硬件/軟件協(xié)同設(shè)計(jì)工具,有可能使用多種面向軟件的設(shè)計(jì)方式作為FPGA設(shè)計(jì)過(guò)程的一部分。

使用基于FPGA的參考平臺(tái)

FPGA中使用嵌入式處理器的優(yōu)勢(shì)之一是能夠在單個(gè)可編程器件上建立硬件/軟件開(kāi)發(fā)對(duì)象——等效硬件參考平臺(tái)。 快速下載和測(cè)試新的軟件/硬件配置的能力也能大大提高設(shè)計(jì)率。通過(guò)使用嵌入式處理器作為測(cè)試生成器,單獨(dú)的硬件部件也可以快速地驗(yàn)證功能。

這種快速原型平臺(tái)的典型例子是Altera公司提供的Nios開(kāi)發(fā)包。Cyclone或Stratix FPGA中都包括這個(gè)工具包,除了高性能的Nios 32位軟核處理器核之外還包括多種硬件和軟件外設(shè)接口。在設(shè)計(jì)過(guò)程中可以選擇這種核,使用Altera SOPC Builder工具配置并下載到相應(yīng)的FPGA中。板上本身的連接容許直接和各種不同的外部部件連接,從串口(RS232和USB)到Flash存儲(chǔ)器和網(wǎng)絡(luò)接口。

在開(kāi)發(fā)過(guò)程中使用這種板子并結(jié)合Altera工具,容許嵌入式系統(tǒng)設(shè)計(jì)者用應(yīng)用原型所需的部件(包括嵌入式處理器)組成目標(biāo)平臺(tái)。然后,軟件開(kāi)發(fā)者能夠關(guān)注應(yīng)用本身,分析和試驗(yàn)不同的硬件/軟件劃分方案。

權(quán)衡硬件和軟件資源

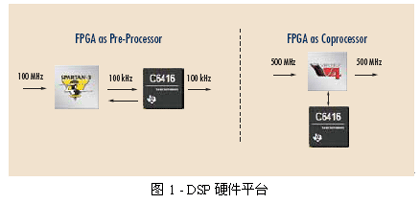

在一些高性能嵌入式應(yīng)用中,從產(chǎn)品構(gòu)建費(fèi)用和開(kāi)發(fā)成本考慮最佳的資源使用方案是混合處理器方案。在這種方案中非關(guān)鍵性能的功能由主處理器實(shí)現(xiàn)(它們可能是或不是嵌入式處理器核),而大計(jì)算量的部件是一個(gè)或多個(gè)DSP芯片、或者其它專(zhuān)用ASIC或FPGA。這種的解決方案通常需要豐富的硬件設(shè)計(jì)和工具的知識(shí),但是在性能和成本方面上具有最佳的收益。

對(duì)于系統(tǒng)中的每個(gè)處理單元(即標(biāo)準(zhǔn)處理器、DSP、FPGA或ASIC),需要不同水平的專(zhuān)用技能。例如,雖然DSP是軟件可編程的,在工具上的初期投入小,但他們需要在DSP專(zhuān)門(mén)的設(shè)計(jì)技術(shù)方面有一些專(zhuān)門(mén)經(jīng)驗(yàn),通常需要匯編級(jí)的編程技能。在另一方面,F(xiàn)PGA在設(shè)計(jì)和工具經(jīng)驗(yàn)上需要相對(duì)高的投入,在硬件設(shè)計(jì)語(yǔ)言作為主要的設(shè)計(jì)輸入方式時(shí)尤其如此。

然而FPGA和專(zhuān)用ASIC設(shè)計(jì)所需的經(jīng)驗(yàn)和工具投入相比,顯然FPGA在開(kāi)發(fā)專(zhuān)用硬件上具有更低的風(fēng)險(xiǎn)。的確,相對(duì)于專(zhuān)用ASIC方案的簡(jiǎn)單性和低風(fēng)險(xiǎn)的設(shè)計(jì)過(guò)程是選擇FPGA的關(guān)鍵因素。最近基于軟件的FPGA設(shè)計(jì)工具使這種設(shè)計(jì)過(guò)程獲得更大的效率。這反過(guò)來(lái)讓系統(tǒng)設(shè)計(jì)者和軟件應(yīng)用開(kāi)發(fā)者在實(shí)際的硬件上能夠更快地嘗試新的算法方式,使用迭代方式進(jìn)行設(shè)計(jì)。

這種迭代方式重要好處是能夠一次改變一個(gè)單元(例如將關(guān)鍵的算法移至FPGA)。應(yīng)用最初是完全用軟件進(jìn)行原型設(shè)計(jì),并驗(yàn)證其正確性,然后由FPGA完成特定的功能,這是在每個(gè)步驟都要對(duì)系統(tǒng)重新進(jìn)行驗(yàn)證的硬件實(shí)現(xiàn)過(guò)程。這種方式被證實(shí)能大大地縮短調(diào)試時(shí)間,降低引入難以調(diào)試的系統(tǒng)錯(cuò)誤的風(fēng)險(xiǎn)。

你如何在考慮“將設(shè)計(jì)的哪部分以硬件實(shí)現(xiàn)”上做出最明智的選擇?一個(gè)普遍采用的方式是從用C,Matlab,SystemC或其它一些軟件編程語(yǔ)言的軟件模型開(kāi)始。隨著應(yīng)用模型和部件算法的發(fā)展,設(shè)計(jì)者確定并發(fā)揮設(shè)計(jì)中的并行性(或重新設(shè)計(jì)算法),利用可編程硬件在建立并行結(jié)構(gòu)方面的獨(dú)有能力。增加并行度通常轉(zhuǎn)化為增加硬件資源。使用軟件模型驗(yàn)證假設(shè),建立可重復(fù)的測(cè)試組,這些測(cè)試組可以作為模型,進(jìn)一步提煉可以進(jìn)行軟件和硬件編譯的內(nèi)容。

混合軟硬件設(shè)計(jì)方法

現(xiàn)今如何開(kāi)發(fā)混合軟件和硬件應(yīng)用呢?如果設(shè)計(jì)是軟件驅(qū)動(dòng)的(現(xiàn)今越來(lái)越多的設(shè)計(jì)是這樣),軟件或系統(tǒng)工程師從編寫(xiě)代碼(如上所述)來(lái)建立系統(tǒng)原型。 另一種是,工程師用更高級(jí)的工具如Simulink(來(lái)自Mathworks),基于UML的工具或其它系統(tǒng)設(shè)計(jì)環(huán)境開(kāi)始。 在這個(gè)過(guò)程中,系統(tǒng)設(shè)計(jì)者或軟件工程師將采用更高級(jí)的設(shè)計(jì)抽象以獲得最大的效率,但是可能獲得很低的性能結(jié)果。因?yàn)橐赃@種方式自動(dòng)選用的處理器類(lèi)型是受限的,為性能轉(zhuǎn)換低級(jí)代碼的機(jī)會(huì)相對(duì)更少。有經(jīng)驗(yàn)的嵌入式開(kāi)發(fā)者可能會(huì)進(jìn)一步用匯編語(yǔ)言?xún)?yōu)化應(yīng)用的各個(gè)部分,或使用專(zhuān)用處理器(即DSP芯片)來(lái)提高性能。硬件工程師可以參與優(yōu)化面向FPGA和ASIC實(shí)現(xiàn)的設(shè)計(jì)中的那部分接口。

初始系統(tǒng)設(shè)計(jì)和劃分完成之后,需要最高性能的各個(gè)部分可以手工描述出來(lái),交給硬件工程師。工程師為FPGA或ASIC部分編寫(xiě)低層的HDL代碼,他們的設(shè)計(jì)生產(chǎn)率通常非常低(軟件工程師1/10或更少)。結(jié)果是系統(tǒng)速度增加了,但是代碼和最初的軟件代碼無(wú)法對(duì)應(yīng),設(shè)計(jì)周期不再一致,系統(tǒng)規(guī)格的改變可能很痛苦。

在這種情況下,系統(tǒng)設(shè)計(jì)者必須作為硬件/軟件仲裁者,指定硬件/軟件接口,鎖定設(shè)計(jì)反映設(shè)計(jì)的前期時(shí)間。一旦硬件開(kāi)發(fā)認(rèn)真地展開(kāi),可能幾乎沒(méi)有機(jī)會(huì)再次從整體上把握。

基于C的設(shè)計(jì)和原型工具加速開(kāi)發(fā)過(guò)程

在上述的方式中,最終的設(shè)計(jì)是軟件和硬件源文件的組合。 一些需要軟件的編譯/調(diào)試工具流程,其它需要硬件設(shè)計(jì)流程和專(zhuān)業(yè)知識(shí)。 然而,隨著基于C的FPGA設(shè)計(jì)工具的出現(xiàn),使得在大部分的設(shè)計(jì)中可以采用熟悉的標(biāo)準(zhǔn)C語(yǔ)言,尤其在那些本身就是實(shí)現(xiàn)算法的硬件電路。 后面的性能轉(zhuǎn)換可能會(huì)引入手工的硬件描述語(yǔ)言(HDL)取代自動(dòng)生成的硬件(正如面向DSP處理器的源代碼通常用匯編重新編寫(xiě)),但是因?yàn)樵O(shè)計(jì)直接從C代碼編譯成最初的FPGA實(shí)現(xiàn),硬件工程師要參與性能轉(zhuǎn)換的時(shí)間會(huì)進(jìn)一步提早至設(shè)計(jì)階段,系統(tǒng)可以用更高效率的軟件設(shè)計(jì)模式來(lái)進(jìn)行設(shè)計(jì)。

CoDeveloper工具(Impluse Accelerated Technologies提供)允許C語(yǔ)言的應(yīng)用編譯后以FPGA網(wǎng)表形式建立硬件,包括允許描述高度并行和多過(guò)程應(yīng)用描述所必須的C語(yǔ)言擴(kuò)展。對(duì)于包括嵌入式處理器(如Altera的Nios軟核處理器)的目標(biāo)平臺(tái),CoDeveloper可以用來(lái)生成必要的硬件/軟件接口,及生成特定過(guò)程的低級(jí)硬件描述。

采用這種工具和硬件/軟件方式獲得成功的關(guān)鍵是軟件和硬件處理資源之間合理的劃分。好的劃分方案不僅要考慮給定算法部件對(duì)計(jì)算量的需求,而且要考慮數(shù)據(jù)帶寬需求。這是因?yàn)橛布?軟件接口可能是主要的性能瓶頸。

合理地利用高并行應(yīng)用的編程模型也很重要。雖然它試圖用傳統(tǒng)編程方式如遠(yuǎn)程過(guò)程調(diào)用(RPC)將特定功能交由FPGA處理,但是研究表明面向數(shù)據(jù)流的通信方式更有效率,它不可能引入阻塞或造成應(yīng)用死鎖。在一些情況下,這意味著重新從整體上考慮設(shè)計(jì),尋找新的方式對(duì)數(shù)據(jù)進(jìn)行搬移和處理。這么做的結(jié)果是非常顯著的:通過(guò)增加應(yīng)用級(jí)的并行性,充分利用可編程邏輯資源,這可能將使一般算法比純軟件實(shí)現(xiàn)提升幾個(gè)數(shù)量級(jí)。

在這種應(yīng)用的開(kāi)發(fā)過(guò)程中(或重新工程化),設(shè)計(jì)工具是可視化的,能調(diào)試多個(gè)并行過(guò)程的互連。工具有助于量化地給出劃分方式的結(jié)果,識(shí)別可能表示應(yīng)用瓶頸的高數(shù)據(jù)吞吐量的區(qū)域。用戶(hù)可以在工具的幫助下,進(jìn)行更詳細(xì)的分析和性能調(diào)整。

圖1,在應(yīng)用調(diào)試和監(jiān)視過(guò)程中連接硬件和軟件過(guò)程

設(shè)計(jì)實(shí)例:基于FPGA的圖像慮波器

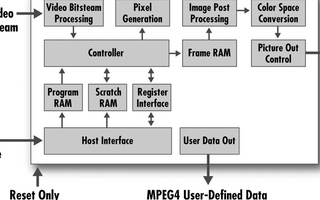

為了演示這些工具如何用來(lái)把算法過(guò)程移至FPGA,我們以圖像慮波器為例,其中輸入數(shù)據(jù)流必須非常快速地處理,生成輸出數(shù)據(jù)流。這樣的問(wèn)題可能涉及大量的計(jì)算,而且也是對(duì)帶寬要求非常高。

圖2說(shuō)明一個(gè)簡(jiǎn)單的圖像慮波器如何工作。在所示的示例中(邊緣檢測(cè)慮波器),尤其是3×3窗口的像素?cái)?shù)據(jù)必須以流方式組合和處理。

圖2,圖像慮波器過(guò)程一次處理輸入圖像一個(gè)像素,在最近的八個(gè)像素進(jìn)行卷積

有許多可能的方法實(shí)現(xiàn)這種算法。在本例中,兩個(gè)流水式硬件處理器用C描述完成這種功能:一個(gè)過(guò)程生成匹配源圖像的匹配行像素(以像素流讀取),同時(shí)第二個(gè)過(guò)程接受第一個(gè)過(guò)程的數(shù)據(jù)流的結(jié)果,將對(duì)每個(gè)像素窗口卷積,生成一個(gè)輸出圖像,用第二個(gè)過(guò)程中單一的卷積像素流表示。這個(gè)過(guò)程和流用Impulse C庫(kù)(見(jiàn)附文《Impluse C編程模型》)提供的C兼容的流I/O例程來(lái)聲明和讀/寫(xiě)。

因?yàn)樗惴ㄊ怯脴?biāo)準(zhǔn)C(外加Impulse C庫(kù))描述的,我們能從軟件設(shè)計(jì)(用Microsoft Visual Studio開(kāi)發(fā))開(kāi)始,它在桌面仿真環(huán)境下完成圖像算法。這種設(shè)計(jì)將兩種硬件過(guò)程和圖像卷積功能結(jié)合到軟件臺(tái)設(shè)計(jì)中(它可以編譯,并以基于PC的臺(tái)式機(jī)應(yīng)用或運(yùn)行在Nios處理器中的嵌入式應(yīng)用運(yùn)行),它從TIFF格式文件中讀取數(shù)據(jù)進(jìn)行處理。這種設(shè)計(jì)可以用標(biāo)準(zhǔn)桌面調(diào)試工具和CoDeveloper Application Monitor進(jìn)行設(shè)置和運(yùn)行。在這種方式下,算法結(jié)果可以在編譯到FPGA平臺(tái)之前進(jìn)行驗(yàn)證。

編譯為硬件

用標(biāo)準(zhǔn)桌面C開(kāi)發(fā)工具仿真它的功能之后,我們準(zhǔn)備用Altera Stratix開(kāi)發(fā)原型板,在混合FPGA/處理器目標(biāo)上實(shí)現(xiàn)該應(yīng)用。Altera Nios開(kāi)發(fā)包包括所有編譯和綜合至FPGA所需的硬件和軟件(包括自動(dòng)生成的硬件過(guò)程的HDL源文件和表示軟件過(guò)程的C源代碼)。Altera提供的軟件結(jié)合Impulse CoDeveloper,為我們提供了從C語(yǔ)言編譯和執(zhí)行測(cè)試應(yīng)用所需的一切。

我們第一步是為圖像濾波器本身生成硬件。為了達(dá)到這一目的,我們從CoDeveloper工具中選用Altera Nios Platform Support Package,處理相關(guān)的Impulse C源文件。這將產(chǎn)生大約1200行的RTL和相關(guān)的硬件/軟件接口源文件。

接下來(lái),用Altera Quartus工具建立新的項(xiàng)目,生成包括必要外設(shè)的Nios處理器核(用Altera的SOPC Builder)。CoDeveloper輸出生成的硬件和軟件文件給Quartus。使用Altera的框圖工具,我們通過(guò)Avalon片內(nèi)總線(xiàn)將生成的硬件過(guò)程和Nios處理器相連。

整個(gè)系統(tǒng)用Altera Quartus綜合。應(yīng)用的軟件部分(主要由測(cè)試生成器和客戶(hù)功能組成,包括組函數(shù))也導(dǎo)入Quartus項(xiàng)目,用所包含的Nios編譯器編譯。

最后,用Altera工具生成bit文件,通過(guò)提供的并口電纜下載到平臺(tái)上。在這個(gè)平臺(tái)按預(yù)期要求上電和運(yùn)行。

在這個(gè)例子中,顯式流水的兩個(gè)圖像濾波器過(guò)程和由CoDeveloper C自動(dòng)為硬件編譯器生成的流水在每?jī)蓚€(gè)FPGA時(shí)鐘周期獲得最佳的單像素圖像處理速率,相當(dāng)于大約10ms完成整個(gè)512×512圖像的處理速度。

當(dāng)然,在FPGA上任何算法的性能是取決于I/O因素及算法本身。在我們的圖像濾波器測(cè)試方案中,圖像數(shù)據(jù)從Nios上運(yùn)行的測(cè)試生成器通過(guò)Avalon片內(nèi)互連傳送到生成的FPGA硬件上,這樣可以獲得比上述最大像素速率低得多的有效吞吐量。另一個(gè)算法版本中,像素?cái)?shù)據(jù)直接從FPGA硬件接口傳送和讀取,這樣做的結(jié)果會(huì)最接近最佳的結(jié)果。因此考慮帶寬的限制是非常重要的。象CoDeveloper這樣的工具可以更容易和更快地進(jìn)行這方面的評(píng)估和實(shí)驗(yàn)。

附文:Impluse C編程模型

建立軟件和硬件相結(jié)合的設(shè)計(jì)需要對(duì)并行編程技術(shù)有所了解。為了幫助建立高度并行的混合硬件/軟件應(yīng)用,Impulse C庫(kù)包括了設(shè)置和管理多個(gè)獨(dú)立過(guò)程的功能,它可以通過(guò)數(shù)據(jù)流、信號(hào)和可選的共享存儲(chǔ)資源相連接。

Impulse C編程模型(概念上和1980年C.A.R.Hoare描述的通信時(shí)序處理模型類(lèi)似)提供了對(duì)硬件/軟件劃分和同步的系統(tǒng)級(jí)控制,同時(shí)允許用標(biāo)準(zhǔn)C構(gòu)造編寫(xiě)和自動(dòng)優(yōu)化獨(dú)立過(guò)程。

圖a,Impulse C編程模型:通信主要通過(guò)數(shù)據(jù)流(映射為生成硬件中的FIFO),其它需要同步的信號(hào),本地存儲(chǔ)器。

使用Impulse C庫(kù)功能,C語(yǔ)言可用來(lái)描述高度并行的應(yīng)用,具有最小的軟件編程復(fù)雜度,同時(shí)具有用標(biāo)準(zhǔn)C開(kāi)發(fā)環(huán)境下編譯和調(diào)試的能力。例如,使用Impulse C庫(kù)功能,一個(gè)簡(jiǎn)單的圖像濾波器可以用如下的代碼風(fēng)格描述(實(shí)際算法省略)

這設(shè)計(jì)方法的結(jié)果是底層硬件平臺(tái)的實(shí)際情況被抽象,用戶(hù)(他可能是有經(jīng)驗(yàn)的C程序員,但幾乎沒(méi)有硬件設(shè)計(jì)知識(shí))不必學(xué)習(xí)硬件設(shè)計(jì)方法,就可以描述和運(yùn)行混合軟件/硬件應(yīng)用。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論