基于DSP+FPGA的實(shí)時視頻采集系統(tǒng)設(shè)計

0 引言

圖像是自然生物或人造物理的觀測系統(tǒng)對世界的記錄,是以物理為載體,以介質(zhì)來

2010-01-11 10:15:46 833

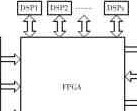

833 DSP+FPGA部分 FPGA + DSP結(jié)構(gòu),DSP采用TMS320C6455,FPGA采用XC5VSX95T-1FF1136T具備CPCI接口,PCI為32bit 33MHzDSP具有千兆網(wǎng)絡(luò)DSP

2014-06-24 14:01:53

本帖最后由 mr.pengyongche 于 2013-4-30 03:09 編輯

DSP+FPGA在高速高精運(yùn)動控制器中的應(yīng)用 摘要:數(shù)字信號處理器具有高效的數(shù)值運(yùn)算能

2012-12-28 11:20:34

DSP+FPGA+AD控制系統(tǒng),FPGA負(fù)責(zé)AD7606的采集,將電機(jī)參數(shù)采集后,傳輸至DSP ,DSP將數(shù)據(jù)進(jìn)行變換后輸出PWM進(jìn)而控制電機(jī)的轉(zhuǎn)速。DSP采用TI公司的TMS320F28335

2016-07-18 16:59:22

DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級,適合于實(shí)時視頻圖像處理,電機(jī)控制,數(shù)據(jù)采集。單DSP核心的系統(tǒng)

2016-09-24 10:41:18

`DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級,適合于實(shí)時視頻圖像處理,電機(jī)控制,數(shù)據(jù)采集。單DSP核心

2016-09-01 15:41:48

在雷達(dá)信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實(shí)時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復(fù)雜算法處理上的優(yōu)勢,DSP+FPGA的實(shí)時信號處理系統(tǒng)的應(yīng)用越來越廣泛

2018-12-04 10:39:29

在雷達(dá)信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實(shí)時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復(fù)雜算法處理上的優(yōu)勢,DSP+FPGA的實(shí)時信號處理系統(tǒng)的應(yīng)用越來越廣泛

2019-06-19 05:00:08

摘要:在雷達(dá)信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實(shí)時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復(fù)雜算法處理上的優(yōu)勢,DSP+FPGA的實(shí)時信號處理系統(tǒng)

2019-06-21 05:00:04

的數(shù)目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實(shí)現(xiàn)。本課程以DSP設(shè)計在FPGA芯片上的開發(fā)為主線,遵照由淺入深的基本步驟和思路進(jìn)行詳細(xì)講解,每一個知識點(diǎn)都給出了基于ISE(HDL語言

2009-07-21 09:22:42

FPGA器件售價不到10美元(在與門陣列產(chǎn)品相當(dāng)?shù)呐繒r)。 性能和功耗 與傳統(tǒng)數(shù)據(jù)處理方法不同,DSP采用了高度流水線化的并行操作。而FPGA結(jié)構(gòu)則可以做得更好,達(dá)到更高的性能。FPGA具有

2011-02-17 11:21:37

兼顧速度及靈活性。高層運(yùn)算的特點(diǎn)是所處理的數(shù)據(jù)量較底層少,但算法結(jié)構(gòu)復(fù)雜,適宜采用運(yùn)算速度高、尋址方式靈活、通信能力強(qiáng)的DSP 芯片來實(shí)現(xiàn)。DSP+FPGA 結(jié)構(gòu)最大的特點(diǎn)是結(jié)構(gòu)靈活,有較強(qiáng)的通用性

2018-12-06 10:05:49

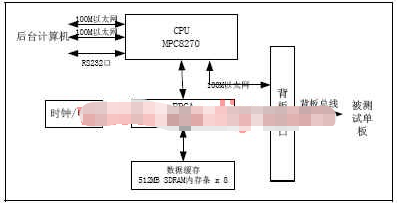

。可以通過在DSP的Linkport總線接口上增加FPGA實(shí)現(xiàn)的適配電路,擴(kuò)展USB 2.0接口,實(shí)現(xiàn)上述應(yīng)用需求。下文將介紹具體的實(shí)現(xiàn)方案。1 系統(tǒng)總體方案系統(tǒng)實(shí)現(xiàn)的總體方案如圖1所示。在本方案中

2019-05-31 05:00:04

反復(fù)編程使用。DSP、FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優(yōu)點(diǎn)。在中小批量通信產(chǎn)品的設(shè)計生產(chǎn)中,用FPGA和DSP實(shí)現(xiàn)HDLC功能是一種值得采用的方法。HDLC的幀

2011-03-17 10:23:56

處理器的數(shù)目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實(shí)現(xiàn)。本課程以DSP設(shè)計在FPGA芯片上的開發(fā)為主線,遵照由淺入深的基本步驟和思路進(jìn)行詳細(xì)講解,每一個知識點(diǎn)都給出了基于ISE(HDL語言

2009-07-21 09:20:11

相位、多抽樣率處理、級聯(lián)、易于存儲等;可用于頻率非常低的信號。項(xiàng)目描述:在借鑒和吸收國內(nèi)外示波器技術(shù)的基礎(chǔ)上,設(shè)計了基于DSP的50MHz的數(shù)字示波器。本系統(tǒng)采用了DSP+FPGA的結(jié)構(gòu),充分利用

2015-09-10 11:15:17

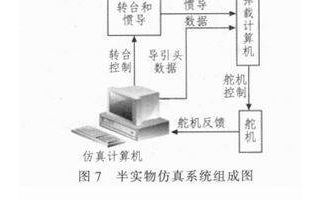

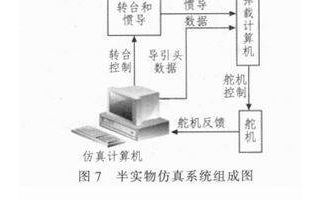

飛控計算機(jī)平臺尤為重要。傳統(tǒng)的單處理器核心飛控計算機(jī)難以在多通道異步數(shù)據(jù)收發(fā)的同時保證數(shù)據(jù)處理速度,難以滿足現(xiàn)代導(dǎo)彈的要求。本文提出了一種基于DSP+FPGA結(jié)構(gòu),對外接口為422的通用數(shù)字飛控計算機(jī)

2019-06-26 07:29:55

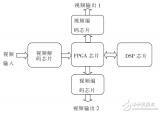

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。實(shí)時視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于用

2019-07-01 07:38:06

,集成度高,可靠性強(qiáng)。綜合比較以上3種方案,在對WCDMA數(shù)字基帶接收機(jī)的設(shè)計中,采用了第三種方案,其結(jié)構(gòu)框圖如圖1所示。

2019-07-05 06:41:27

本帖最后由 mr.pengyongche 于 2013-4-30 03:00 編輯

這是華中科技大學(xué)一篇關(guān)于dsp+fpga直線電機(jī)伺服驅(qū)動的論文。希望對這方面科研的同學(xué)有幫

2013-03-22 17:21:46

SEED-HPS6678(HPS6678)是北京艾睿合眾科技有限公司新推出的新一代高端DSP+FPGA應(yīng)用方案。DSP采用TI公司首顆最高主頻為10GHz的8核浮點(diǎn)DSP芯片TMS320C6678

2019-09-24 08:29:12

分享一種TD-SCDMA系統(tǒng)基帶發(fā)送方案

2021-06-01 06:52:04

和軟件設(shè)計層次上逐漸被克服。FPGA硬件結(jié)構(gòu)正在實(shí)現(xiàn)增強(qiáng)的DSP塊。并具有更多的功能和更強(qiáng)的性能。系統(tǒng)級設(shè)計軟件正在簡化從塊級到硬件描述語言(HDL),級的轉(zhuǎn)換。一些系統(tǒng)工具中集成了流行的DSP算法開發(fā)工具(例如MATLAB),大大簡化了FPGA中實(shí)現(xiàn)信號處理算法的過程。

2021-12-15 06:30:00

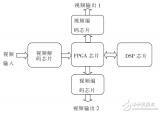

有限的不足,而且提高了監(jiān)控資源的利用率,降低了監(jiān)控成本。 1 系統(tǒng)硬件結(jié)構(gòu) 采用DSP+FPGA的硬件結(jié)構(gòu)方案,利用DSP和FPGA控制MAX4312選通所需要的視頻通道,從而達(dá)到在多路視頻通道間進(jìn)行切換的目的。系統(tǒng)結(jié)構(gòu)框圖如

2012-12-12 17:00:21

會受一定的影響。?本文所提出的基于DSP+FPGA的控制系統(tǒng)方案,利用FPGA的容量大、可編程實(shí)現(xiàn)很多功能,結(jié)合DSP具有高速的信息處理能力的特點(diǎn),使得本控制系統(tǒng)非常簡潔,結(jié)構(gòu)靈活,通用性強(qiáng),系統(tǒng)也易于維護(hù)和擴(kuò)展。該方案基于軟件無線電的思想,是采用通用平臺的設(shè)計。?

2019-07-29 06:08:47

報文和GOOSE報文的發(fā)送間隔都有嚴(yán)格的時間間隔要求,因此本設(shè)計中時序控制采用FPGA實(shí)現(xiàn),相對與DSP系統(tǒng),FPGA系統(tǒng)在時序控制上能實(shí)現(xiàn)更為精準(zhǔn)的時序,本方案中FPGA芯片主要作為以太網(wǎng)總線控制器

2018-09-06 10:21:51

ASIC不夠靈活的缺點(diǎn)。與其他中小規(guī)模集成電路相比,其優(yōu)點(diǎn)主要在于它有很強(qiáng)的靈活性,即其內(nèi)部的具體邏輯功能可以根據(jù)需要配置,對電路的修改和維護(hù)很方便。DSP+FPGA結(jié)構(gòu)最大的特點(diǎn)是結(jié)構(gòu)靈活,有較強(qiáng)

2019-09-19 08:21:16

的重點(diǎn)是以DSP+FPGA為核心的視頻處理模塊的設(shè)計與實(shí)現(xiàn),可以完成多路視頻的切換選擇輸出控制和視頻縮放顯示的功能,同時具備通信控制等功能。

2019-06-20 06:34:25

FPGA一般用來控制整個系統(tǒng)的時序,本設(shè)計采用集成微處理器的FPGA,同時完成信號模擬和時序控制的功能,改變了以往信號處理DSP+FPGA中FPGA作為協(xié)處理器的模式[1-3]。整個設(shè)計僅需要具有嵌入

2019-07-15 06:48:33

基于DSP28335_開發(fā)板實(shí)現(xiàn)SD_FAT32的電路方案設(shè)計源碼

2023-09-20 07:52:07

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。 實(shí)時視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-28 08:10:26

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。 實(shí)時視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-19 06:12:05

隨著現(xiàn)代電子信息技術(shù)的發(fā)展,人機(jī)交互、圖形圖像數(shù)據(jù)的輸出顯示在系統(tǒng)設(shè)計中越來越重要,一方面要求各種參數(shù)的輸入,另一方面要求將數(shù)據(jù)結(jié)構(gòu)顯示出來。文中設(shè)計的基于DSP和FPGA的系統(tǒng)結(jié)構(gòu),實(shí)現(xiàn)了人機(jī)交互

2019-07-03 08:08:33

它們在高速和實(shí)時系統(tǒng)中的應(yīng)用。隨著深亞微米半導(dǎo)體制造工藝的不斷創(chuàng)新,百萬門可編程器件的不斷推出,為DSP提供了第3種有效的解決方案,即利用FPGA實(shí)現(xiàn)DSP運(yùn)算硬件化。它能夠在集成度、速度和系統(tǒng)功能

2019-08-02 06:03:48

,但是需要占用較大的存儲空間。3. 基于FPGA 的非線性校正方法的實(shí)現(xiàn)方案有兩種對OFDM基帶信號實(shí)現(xiàn)非線性校正的方案。一種是基于FPGA,一種是基于DSP。基于FPGA方案的優(yōu)點(diǎn)在于集成度高,而

2018-07-30 18:09:06

信號,調(diào)制無線信號以便實(shí)現(xiàn)同通信網(wǎng)絡(luò)系統(tǒng)前端基站的無線通信。文章設(shè)計了一種基于先進(jìn)微處理器(ARM)、數(shù)字信號處理(DSP)和現(xiàn)場可編程門陣列(FPGA)體系結(jié)構(gòu)的3G移動終端基帶信號處理器。這種

2019-07-03 06:18:48

本文介紹基于TMS320VC5509A DSP的JPEG視頻壓縮系統(tǒng)的設(shè)計和實(shí)現(xiàn)方案,該系統(tǒng)硬件設(shè)計采用DSP+FPGA的方案,充分發(fā)揮了各自優(yōu)勢;而軟件設(shè)計針對C55x的結(jié)構(gòu)進(jìn)行程序結(jié)構(gòu)和算法優(yōu)化,經(jīng)過驗(yàn)證達(dá)到較好的實(shí)時效果。

2021-06-02 06:25:48

雖然并不如預(yù)想中明朗,但中國3G的蓄勢待發(fā)和WiMax的推進(jìn)以及并不太遙遠(yuǎn)的4G、LTE等,將促進(jìn)宏基站和家用基站市場的起飛。在傳統(tǒng)的ASIC及DSP+FPGA基站解決方案外,多核DSP浮出水面,基站解決方案開始承接新一輪的吐故納新。

2019-07-18 07:54:22

如何采用現(xiàn)場可編輯門陣列FPGA來實(shí)現(xiàn)對直流電機(jī)的控制?

2021-10-19 09:08:30

介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進(jìn)行直接數(shù)字頻率合成的VHDL源程序。

2021-04-30 06:29:00

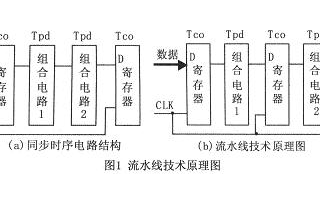

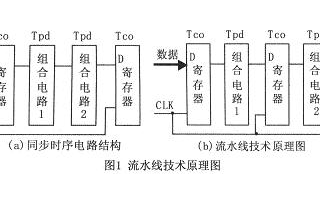

本文首先介紹了FIR濾波器和脈動陣列的原理,然后設(shè)計了脈動陣列結(jié)構(gòu)的FIR濾波器,畫出電路的結(jié)構(gòu)框圖,并進(jìn)行了時序分析,最后在FPGA上進(jìn)行驗(yàn)證。結(jié)果表明,脈動陣列的模塊化和高度流水線的結(jié)構(gòu)使FIR

2021-04-20 07:23:59

、成本上的優(yōu)勢是巨大的。 除了上述兩種方案,還有DSP+FPGA方案,以及選擇內(nèi)部嵌入DSP模塊的FPGA實(shí)現(xiàn)系統(tǒng)的方案。

2019-06-19 08:02:03

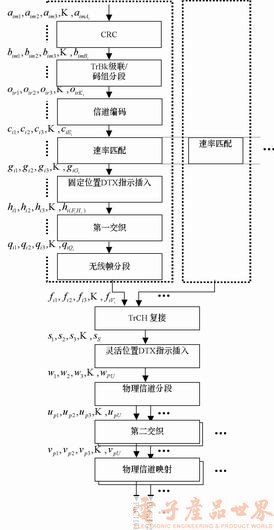

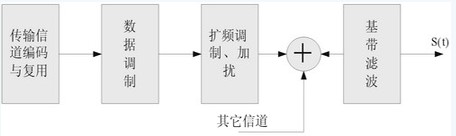

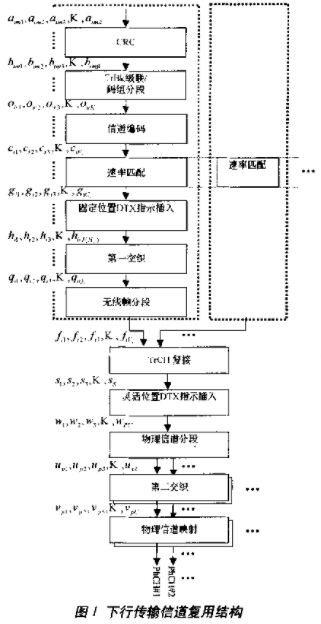

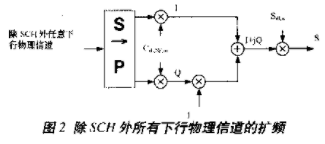

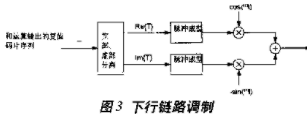

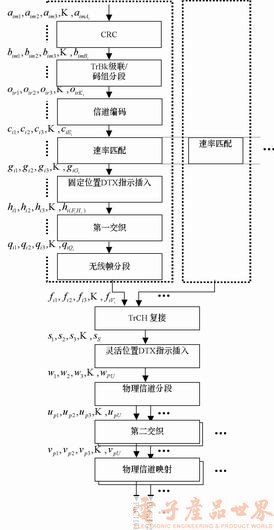

本文首先介紹WCDMA系統(tǒng)的無線信道的基帶發(fā)送方案,說明其對多媒體業(yè)務(wù)的支持以及實(shí)現(xiàn)的復(fù)雜性。然后,從硬件實(shí)現(xiàn)角度,進(jìn)行了DSP和FPGA的性能比較,提出DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案,并以基站分系統(tǒng)(BTS)的發(fā)送單元為例,具體給出了該實(shí)現(xiàn)方案在下行無線信道基帶發(fā)送單元中的應(yīng)用。

2021-05-06 07:40:39

,市場上的麥克風(fēng)陣列方案不斷增加。在組合結(jié)構(gòu)上以線形、環(huán)形為主。在麥克風(fēng)數(shù)量上,一般消費(fèi)級別的有2、4、5、6、8等幾種形式。訊飛也推出二麥線性陣列、四麥線性陣列和六麥環(huán)形陣列,以及MORFEI麥克風(fēng)

2018-05-17 15:36:07

請教電力電子方向里dsp+FPGA架構(gòu)的案例

2018-12-10 18:32:58

這部分完成。其中每一次讀寫操作都需要嚴(yán)格按照 DS18B20的讀寫時隙進(jìn)行。該模塊復(fù)雜程度高和占用資源多,是整個 FPGA中的重要模塊。本方案一共有七路溫度采集模塊,它們的并行結(jié)構(gòu)使得系統(tǒng)可以方便地實(shí)現(xiàn)

2020-08-19 09:29:48

具有系統(tǒng)級性能的FPGA在半導(dǎo)體工藝的線寬達(dá)到深亞微米后更進(jìn)一步按信號處理的要求改進(jìn)器件結(jié)構(gòu)和性能,不僅可實(shí)現(xiàn)VLSI DSP,且具有系統(tǒng)內(nèi)可再編程的特性,可用流水和并行處

2009-05-09 12:57:35 16

16 介紹了基于新型高性能DSP芯片TMS320F2812和現(xiàn)場可編程門陣列ACEXEPlK208-3FPGA實(shí)現(xiàn)的斷路器同步關(guān)合控制平臺的設(shè)計,控制單元采用嵌人式實(shí)時多任務(wù)操作系統(tǒng)pC/OS-II作為系統(tǒng)軟件平臺,

2009-07-07 16:17:13 25

25 本文介紹了DSP 和FPGA 在數(shù)字電子設(shè)計中的優(yōu)勢,并結(jié)合雷達(dá)模擬系統(tǒng)的硬件設(shè)計實(shí)例,重點(diǎn)闡述了相應(yīng)的硬件與軟件實(shí)現(xiàn)方法。關(guān)鍵詞:DSP FPGA 數(shù)字電路設(shè)計雷達(dá)模擬系統(tǒng)

2009-08-25 14:33:01 15

15 簡要分析了DSP+FPGA系統(tǒng)的特點(diǎn)和優(yōu)越性,并且結(jié)合一個實(shí)時信號處理板的開發(fā),提出在此類系統(tǒng)中,FPGA設(shè)計的幾個關(guān)鍵問題,并且給出了詳實(shí)的分析和解決方案。

2009-09-02 17:44:44 24

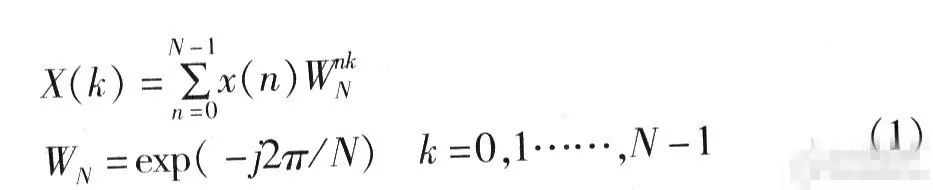

24 本文討論了一種可在FPGA 上實(shí)現(xiàn)的FFT 結(jié)構(gòu)。該結(jié)構(gòu)采用基于流水線結(jié)構(gòu)和快速并行乘法器的蝶形處理器。乘法器采用改進(jìn)的Booth 算法,簡化了部分積符號擴(kuò)展,使用Wallace 樹結(jié)構(gòu)和4-2

2009-09-11 15:46:40 16

16 主要介紹基于現(xiàn)場可編程門陣列(FPGA)的微波接力通信中FFT 模塊的設(shè)計與實(shí)現(xiàn)方案。提出一種全并行流水結(jié)構(gòu),采用新一代大容量的高速Stratix 系列FPGA 可以在N 個系統(tǒng)時鐘之內(nèi)

2009-11-24 12:13:19 19

19 簡要分析了DSP+FPGA 系統(tǒng)的特點(diǎn)和優(yōu)越性,結(jié)合導(dǎo)引頭信號處理板的開發(fā),提出了在此系統(tǒng)中,FPGA 設(shè)計的幾個關(guān)鍵技術(shù),并且給出了詳實(shí)的分析和解決方案。

2009-12-23 14:53:54 20

20 為了在梳棉機(jī)上實(shí)現(xiàn)在線檢測監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測裝置,取代傳統(tǒng)的PC-Base檢測模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計和控制

2010-02-24 14:06:05 18

18 對于嵌入式折反射全景視頻處理系統(tǒng),由于計算量大,一般采用多處理器協(xié)同的結(jié)構(gòu),但在該結(jié)構(gòu)下多個處理器之間需要進(jìn)行高速的數(shù)據(jù)通信。該文提出一種基于DSP+FPGA 架構(gòu)的雙核

2010-03-06 11:03:46 10

10 FPGA實(shí)現(xiàn)DSP應(yīng)用

摘要:具有系統(tǒng)級性能的FPGA在半導(dǎo)體工藝的線寬達(dá)到深亞微米后更進(jìn)一步按信號處理的要求改進(jìn)器件結(jié)構(gòu)和性能,不僅可實(shí)現(xiàn)VLSI DSP,且具有系統(tǒng)

2010-04-01 15:39:54 14

14 為了在梳棉機(jī)上實(shí)現(xiàn)在線檢測監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測裝置,取代傳統(tǒng)的PC-Base檢測模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計和控制

2010-07-17 17:25:09 11

11 簡要分析了DSP+FPGA系統(tǒng)的特點(diǎn)和優(yōu)越性,結(jié)合導(dǎo)引頭信號處理板的開發(fā),提出了在此系統(tǒng)中,FPGA設(shè)計的幾個關(guān)鍵技術(shù),并且給出了詳實(shí)的分析和解決方案。

2010-07-21 17:28:04 18

18 摘? 要: 本文在分析WCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,結(jié)合DSP和FPGA性能的比較,提出了一種在性能、靈活性和性價比上都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 引言 隨

2006-03-11 13:29:42 1016

1016

摘要: 提出了一種采用現(xiàn)場可編程門陣列(FPGA)實(shí)現(xiàn)基帶信號成形的FIR數(shù)字濾波器硬件電路的方案。該方案基于分布式算法的思想,利用FPGA豐富的查找表資源,從

2009-06-20 14:07:44 1439

1439

基于DSP+FPGA的實(shí)時視頻采集系統(tǒng)設(shè)計

0 引言

圖像是自然生物或人造物理的觀測系統(tǒng)對世界的記錄,是以物理為載體,以介質(zhì)來記錄信息的

2009-12-16 10:20:55 767

767

一種基于DSP+FPGA的控制系統(tǒng)方案設(shè)計

一、前言 ?

本文提到的控制系統(tǒng)控制通信設(shè)備的正常工作,是整個通信設(shè)備的重要組成部分。該控制系統(tǒng)要實(shí)現(xiàn)的功能

2009-12-22 17:44:41 1134

1134

目前的衛(wèi)星遙感圖像壓縮系統(tǒng)硬件方案大多基于高性能可編程邏輯器件FPGA[2-4]。但這種方案整系統(tǒng)成本居高不下,且FPGA存在單粒子翻轉(zhuǎn)效應(yīng)。因此,筆者提出一種多DSP+FPGA的

2010-11-27 10:35:05 1909

1909

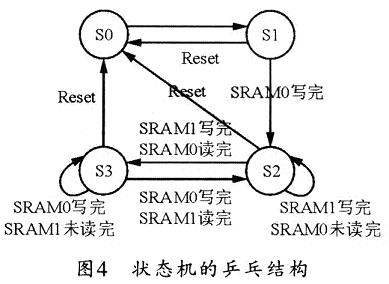

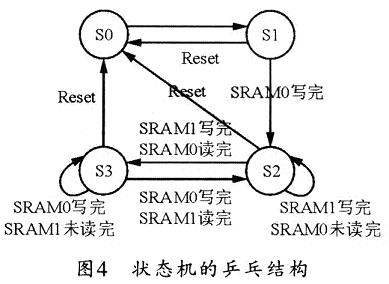

摘要:為了實(shí)現(xiàn)高速HDLC通訊協(xié)議,設(shè)計了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機(jī);其中DSP用于實(shí)現(xiàn)數(shù)據(jù)控制,FPGA用于實(shí)現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 摘要:根據(jù)衛(wèi)星數(shù)傳系統(tǒng)的要求,考慮FPGA的單拉子效應(yīng),提出一種多。印DSP+FPGA的衛(wèi)星數(shù)據(jù)壓縮機(jī)的硬件結(jié)構(gòu)。介紹了CCD相機(jī)與教據(jù)壓縮機(jī)之間的LVDS接口、數(shù)據(jù)壓縮機(jī)與綜合處理器之間的遙控遙測接口、硬件內(nèi)部DSP與FPGA之間的串行EDMA方式通信接口的實(shí)現(xiàn)方法,

2011-02-27 23:08:56 61

61 【摘要】本文論述了FPGA在DSP應(yīng)用上的優(yōu)缺點(diǎn),比較了FPGA芯片和DSP芯片之間的差別,介紹了解決隔閡的方案--Xtreme DSP軟件包和平臺級的Virtex Ⅱ芯片。最后,對Xtreme和VirtexⅡ芯片的特點(diǎn)進(jìn)行了詳細(xì)說明。 關(guān)鍵詞:數(shù)字信號處理;可編程門陣列;芯片

2011-02-28 13:09:41 61

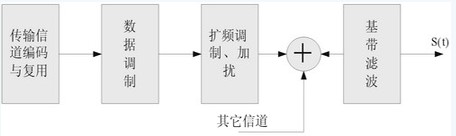

61 摘要:本文在分析TD-SCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,提出了一種在性能、靈活性和性價比方面都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 關(guān)鍵詞:TD-SCDMA;基帶處理;DSP;FPGA

2011-03-02 01:38:41 60

60 文章介紹了一種基于DSP爭FPGA結(jié)構(gòu)的高精度測井?dāng)?shù)據(jù)采集系統(tǒng)的設(shè)計方法,包括信號調(diào)理、數(shù)據(jù)采集、數(shù)據(jù)處理等。整個系統(tǒng)使用16位高精度A/D轉(zhuǎn)換芯片AD974。數(shù)字電路部分采用Xilinx公司

2011-09-08 17:46:55 71

71 針對目前國內(nèi)外大多數(shù)紅外圖像自動跟蹤系統(tǒng)采用DSP+FPGA 結(jié)構(gòu),系統(tǒng)存在設(shè)計電路復(fù)雜、成本高、實(shí)時性較差等缺點(diǎn),開發(fā)出在單片現(xiàn)場可編程門陣列(FPGA)中實(shí)現(xiàn)以NiosⅡ軟核處理器

2011-09-13 17:29:54 77

77 針對兩軸電視經(jīng)緯儀動基座跟蹤目標(biāo)時,視軸無法隔離載體擾動造成圖像旋轉(zhuǎn)現(xiàn)象,提出一種基于數(shù)學(xué)平臺的電子消旋方法,采用捷聯(lián)式慣導(dǎo)+DSP+FPGA的硬件系統(tǒng)通過反向旋轉(zhuǎn)和雙線性插

2011-09-14 16:27:23 38

38 本文介紹了一種應(yīng)用于數(shù)字通信領(lǐng)域的語音基帶處理系統(tǒng)。設(shè)計的目的是把待傳輸?shù)哪M語音信號轉(zhuǎn)換為數(shù)字基帶信號,使用固定的頻率在信道上傳輸。根據(jù)系統(tǒng)的功能,設(shè)計中主要采

2011-10-14 17:37:04 35

35 在雷達(dá)信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實(shí)時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復(fù)雜算法處理上的優(yōu)勢,DSP+FPGA的實(shí)時信號處理系統(tǒng)

2012-07-05 15:01:40 8211

8211

一種基于FPGA的ZigBee物理層發(fā)射機(jī)的數(shù)字基帶實(shí)現(xiàn)方案_陳迪平

2017-03-14 16:54:58 6

6 針對信號處理數(shù)據(jù)量大、實(shí)時性要求高的特點(diǎn),從實(shí)際應(yīng)用出發(fā),設(shè)計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務(wù)需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 3061

3061

本文主要介紹了一種基于DSP+FPGA的實(shí)時圖像去霧增強(qiáng)系統(tǒng)設(shè)計,FPGA通常作為一種調(diào)度使用,圖像處理算法實(shí)現(xiàn)主要靠高速處理信號處理芯片DSP完成,在跟蹤等領(lǐng)域圖像數(shù)據(jù)只需單向進(jìn)入DSP,處理后輸出相應(yīng)參數(shù)即可,在實(shí)時視頻圖像處理中大量圖像數(shù)據(jù)只需通過EMIF輸入,且輸出數(shù)據(jù)量較小可以實(shí)時完成。

2017-12-25 10:24:21 4379

4379

本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計與實(shí)現(xiàn),DSP-BF561作為主處理器,負(fù)責(zé)整個算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實(shí)現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預(yù)處理中大量的累乘加運(yùn)算。實(shí)驗(yàn)證明系統(tǒng)達(dá)到了實(shí)時性要求。

2017-12-25 10:39:47 5649

5649

控計算機(jī)平臺尤為重要。傳統(tǒng)的單處理器核心飛控計算機(jī)難以在多通道異步數(shù)據(jù)收發(fā)的同時保證數(shù)據(jù)處理速度,難以滿足現(xiàn)代導(dǎo)彈的要求。本文提出了一種基于DSP+FPGA結(jié)構(gòu),對外接口為422的通用數(shù)字飛控計算機(jī)平臺

2020-01-29 17:11:00 3012

3012

,所需的存儲量、運(yùn)算量以及處理延時差異很大。因此,采用何種硬件結(jié)構(gòu)才能有效地處理各種業(yè)務(wù)是本文所要探討的問題。

2020-01-16 09:16:00 2949

2949

與FPGA結(jié)合在一起,組成DSP+FPGA架構(gòu),實(shí)現(xiàn)了需求獨(dú)特、靈活、功能強(qiáng)大的DSP+FPGA高速數(shù)據(jù)采集處理系統(tǒng)。

2020-02-12 13:42:30 4542

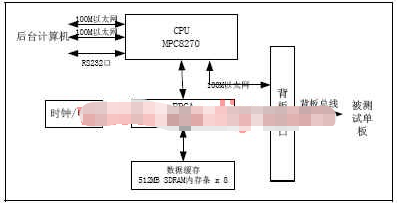

4542 在基站的模擬測試系統(tǒng)中,終端控制子系統(tǒng)負(fù)責(zé)生成上行測試數(shù)據(jù)并將其發(fā)送到被測基帶板,測試基帶板上行接收的功能及性能;同時根據(jù)后臺控制采集下行發(fā)射的基帶數(shù)據(jù)并送后臺進(jìn)行分析,測試其發(fā)射功能。而FPGA部分屬于終端控制子系統(tǒng)的前臺部分,負(fù)責(zé)IQ數(shù)據(jù)的發(fā)送及采集,基帶測試板的功能主要在這里面實(shí)現(xiàn)。

2020-08-07 17:53:52 1482

1482

它們在高速和實(shí)時系統(tǒng)中的應(yīng)用。隨著深亞微米半導(dǎo)體制造工藝的不斷創(chuàng)新,百萬門可編程器件的不斷推出,為DSP提供了第3種有效的解決方案,即利用FPGA實(shí)現(xiàn)DSP運(yùn)算硬件化。它能夠在集成度、速度和系統(tǒng)功能方面滿足DSP應(yīng)用的需要。

2020-08-10 11:22:34 1692

1692

本電路方案為基于DSP2407 開發(fā)板實(shí)現(xiàn)cap的電路方案設(shè)計,內(nèi)附有原理圖,PCB以及源碼文件,適合剛?cè)腴Tdsp的小伙伴學(xué)習(xí)使用。有需要參考的可以下載來看看。

2020-12-11 08:00:00 12

12 針對高速實(shí)時信號處理的要求,介紹了用現(xiàn)場可編程邏輯陣列(FPGA)實(shí)現(xiàn)的一種流水線結(jié)構(gòu)的FFT處理器方案。該FFT處理器能夠?qū)π盘栠M(jìn)行實(shí)時頻譜分析,最高工作頻率達(dá)到75 MHz。通過對采樣數(shù)據(jù)進(jìn)行加

2021-01-25 14:51:00 12

12 為消除因探測器姿態(tài)變化造成的圖像旋轉(zhuǎn),保持觀測圖像的穩(wěn)定狀態(tài),采用可編程邏輯門陣列(FPGA)和數(shù)字信號處理器(DSp)構(gòu)建數(shù)字硬件平臺。給出了實(shí)時消像旋的完整硬件結(jié)構(gòu)與相應(yīng)算法。設(shè)計采用

2021-02-04 16:46:00 10

10 基于DSP28335實(shí)現(xiàn)SD_FAT32的電路方案設(shè)計源碼。

2021-03-25 14:48:18 33

33 目前,硬件實(shí)現(xiàn)FFT算法的方案主要有:通用數(shù)字信號處理器(DSP)、FFT專用器件和現(xiàn)場可編程門陣列(FPGA)。DSP具有純軟件實(shí)現(xiàn)的靈活性,適用于流程復(fù)雜的算法,如通信系統(tǒng)中信道的編譯

2023-05-11 15:31:41 3541

3541

電子發(fā)燒友網(wǎng)站提供《基于DSP的車載語音識別系統(tǒng)方案設(shè)計.pdf》資料免費(fèi)下載

2023-11-08 09:14:38 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評論