我們常用的電腦看到CPU一般有I3、I5、I7,那么什么是酷睿i7處理器,i7處理器怎么樣?酷睿i7是一款45nm的四核處理器,處理器擁有8MB三級緩存,支持三通道 DDR3內存。處理器采用LGA 1366針

2012-09-14 14:30:59 32573

32573 QAT相關的名詞組織關系是什么?處理器和PCH設備之間的通訊流程是怎樣的?服務實例與硬件是如何交互的?

2021-07-23 08:12:11

處理器中斷處理的過程是怎樣的?處理器在讀內存的過程中,CPU核、cache、MMU如何協同工作?

2021-10-18 08:57:48

矢量中斷控制器(NVIC)與處理器核心緊密集成,以實現低延遲中斷處理。

?多個高性能總線接口。

?低成本調試解決方案,具有以下可選功能:

--實現斷點和代碼修補程序。

--實施監視點、跟蹤和系統分析

2023-08-08 07:18:05

。

·專用低延遲AHB-Lite外設(AHBP)接口。

·AHB-提供對TCM的DMA訪問的Lite從機(AHBS)接口。

處理器有一個可選的內存保護單元(MPU),可以配置為保護內存區域。

用于錯誤檢測

2023-08-17 07:55:23

,并且提供了可選的硬件加速器一致性端口(ACP),以減少與其他主機共享存儲器區域時的軟件高速緩存維護操作。

中斷延遲通過中斷和重新啟動加載-存儲多條指令以及使用集成中斷控制器來保持低。

Cortex-R7 MPCore處理器為低延遲和確定性提供了兩種專門的內存解決方案

2023-08-18 06:34:29

該處理器包括一個內核、一個嵌套的矢量化中斷控制器(NVIC)、高性能總線接口和其他功能。

該處理器包含以下功能:

·處理器核心。

·嵌套矢量化中斷控制器(NVIC)與處理器內核緊密集成,實現低延遲

2023-08-18 06:09:49

。ARM Cortex系列處理器ARM公司在經典處理器ARM11以后的產品改用Cortex命名,并分成A、R和M三類,旨在為各種不同的市場提供服務。??1、Cortex-A:面向尖端的基于虛擬內存

2021-05-12 06:30:00

在使用ARM內核單片機的時候,經常搞不清楚處理器與內核架構之間的對應關系,于是自己畫了一個思維導圖,方便觀看。其中相關的命名規則如下指令集命名規則ARM 指令集架構命名規則:| ARMv | n

2021-07-16 06:02:24

ARM處理器都是RISC結構,單周期操作,指令流水線,使用加載或存儲指令訪問內存。ARM7采用馮-諾依曼結構,3級流水線;ARM9采用哈佛結構,5級流水線;Cortex-A15采用13級流水線

2021-12-21 07:16:24

ARM處理器模式和ARM處理器狀態有何區別?

2022-11-01 15:15:13

,或意外操作,如無效輸入數據或操作員錯誤。

?內存損壞,雜散輻射和其他影響可能導致存儲的數據在RAM中被破壞。

ARMv8?M處理器的功能可以使軟件管理甚至糾正一些錯誤條件,并提醒設備的用戶注意該事

2023-08-02 06:28:02

的所有強制功能,以及預取推測保護、斷電調試、可靠性、可用性和可維護性(RAS)擴展以及性能監視器擴展。

Cortex?-R82處理器面向需要最小化延遲的移動調制解調器和存儲控制器應用。

Cortex

2023-08-17 07:45:14

高速緩存維護操作。

中斷延遲通過中斷和重新啟動加載存儲多條指令以及使用集成中斷控制器來保持較低的延遲。

Cortex-R8處理器為低延遲和確定性提供了兩種專門的內存解決方案:

·緊耦合存儲器(TCM

2023-08-18 08:28:22

可以將其用于緊耦合的存儲器(TCM)。二級緩存的大小取決于處理器的版本,各版本對應的大小如下:256 KB (V5a)768 KB (V5h)128 KB (V5l) 二級內存被分區為緩存或緊耦合

2018-09-20 16:50:09

RISC-V和開源處理器之間是什么關系?

2023-03-09 10:06:52

RK3399處理器與AR9201處理器有哪些不同之處呢?hi3559A處理器與RV1126處理器有哪些不同之處呢?

2022-02-21 07:29:27

用于SHARC處理器的ADZS-21489-EZLITE,ADSP-2148x EZ-KIT Lite評估系統。 SHARC處理器基于32位超級哈佛架構,包括一個獨特的內存架構,由兩個大型片上雙端口

2020-03-16 10:19:26

應用處理器與MCU“跨界”處理器—從性能差距到新解決方案領域降低成本—去除片內閃存集高性能、低延遲、高能效和安全性于一體相關行業和應用 i.MX RT跨界處理器

2021-02-19 06:06:39

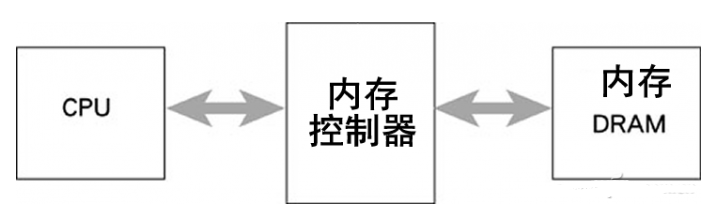

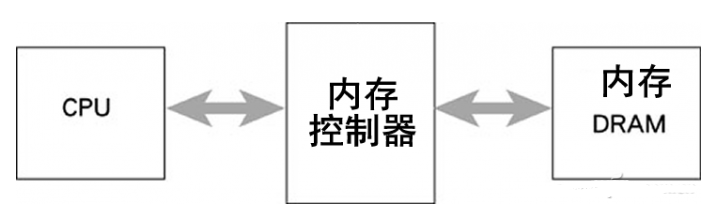

所花的總時間。在處理器上,我們也可以說讀寫的延遲是指令發出,經過緩存,總線,內存控制器,內存顆粒,然后原路返回所花費的時間。但是,更多的時候,我們說的訪存延遲是大量讀寫指令被執行后,統計出來的平均訪問時間

2017-06-08 10:13:08

為什么我的處理器漏電?

2021-03-02 08:19:38

包括 幾種內存管理單元的變種,包括簡單的內存保護到復雜的頁面層次。ARM 微處理器系列包括 ARM7 系列、ARM9 系列、ARM9E 系列、ARM10E 系列、 SecurCode 系列

2019-09-24 17:47:38

總線(元件級總線)微型計算機:由CPU、內存儲器、輸入輸出接口電路組成!以及內總線(系統總線)微型計算機系統:以微型計算機為主體,配上系統軟件,應用軟件,外存儲器,輸入輸出設備,電源,面板和機架!以及外總線(通信總線)微型處理器的典型結構如下圖所示其中...

2021-07-22 06:48:44

任何人都可以使用處理器專家共享 led 閃爍的定時器中斷延遲程序嗎

2023-03-30 07:23:31

我在PIC32系列參考手冊Sec 3中讀到:內存段的映射取決于CPU錯誤級別(由CPU狀態寄存器中的ERL位設置)。在復位、軟復位或NMI上,CPU設置錯誤級別(Erl=1)。在這種模式下,處理器

2020-05-15 14:33:57

i.MX RT跨界處理器基于Adesto EcoXIP進行內存擴展

2022-12-12 07:29:32

你好,目前,我cyblle_22001型控制器ARM M0處理器的工作。我想有多少延遲所產生的處理每一個NOP指令。任何人可以告訴我提前感謝 以上來自于百度翻譯 以下為原文Hi

2018-09-26 11:04:16

如何滿足傳感網節點低功耗和高處理能力間的平衡關系?基于OMAP的低功耗節點處理器該如何去設計?

2021-05-20 06:50:19

存儲器的延遲都是一樣的。這種體系結構的處理器有時候也會被叫做對稱多處理器(Symmetric Multi-Processor,簡稱SMP)。這里的“對稱”,是說所有的處理器沒有主次或從屬關系。所有處理器

2022-06-07 16:46:44

的啟動過程。在分析多核處理器啟動之前,我們先來看看一個單核的計算機系統是如何啟動的。假設大家對內存管理,TLB,緩存(Cache),DDR,PCIe這些有一些基礎知識。當我們按下電源開關以后,系統

2022-06-07 16:41:29

多內核是指在一枚處理器中集成兩個或多個完整的計算引擎(內核),多核處理器是單枚芯片(也稱為“硅核”),能夠直接插入單一的處理器插槽中,但操作系統會利用所有相關的資源,將它的每個執行內核作為分立的邏輯

2019-06-20 06:47:01

在存儲在由指針尋址的內存中的巨大稀疏矩陣上運行因子分解。有沒有辦法給PL中創建的RTL提供相同的內存訪問權限,或者我必須將整個矩陣存儲在本地RAM中,然后運行計算。因為后者會占用大量矩陣的大量空間。 RTL設計如何直接訪問處理器內存。我可以將軟件代碼中使用的相同指針傳遞給硬件邏輯嗎?

2020-04-28 10:26:26

內存延遲對音頻處理器的性能有什么影響?如何使音頻處理以最效的方式實現?

2021-06-02 06:36:53

嗨,我想通過pcie鏈接訪問外部處理器的內存。 CDMA如何知道外部處理器的內存?如何在cdma中尋址外部處理器內存?我試過訪問內存并得到CDMA解碼錯誤?謝謝

2020-04-22 10:28:03

微處理器的結構是由哪些部分組成的?微處理器的代碼是如何執行的呢?

2022-02-28 09:25:10

的基于虛擬內存的操作系統和用戶應用 2、Cortex-R:針對實時系統 3、Cortex-M:微控制器ARM Cortex系列處理器——Cortex-AARM Cortex-A 系列是一系列用于復雜

2018-09-13 10:01:22

有誰知道是否有辦法在54832B上升級bios以支持更多內存和更高速處理器? Scope擁有摩托羅拉VP22主板,1GHz處理器和512MByte內存。謝謝' 以上來自于谷歌翻譯 以下為原文

2019-05-29 10:58:16

我目前正在評估 iMXRT1062 處理器,現在正在尋找具有接近相同 I/O 和內存特性但還支持 MMU 的處理器。也許有人可以就此提出建議。

2023-03-27 07:57:08

的修改方面缺乏靈活性。本文介紹一種嶄新的基于Matlab與QuartusII的DSP處理器的設計軟件DSP Builder,詳細介紹了其設計流程與優點,并以DDS直接數字合成器的實現為例說明用該軟件來設計DSP處理器的方法以及與Matlab、QuartusÊ之間的關系。

2011-03-03 10:05:43

的啟動過程。在分析多核處理器啟動之前,我們先來看看一個單核的計算機系統是如何啟動的。假設大家對內存管理,TLB,緩存(Cache),DDR,PCIe這些有一些基礎知識。當我們按下電源開關以后,系統

2022-07-19 15:00:47

Cortex-A系列處理器采用weakly-ordered內存模型。除此之外,在這個模型中可以將特定的內存區域標記為Strongly-ordered(即對指令執行的順序有嚴格的要求,保證指令按順序

2022-07-26 16:04:03

請問RISC處理器和ARM7處理器的區別在哪?求大神解答

2022-06-30 17:51:06

請問一下ARM處理器與架構對應的關系是什么?

2021-11-04 07:51:15

)、精簡的兩線和單線調試接口、“WFE”指令、物理內存保護(PMP)等特色功能,詳細說明可參考青稞微處理器手冊。

特色功能

1.硬件壓棧(HPE)

稞處理器開啟硬件壓棧后,當發生中斷,硬件自動將

2023-10-11 10:42:49

什么是處理器緩存 緩存是指可以進行高速數據交換的存儲器,它先于內存與CPU交換數據,因此速度很快

2009-12-17 16:03:57 743

743 什么是移動處理器

要了解何謂移動處理器之前,我們不得不弄明白什么是處理器,處理器英文全名為Central Processing Unit,即中央處理器。是電腦中

2010-01-23 11:06:24 2026

2026 什么是處理器緩存處理器緩存:

Cache(高速緩沖存儲器)是位于CPU與主內存間的一種容量較小但速度很高的存儲器。由于CPU的速度遠

2010-02-04 12:02:26 1093

1093 信號處理器(DSP),信號處理器(DSP)是什么意思

DSP是(digital signal processor)的簡稱,是一種專門用來實現信號處理算法的微處理器芯片

2010-03-26 14:53:54 16529

16529

或許您已經發現,內存模塊在主機體上的配置對系統性能表現有直接的影響。由于區域內存必須儲存中央處理器所需的所有數據,內存以及中央處理器間數據

2010-09-15 17:27:56 955

955 現代的處理器(SoC)或DSP都內建有內存控制器,它是外部SDRAM、FLASH、EEPROM、SRAM……等內存的控制接口。但不同處理器內部的內存控制方式都不盡相同

2011-04-21 11:42:01 1374

1374 一種基于隨機指令延遲的抗旁路攻擊處理器結構_李紅

2017-01-07 18:56:13 0

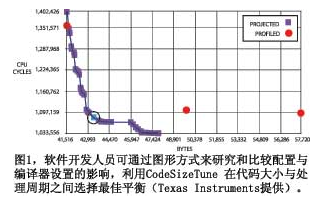

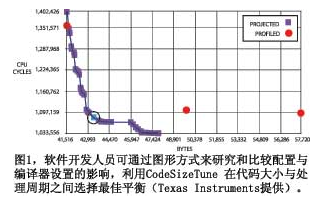

0 ,因為在處理器邏輯與內存間存在的性能差異正隨著每次工藝技術的變化而逐步增大。實際上,內存存取延遲的改進及每個工藝技術步驟接收內存請求的時間都比處理器內核邏輯的同量時鐘速率提高要少。

2020-04-23 08:02:00 2100

2100

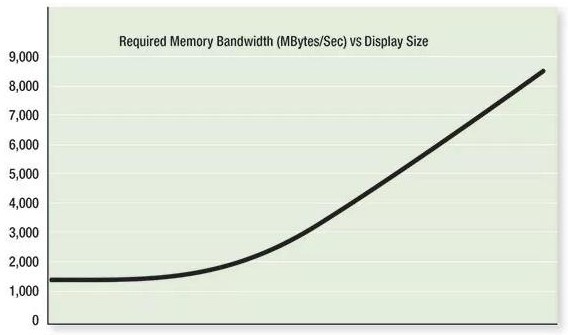

數個先進的處理器系列和架構也伴隨視頻技術的發展而發展,最新一代設計足以處理智能監控和視頻回放。在所有的設計中,都使用了外部總線接口并且大多使用高速外部DRAM。最先進的處理器可以處理幾GB內存尋址,支持DDR、SDR等數種同步高速內存接口。設計人員在設計架構系統時需要持續關注內存帶寬的大小。

2019-08-06 08:12:00 2706

2706

九代酷睿處理器的內存控制器可以支持16GB核心容量,單條32GB的DDR4內存。

2018-10-25 14:21:40 5494

5494 這位工程師表示,如果在使用Celeron處理器的設備上移除圓角,每秒幀數就會增加,內存也會改善。Pixel Slate的低端版本配備的就是Celeron處理器,大部分與延遲相關的投訴都出現在這個版本的平板電腦上。延遲的另一個原因是谷歌強制對GPU內存做了限制。

2019-01-03 16:08:50 1183

1183 本文目的是要理清ARM處理器的CPSR狀態標志和ARM指令的條件符之間的關系。

2019-11-25 18:01:19 8

8 手機可以看作是一個小型的電腦設備,手機運行卡不卡不但和手機芯片、內存、閃存有關系,而且和手機的做工、用料以及系統優化都有很大關系,任何一個方面存在短板,都可能導致手機的卡頓。

2020-01-12 10:02:13 17804

17804 目前,英特爾的十代酷睿處理器采用了全新的內存控制器,提高了對內存頻率的支持,支持LPDDR4-3733MHz內存以及DDR4-3200MHz內存(前者用于移動端,后者用于桌面端),這對提升專業應用以及游戲的加載速度都有幫助。

2020-04-12 10:50:19 8469

8469 如何選購手機 ?處理器和內存哪個更重要?原則上來講,手機的每個部件都很重要,都是相輔相成的,離開誰都不行。如何選購手機?當然我們在挑選手機的時候,也會不自覺的關注自己對手機感興趣的點,比如屏幕、處理器、電池容量、攝像拍照、系統等都是大家在糾結“如何選購手機?”時候比較關注的。

2020-05-25 09:50:36 6710

6710 一體式水冷大家都不陌生,兼顧處理器和顯卡的水冷也不少,但是你見過同時給處理器、內存散熱的水冷嗎?曜越今天就發布了全球首款處理器內存一體式水冷——Floe RC360、Floe RC240。

2020-06-05 11:29:44 3726

3726 比較有經驗的小伙伴裝機的時候,插內存這個活兒已經是很熟練了,所以小編要是問你知道怎么插內存嗎?肯定會被鄙視的吧。還真別急,如果是最近裝機的話,特別是使用高頻內存的AMD處理器裝機的話,趕緊去看

2020-08-24 11:08:24 3416

3416

小編聊到過內存延遲這種參數,對整個系統來說,內存延遲的影響遠不如容量、頻率等。不過有時候,內存延遲可不僅和內存條能力有關,而且會明顯影響整個電腦的性能,這是腫么回事呢?有點看糊涂了的小伙伴別急,小編

2020-09-09 10:53:06 10828

10828

Deep Vision 是一家致力于為邊緣計算解決方案打造人工智能推理芯片、成立至今已有六年的初創企業。該公司宣布推出了全新的 ARA-1 處理器,有望在低延遲、高效能、以及計算性能之間找到合適

2020-11-17 14:51:29 2585

2585 現在,有國外博主做了一個有趣的視頻,主要是來對比不同內存大小,對M1處理器的影響。

2020-11-24 09:21:33 3280

3280 2020年半導體市場的表現超出了大家的認知,年初還擔心經濟下滑導致市場萎縮,沒想到的是疫情也改變了經濟,數字化大發展,而半導體行業現在擔心的是產能緊張,而且是全行業的,明年處理器及內存都預測會缺貨到無法想象。

2020-12-01 11:00:27 1883

1883 三星宣布新的HBM2內存集成了AI處理器,最高可提供1.2 TFLOPS嵌入式計算能力,使內存芯片本身可以執行CPU、GPU、ASIC或FPGA的操作。

2021-02-20 16:35:46 2591

2591 EE-171:ADSP-BF535 Blackfin?處理器多周期指令和延遲

2021-04-13 18:24:37 0

0 EE-220:將外部內存與第三代SHARC?處理器和并行端口配合使用

2021-04-17 11:17:41 1

1 EE-197:ADSP-BF531/532/533 Blackfin?處理器多周期指令和延遲

2021-04-26 19:39:05 12

12 EE-295:在SHARC?處理器上實現延遲線

2021-05-19 15:11:17 1

1 EE-171 ADSP-BF535 Blackfin?處理器多周期指令和延遲

2021-06-18 11:47:28 10

10 ,在能源效率、工作負載容量和容器密度等方面預計可提高3倍。 Power10處理器作為POWER架構系列服務器產品中的最新一代中央處理器產品,多項創新技術備受關注,開放的內存接口、超高的內存帶寬,更低的最低延時,Power10進一步突破“內存墻”限制,樹立了高端處理器的新標桿。 單核

2021-11-18 16:30:58 1103

1103

芯片集成了上外圍器件,CPU不帶外圍器件是高度集成的通用結構的處理器。芯片可以制成不同的形狀和尺寸,廣泛應用于多個領域。

2022-01-03 08:29:00 10853

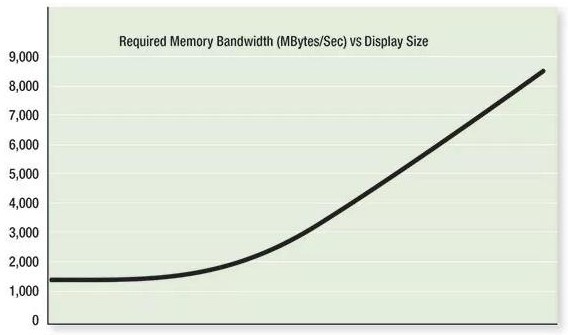

10853 典型的DSP通常具有少量快速片上存儲器。微控制器通常可以訪問更大的外部存儲器。Blackfin處理器具有分層內存架構,結合了兩種方法的優點,提供具有不同性能級別的多個級別的內存。對于需要最大確定性

2023-02-02 13:50:09 1471

1471

人工智能處理器的主要優勢在于它們的高效能力、低功耗和低延遲。與基于CPU或GPU的通用處理器相比,AI處理器通常具有更高的能效比,這意味著它們可以對更多的數據進行處理,在更短的時間內完成任務。

2023-08-13 16:45:31 3487

3487 微處理器由以下幾個主要組成部分構成:控制單元、算術邏輯單元、寄存器組和高速緩存。 控制單元:控制單元是微處理器的核心組成部分,負責協調和控制整個微處理器的運作。它包括指令譯碼器、時鐘發生器和程序

2024-02-22 10:40:10 5554

5554 、內存、總線和I/O接口等。 處理器核心: 處理器核心是嵌入式微處理器的核心組成部分,負責處理指令和數據。常見的處理器核心包括單核心和多核心。單核心處理器核心由一個處理單元組成,它能夠執行一個指令流,一次只能處理一個

2024-04-21 09:32:16 1473

1473 嵌入式微處理器是指集成在嵌入式系統中的微處理器,它是一種專門針對特定應用的定制處理器。嵌入式微處理器的主要組成包括核心處理單元、內存、外設、總線和輸入/輸出(I/O)接口等。 核心處理單元: 核心

2024-05-04 15:48:00 3520

3520 的原因、影響以及解決方案。 一、通信延遲的原因 網絡延遲 :在基于以太網的通信中,網絡延遲是導致通信延遲的主要原因之一。 硬件性能 :PLC和上位機的處理器速度、內存容量等硬件性能不足可能導致處理速度慢,從而產生延遲。 軟件設計

2024-06-06 09:58:56 8952

8952 圖像處理器與計算機視覺是兩個在圖像處理領域緊密相連但又有所區別的概念。它們之間的關系和區別可以從多個維度進行探討。

2024-08-14 09:36:41 1401

1401 內存延遲是指等待對系統內存中存儲數據的訪問完成時引起的延期,它是衡量內存響應速度的重要指標。影響內存延遲的因素眾多,主要包括硬件因素和軟件因素兩大方面。

2024-09-04 11:46:51 5152

5152 內存緩沖區和內存之間的關系是計算機體系結構中一個至關重要的方面,它們共同協作以提高數據處理的效率和系統的整體性能。

2024-09-10 14:38:54 1687

1687 微處理器(Microprocessor)與CPU(Central Processing Unit,中央處理器)之間的關系緊密且復雜,它們既相互關聯又有所區別。

2024-10-05 14:57:00 4541

4541 對稱多處理器(Symmetric Multi-Processing,簡稱SMP)是一種多處理器系統,其中多個處理器共享相同的物理內存和其他資源,并且操作系統將它們視為單一的邏輯處理器。SMP系統

2024-10-10 16:36:10 1595

1595 前端總線(Front Side Bus,FSB)是計算機中處理器與內存、北橋芯片之間數據傳輸的通道。在計算機系統中,前端總線頻率是衡量數據傳輸速率的一個重要指標。內存則是計算機的主要存儲部件,用于

2024-10-10 17:14:02 1433

1433 隨著技術的發展,計算機系統對性能的要求越來越高。PCIe作為連接處理器、內存、存儲和其他外圍設備的關鍵接口,其性能直接影響到整個系統的表現。PCIe延遲,作為衡量數據傳輸效率的重要指標,對系統性

2024-11-26 15:14:20 3381

3381 設計中,內存要求很簡單,由用于操作的SRAM和滿足非易失性存儲要求的EPROM組成。在20世紀80年代初,內存和微處理器之間的關系變得顯而易見。摩托羅拉的MC68000系列和類似CPU等產品推動了對高容量內存的需求。與此同時,連接到內存的標

2024-12-24 13:45:25 994

994 電子發燒友網站提供《EE-171:ADSP-BF535 Blackfin處理器多周期指令和延遲.pdf》資料免費下載

2025-01-05 09:47:40 0

0 電子發燒友網站提供《EE-295:在SHARC處理器上實現延遲塊.pdf》資料免費下載

2025-01-06 14:34:06 0

0 電子發燒友網站提供《EE-197:ADSP-BF531/532/533 Blackfin處理器多周期指令和延遲.pdf》資料免費下載

2025-01-08 14:39:05 0

0 Ampere 發布了旗艦產品 AmpereOne 處理器的新版本,擁有 12 個內存通道的最新處理器。正如 Ampere 在去年5月份的年度戰略和產品路線圖更新中提到的,公司正在構建

2025-01-09 13:44:14 1015

1015

電子發燒友App

電子發燒友App

評論