0 引 言

??? 短波通信是利用地波或低電離層進行幾十千米到幾百千米的中、近距離通信,利用電離層反射進行數千乃至上萬千米的遠距離通信。受電離層中存在瑞利衰落、多徑效應、多普勒頻移等復雜時變因素的影響,短波通信設備在測試和定裝工作耗費較大。為了測試各種短波無線通信系統的性能,通常有兩種方法,一種是實驗測試,另一種是信道模擬。在實驗測試中,為了測試短波通信設備的性能,往往需要在實際通信環境中進行大量的、遠距離的場外實驗和長時間的測試,實現起來非常困難;信道模擬方法則是通過對信道特性進行理論分析,建立信道模型,在實驗室環境下進行與實際信道類似的模擬,它可以很容易地制造各種典型信道特性環境和電磁環境,能夠模擬的地域度非常廣闊,不受氣候條件限制,可以隨時進行多次重復實驗,而且測試費用少,可以縮短通信設備的研制周期。在各種典型短波信道模型中,Watterson模型由于大多數情況下能夠較好地反映短波信道的特性,且復雜度低,而被CCIR推薦并廣泛使用。

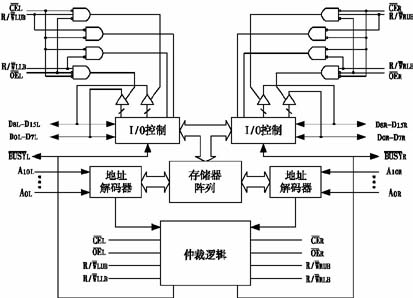

??? 在研究短波信道中有一個重要問題,即是多徑的傳播問題。多徑傳播主要帶來兩個問題:衰落和延時。多徑延時是指多徑中最大的傳輸延時與最小的傳輸延時之差。多徑時延在短波線路上,最嚴重時時延可達到毫秒級。短波信道模擬器研究中,由于要求的延時尺寸比較大,而且延時的精度要盡可能的高,再加上實時性的原因,數據量非常大。為了后續的DSP的算法處理和前面A/D的數位和精度要求,可以選用大容量存儲器作大尺度的延時處理,并選用DSP作插值算法做高精度的小尺寸的延時算法處理。本文重點對高精度小尺寸延時算法進行研究,提出一種基于內插技術的實現方法。

1 內插抽取器實現結構

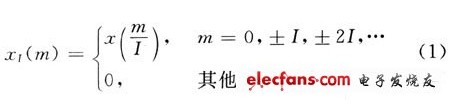

??? 整數倍內插就是指在兩個原始抽樣點之間插入I-1個零值。原始序列x(n)內插后的序列和頻譜分別為:

???

??

??

??

??? 由式(2)可見,內插后信號頻譜為原始序列譜經I倍壓縮后得到的譜。在頻譜圖中不僅含有X(ejω)的基帶分量,而且還含有其頻率大于π/I的高頻成分(稱其為X(ejω)的高頻鏡像)。為了從XI(ejω)中恢復原始譜,則必須對內插后的信號進行低通濾波(濾波帶寬為π/I),經過內插大大提高了信號的時域分辨率。整數倍抽取是指把原始采樣序列x(n)每隔D-1個數據取一個,以形成一個新序列xD(m),即:

???

式中:D為抽取倍數,是正整數。xD(n)的離散傅里葉變換為:

???

??? 從式(4)可以看出,抽取序列的頻譜XD(ejω)為抽取前原始序列頻譜X(ejω)經頻移和D倍展寬后的D個頻譜的疊加和。如果x(n)序列的采樣率為fs,則其無模糊帶寬為fs/2。當以D倍抽取率對x(n)進行抽取后,得到的抽取序列xD(m)的取樣率為fs/D,其無模糊帶寬為fs/(2D);當x(n)含有大于fs/(2D)的頻率分量時,xD(m)就必然產生頻譜混疊,導致從xD(m)中無法恢復x(n)中小于fs(2D)的頻率分量信號。為了避免抽取帶來的頻譜混疊,需要用一數字濾波器(濾波器帶寬為π/D)對X(ejω)進行濾波,使X(ejω)中只含有小于π/D的頻率分量,再進行D倍抽取,則抽取后的頻譜就不會發生混疊。可以說XD(ejω)能準確地表示X(ejω)中小于π/D的頻率分量信號,所以這時對XD(ejω)進行處理等同于對X(ejω)的處理,但前者的數據流速率只有后者的1/D,大大降低了對后處理速度的要求。

??? 前面介紹的抽取和內插的結構對運算速度的要求是相當高的,這主要表現在抽取濾波器模型中的低通濾波器位于抽取算子之前,也就是說低通濾波器是在降速之前實現的;而對于內插器模型,其低通濾波器位于內插算子之后,也就是說內插器低通濾波器是在提速之后進行的。總之,無論是抽取器還是內插器,其抗混疊數字濾波均在高取樣率條件下進行,這大大提高了對運算速度的要求,對實時處理是極其不利的。下面將討論有利于實時處理的抽取器、內插器的多相濾波結構。

??? 設數字濾波器的沖擊響應為h(n),它的z變換定義為: 式中,N為濾波器長度。如果將沖激響應h(n)按下列的排列分成D個組,如N不為D的整數倍,則將h(n)后補零,使得濾波器長度N為D的整數倍,即N/D=Q,Q為整數,則:

式中,N為濾波器長度。如果將沖激響應h(n)按下列的排列分成D個組,如N不為D的整數倍,則將h(n)后補零,使得濾波器長度N為D的整數倍,即N/D=Q,Q為整數,則:

D-1。式(5)即為數字濾波器H(z)的多相濾波結構。針對本文的應用,此處給出一個I倍內插器多相濾波結構的實現框圖,如圖1所示。其中,Rk(z')=E(I-1-k)(z')。

??? 由圖1可見,此時的數字濾波器Rk(z)位于內插器之前,即濾波是在數據流提速之前進行的,這就大大降低了對處理器的要求,提高了實時處理能力。此外,多相濾波器結構的另一個好處是每一分支濾波器的系數由原來的N個減少到N/I個,可以減小濾波運算的累積誤差,有利于提高計算精度,降低對處理器字長的要求。圖2是多相結構內插濾波器的開關結構形式。它可以更清楚地說明多相結構內插濾波器是如何工作的。對輸入速率為Fs的數據流,經L個子濾波器后,每個子濾波器的數據流速度依然是Fs,但整個內插濾波器的數據流速度提高為I·Fs,此時用速率為I·Fs的開關對輸出數據流進行選擇,即完成了I倍內插數據的獲取。同樣可以得出D倍抽取器多相濾波結構。

2 時延算法的DSP實現

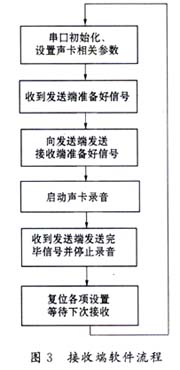

??? 短波信道模擬器系統中常采用軟件無線電思想實現。軟件無線電的宗旨就是盡可能地簡化射頻模擬前端,使A/D轉換盡可能地靠近天線去完成模擬信號的數字化,而且數字化后的信號要盡可能多地用軟件進行處理,實現各種功能和指標。軟件部分主要用DSP芯片來進行處理信號。根據軟件無線電的知識,可以使用內插來完成精確性時延部分的工作,但為了避免插值后數據量的大增,導致DSP處理的負荷量過重,之后就得考慮數據的抽取操作用以減少處理的數據量。在上部分中,可以得出內插和抽取過程都需要一濾波器進行濾波,避免內插帶來的高頻鏡像和抽取帶來的頻譜混疊。可以采用內插和抽取組合的辦法來解決內插所導致的數據量大增問題,并保證小尺寸時延的精度。但必須內插在前,抽取在后,以確保其中間序列的基帶譜寬度不小于原始輸入序列譜或輸出序列譜的基帶頻譜寬度,否則將會引起信號失真。這里采取的是D倍內插再D倍抽取以實現級聯來滿足要求。但是由于他們級聯的D倍內插濾波器和D倍抽取濾波器工作在相同的采樣率Dfs下,所以他們可以以一個組合濾波器來代替。圖3是基于內插和抽取技術的時延器結構。

??? 輸入信號x(n)的抽樣速率為fs,為實現延遲L/D個樣點間隔,首先將x(n)的抽樣速率增加到原來的D倍(即在x(n)的二個樣點間插入D-1個零),速率提高后的V(n)序列經低通濾波器濾波,低通濾波器的作用是濾除間隔為原抽樣頻率重復出現的成分。V(n)是x(n)內插后的序列,其抽樣速率為Dfs,u(n)在高抽樣率上延遲L個樣點后得ω(n),最后在ω(n)序列中,每D個樣點保留一個即得到y(n)。y(n)是x(n)延遲了(L/D)T的序列,這里T=1/fs是原序列的抽樣周期。在得出u(n)的過程中,經過的低通濾波器是FIR濾波器,V(n)序列經低通濾波器濾波時是利用![]() 產生的,但V(n)是通過x(n)的兩樣m=0點插零得到,也就是說在進行卷積運算時,將會有許多項是零乘以濾波系數的情況。根據規律可以得出,濾波系數每隔D個再相互與x(n)中相鄰數據相乘加得到。結合數字濾波器H(z)的多相濾波結構的知識,多相濾波器是由D個子濾波器構成的。各個子濾波器參數如下,其中N/D=Q,N為濾波器長度,Q為整數,令K=Q-1:

產生的,但V(n)是通過x(n)的兩樣m=0點插零得到,也就是說在進行卷積運算時,將會有許多項是零乘以濾波系數的情況。根據規律可以得出,濾波系數每隔D個再相互與x(n)中相鄰數據相乘加得到。結合數字濾波器H(z)的多相濾波結構的知識,多相濾波器是由D個子濾波器構成的。各個子濾波器參數如下,其中N/D=Q,N為濾波器長度,Q為整數,令K=Q-1:

????

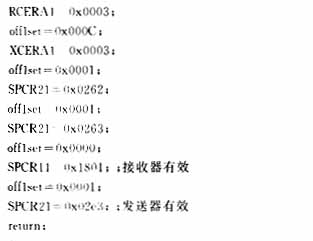

??? 在上面各子濾波器參數組中,相鄰濾波參數都相隔D個,也將是輸入信號x(n)依次通過各子濾波器后產生新的信號u(n),此時的抽樣周期TD=1/Dfs,即x(n)通過相鄰子濾波器后產生的輸出信號間的抽樣時間是一個抽樣周期1/Dfs。那么,x(n)依次通過子濾波器參數組中相距L相應的子濾波器時產生的輸出信號間抽樣時間是L/Dfs。這樣就能夠產生L個延遲樣點時間。最后再采取數據抽取工作。抽取工作其實可以采取對未被抽取的輸出信號相對應的數據進行內插濾波操作,而不對抽取的輸出信號相對應的數據進行內插濾波操作。這樣可讓DSP減少許多運算操作,節省DSP實現時延過程的執行時間,能夠保證信號數據的準確性。選用的DSP芯片是TI公司的TMS320C6416,主頻可以達到1 GHz,運算速度已達到8 000 MIPS,為32 b定點數字信號處理器。根據輸入信號x(n)的頻譜分析可得出最高頻率fmax(fmax≤fs/2),其中利用.Matlab或者SystemView軟件設計一個低通濾波器,得出濾波系數。

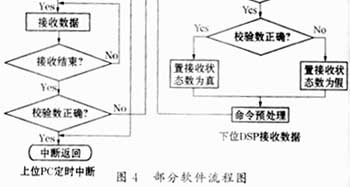

??? 設定一個輸入信號x(n)包含f1=6.25 MHz和f2=10 MHz的信號,采樣頻率fs=25 MHz,要使信號多徑時延精度達到1 ns,就要選擇內插倍數為40倍。設計一個最高頻率10 MHz的低通濾波器,得出含濾波器長度N=800的濾波器系數。將這些系數分為40個子濾波器參數組,每組中含有20個濾波系數,分別依次取子濾波器參數組組名為Group1,Group2,…,Group40。當信號需要延時5 ns時,通過內插后則需要5個采樣樣點延遲時間,然后再進行抽取實現。在DSP中算法的實現,是將包含f1=6.25 MHz和f2=10 MHz輸入信號通過相對應的Group5子濾波器進行FIR卷積。在DSP系統的硬件仿真結果中可以得出輸入輸出信號時域波形圖及其頻譜圖。圖4是輸入、輸出信號時域波形比較圖。

??? 從圖4可以看出,在輸入信號x(n)經過40倍內插濾波器濾波,并進行40倍抽取實現后的輸出信號與輸入信號有著相同的時域波形,并且輸出信號時域波形相對輸入信號時域波形出現了相應的延時。

??? 圖5為輸入、輸出信號的頻譜圖。

??? 在原始采樣頻率fs為25 MHz下,輸入信號x(n)經過40倍內插濾波器濾波并進行40倍抽取實現后,對輸入輸出進行頻譜分析,可以得出輸出信號的采樣頻率仍是25 MHz,并含有兩個頻率信號,其一信號頻率f1=6.25 MHz,另一信號頻率f2=10 MHz。從而得出輸出信號頻譜與輸入信號頻譜是吻合的,如圖5所示。

3 結語

??? 提出了一種實現時延的方法。可以選用大容量存儲器作大尺度的延時處理,并選用DSP作插值算法做高精度的小尺寸的延時算法處理。結合軟件無線電思想中的內插和抽取技術,重點介紹高精度、小尺寸的信號延時處理方法。它具有DSP處理時間周期短,節省DSP數據存儲空間,時延精度高等特點。用實驗板SEED-DEC6416進行硬件仿真。試驗結果表明,設計結果基本達到要求,該方法的實現過程是可行的。

?

- dsp(364922)

- 時延算法(5010)

短波通信中實現時延的設計方法

2589

2589

基于一種DRM短波通信設備的應用研究

3225

3225OFDM在短波通信中的應用

3759

3759DSP的實現方法

一種修正的近場聲源定位時延估計方法

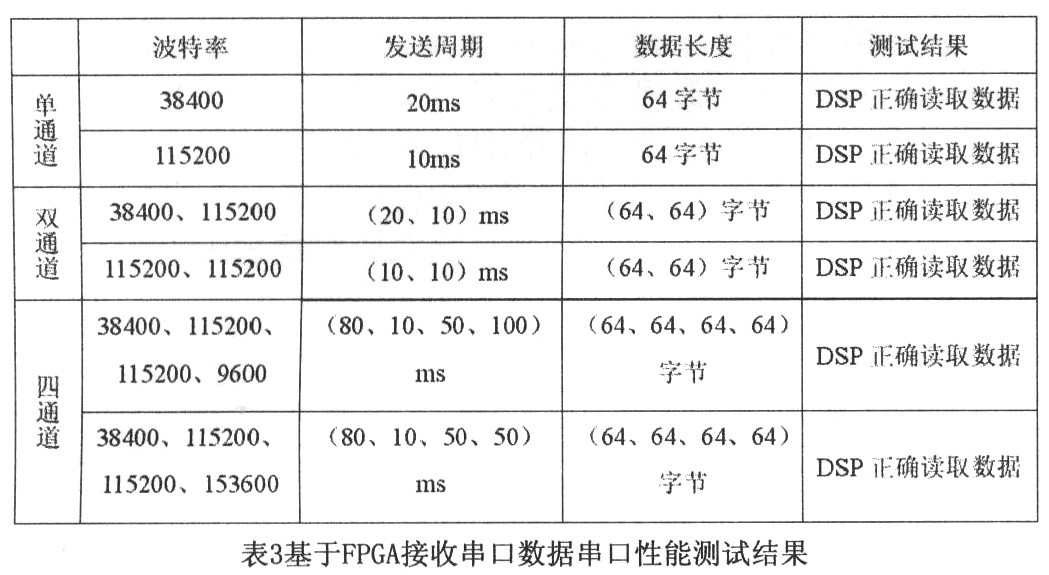

一種基于FPGA的UART實現方法設計

一種基于FPGA的全數字短波解調器設計

短波頻率自適應通信的未來發展趨勢是什么?

基于TMS320C54X系列DSP實現跳頻通信網位同步方案

基于軟件無線電的高速QPSK調制器的設計與實現

如何利用AMBE-2000設計并實現一種基于AMBE-2000的語音系統?

帶大家一起了解高頻微波無線電通信天線

怎樣去實現一種基于DSP和ADC技術高速緩存和海量緩存?

求一種基于DSP的CAN總線通信控制方案

求大佬分享一種嵌入式系統中串口通信幀的同步方法

一種高性能多DSP處理模塊的設計及實現

13

13一種嵌入式系統通信中間件的設計

35

35串行通信波特率的一種自動檢測方法

27

27短波通信中均衡技術的研究

13

13一種基于DSP Builder 的軟件無線電調制器的設計與實

35

35一種特殊陣列實現DOA估計的方法

19

19一種基于TMS320C55x DSP的UART通信設計

26

26直接序列擴頻短波MODEM的DSP實現

16

16DSP與單片機的一種高速通信實現方案

1152

1152

TMS320LF2407A與PC多機串行通信的一種典型方法

1239

1239

一種通過SPI接口協議實現DSP與其它設備通信的方法

2715

2715

一種通信信號傳輸仿真的實現方法

2287

2287

串行通信波特率的一種自動檢測方法

2194

2194

短波頻率管理系統及在通信中的應用

2187

2187利用FPGA技術實現數字通信中的交織器和解交織器

1577

1577

Boost電路的一種軟開關實現方法

9496

9496

基于DSP實現的一種新穎開關逆變電源

852

852

小波在擴頻通信中的應用

1311

1311

一種基于FPGA和SC16C554實現多串口通信的方法

2603

2603

一種寬帶地空通信系統組網方案

61

61NDLC通信中的數據轉發原理

21

21一種PCI總線ARINC429通信卡實現方法

43

43異步FIFO在FPGA與DSP通信中的運用

51

51DSP 和MCS51單片機的一種通信方案的設計與實現

0

0DS-QPSK短波擴頻猝發通信的系統方案研究

5

5異步FIFO在FPGA與DSP通信中的應用解析

3

3短波頻率自適應通信技術解析

17674

17674插入式短波預失真器的設計與實現

0

0短波猝發通信中的均衡器研究

1

1語音通信中時延產生測量及減小方法

3534

3534語音通信中時延時延是怎么產生的?該如何減小?

6196

6196

如何使用FPGA實現短波通信接收機的設計

3

3影響短波通信的主要因素 改善短波通信的方法

5763

5763短波通信的優點與缺點有哪些

7200

7200專業野外短波光端機:為短波通信通過光纖遠程傳輸提供可靠保障

452

452

電子發燒友App

電子發燒友App

評論