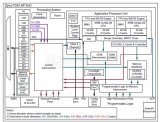

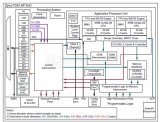

描述此參考設計是基于 66AK2Gx DSP + ARM 處理器片上系統 (SoC) 和配套 AIC3106 音頻編解碼器的參考平臺,可提供實現音頻處理算法設計和演示的捷徑。該音頻解決方案設計包括

2018-10-19 15:35:45

DSP D 56371AF180 處理器是否包括 DSP B 56371AF180 的所有功能?也就是說,DSP D 56371 在其軟件代碼中有 Generic、mini-SA 和 PPP 作為其

2023-06-02 08:46:52

DSP處理器與通用處理器的比較1 對密集的乘法運算的支持GPP不是設計來做密集乘法任務的,即使是一些現代的GPP,也要求多個指令周期來做一次乘法。而DSP處理器使用專門的硬件來實現單周期乘法。DSP

2021-09-03 08:12:55

對比項屬性/特征 硬件乘法器/累加器AUL 通用的MCU在執行乘法操作時是通過軟件編程的方式的來實現的,通常需要幾十甚至上百個時鐘周期,而DSP處理器卻有自己的硬件乘法器,使用硬件的方式來執行乘法

2021-11-03 08:41:44

怎樣根據某些條件選擇DSP處理器的類型?比如:要求數據輸出時間間隔為1ms,速度數據類型為1個浮點型類型數據。急求大神指導!謝謝了!我對DSP處理器不太了解,暫時會用到這個技術。求指導!

2013-06-08 23:33:51

處理器存貯器的帶寬加倍,更重要的是同時為處理器核提供數據與指令。在這種布局下,DSP得以實現單周期的MAC指令。 還有一個問題,即現在典型的高性能GPP實際上已包含兩個片內高速緩存,一個是數據,一個

2011-01-07 15:34:45

ADSP2106x的Link口組成多DSP互連并行系統 首先對ADSP2106x做一簡單介紹。ADSP2106x是一種高性能的32 b數字信號處理器,采用超級哈佛結構。內有3條片內總線,他們是PM總線(程序存貯器

2019-04-08 09:36:19

我沒有在當前文檔中找到明確的答案:兩個內核同時訪問 SRAM 是如何處理的?內部 SRAM 是雙端口的(我的意思是兩個內核可以在沒有額外等待狀態的情況下尋址和訪問同一個 SRAM),還是存在某種仲裁

2023-03-01 06:49:21

的是DSP133.33MHZ,當時鐘上升沿來到的時候,讀取DSP地址線上的數據,存入sram_wa中。lcd_sram1_d和lcd_sram2_d是從DSP的16根數據線上讀出來的數據,通過原語存入這兩個

2014-03-26 10:14:48

SRU)。如第1頁圖1所示,處理器使用兩個計算單元,在一系列DSP算法上比以前的SHARC處理器提供顯著的性能提升。使用SIMD計算硬件,處理器可以在450mhz下運行2.7gflops,在

2020-10-12 17:17:43

ARM946E-S? 是一個可合成的宏小區,結合了ARM9E-S? 帶指令和數據高速緩存的處理器核心、帶保護單元的緊密耦合指令和數據SRAM存儲器、寫緩沖區和AMBA? (高級微處理器總線體系結構

2023-08-02 17:50:31

SPI Flash中代碼搬到 SRAM中運行,應該如何操作?需要自行編程?

4. 看到有兩個文件 SRAM.mac 和 SPIROM.mac ,其功能是什么?

2023-06-16 08:18:54

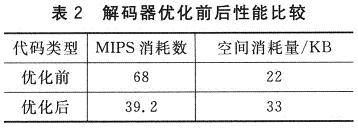

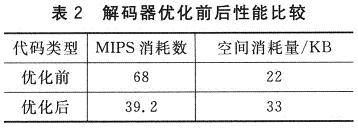

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統下配置使用處理器片內SRAM的應用方案,有效提高了代碼的解碼效率,降低了執行功耗。該方案不論在性能還是成本上都得到了很大改善。

2019-09-24 07:09:13

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統下配置使用處理器片內SRAM的應用方案,有效提高了代碼的解碼效率,降低了執行功耗。該方案不論在性能還是成本上都得到了很大改善。

2020-03-05 07:01:34

種布局下,DSP得以實現單周期的MAC指令。 還有一個問題,即現在典型的高性能GPP實際上已包含兩個片內高速緩存,一個是數據,一個是指令,它們直接連接到處理器核,以加快運行時的訪問速度。從物理

2014-04-17 10:45:08

用于SHARC處理器的ADZS-21489-EZLITE,ADSP-2148x EZ-KIT Lite評估系統。 SHARC處理器基于32位超級哈佛架構,包括一個獨特的內存架構,由兩個大型片上雙端口

2020-03-16 10:19:26

SPC58EC 有一個中斷控制器,支持兩個處理器。您可以為每個核心提供不同的向量表。假設兩個內核處于活動狀態并且發生了一個外部中斷(ADC,定時器),這之后的過程是什么?哪個內核將運行中斷處理程序?

2022-12-12 08:10:22

2106x只具有SISD(單指令流單數據流)功能。為了充分利用這種新的功能,一些指令做了一些改變。ADSP21160包括1個100/150MHz的運算核、雙端片內SRAM、1個支持多處理器的集成在片內

2019-04-03 09:40:03

應用處理器與MCU“跨界”處理器—從性能差距到新解決方案領域降低成本—去除片內閃存集高性能、低延遲、高能效和安全性于一體相關行業和應用 i.MX RT跨界處理器

2021-02-19 06:06:39

嗨,我有新的要求,我必須開發一臺有10個電極和12個引線的心電圖機,它將通過USB向PC機發送數據,PC機應用程序將顯示心電信號。我對ECG系統設計是全新的,為什么需要DSP處理器?我需要開發哪個過濾器?問候,Akshay

2020-03-13 07:13:48

處理器,有TI的C66x系列、ADI的Blackfin系列。二、DSP處理器有什么特點?你可以把DSP處理器想象成一個科學計算器。它非常擅長做運算。1、并行性。某些型號的DSP處理器內部有兩個獨立的乘法器

2020-09-04 10:31:13

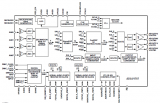

本文提出了一個通用微處理器(ARM)與DSP的接口設計方案,以實現兩者的實時通信。

2021-06-08 06:36:41

ADZS-21369-EZLITE,ADSP-21369用于SHARC處理器的EZ-KIT Lite評估系統。 SHARC處理器基于32位超級哈佛架構,包括一個獨特的內存架構,由兩個大型片上雙端口

2020-03-16 10:19:26

上的片內FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來分擔FIR和IIR處理任務,讓內核去執行其他處理任務。在本文中,我們將借助不同的使用模型以及實時測試示例來探討如何在實踐中利用這些加速器。

2020-12-28 06:26:54

我現在的板子上有兩片C6678dsp,請問,如何在一個打開的CCS5界面下面創建用于這兩個c6678DSP的工程,然后如何進行load和調試?還是說要打開兩個CCS5界面?

另外,如果每個DSP我需要用兩個核(0核和1核),那該怎么創建工程呢?是不是要創建4個工程,寫4個main函數?

2018-06-21 05:21:59

如何去選擇數字信號處理器 (DSP)?

2021-05-25 07:20:05

你好,我打算建立通信以在兩個處理器之間讀寫。一方面是ASIC(MCIMX6)上的四核ARM Cortex A9處理器,另一方面是FPGA(ZC7020)。我在FPGA端沒有任何PCIe硬端口。因此

2020-04-16 09:04:30

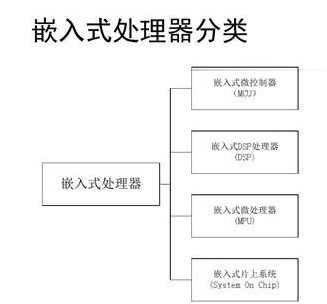

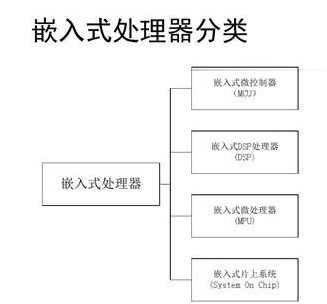

處理器DSP4、嵌入式片上系統SOC(System-on-a-Chip)三、多核處理器四、嵌入式操作系統EOS五、嵌入式實時操作系統RTOS六、嵌入式系統設計七、嵌入式系統的軟件一、嵌入式微處理器體系結構1、馮諾依曼體系結構(1)程序和控制共用一個存儲

2021-11-08 06:57:02

如題,本人在參與的一個項目,用到DSP TMS320C6472 六核處理器。準備使用其中兩個核來相關處理。每個核的代碼我已經寫好,但是本人是DSP新手,現在不知道怎么鏈接.out文件使其從Flash

2013-12-16 09:12:49

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統下配置使用處理器片內SRAM的應用方案,有效提高了代碼的解碼效率,降低了執行功耗。該方案不論在性能還是成本上都得到了很大改善。

2021-04-26 07:01:55

本帖最后由 luna 于 2011-3-3 13:12 編輯

不斷發展的DSP技術迅速地拓寬擴展到了各應用領域,但傳統的DSP處理器由于以順序方式工作而數據處理速度較低,且在功能重構及應用目標

2011-03-03 10:05:43

用于SHARC處理器的ADZS-21479-EZLITE,ADSP-2147x EZ-KIT Lite評估系統。 SHARC處理器基于32位超級哈佛架構,包括一個獨特的內存架構,由兩個大型片上雙端口

2020-03-13 09:35:38

ADZS-21262-EZLITE,ADSP-21262 EZ-KIT Lite評估系統,用于SHARC處理器。 SHARC處理器基于32位超級哈佛架構,包括一個獨特的存儲器架構,由兩個大型片上雙

2020-03-13 09:30:16

問個問題,能不能利用低成本前兩三代的arm處理器來搭架一個萬元內的超算?

2022-09-13 14:59:36

做了一款基于arm處理器的SOC芯片,流片回來后測試發現,ARM能正常和片內SRAM和ROM通信,卻不能和片外SRAM進行通信,請教高手,ARM不能和片外SRAM通信的可能的原因?

2022-06-10 15:50:38

請問SRAM 存儲數據具體是怎么存儲的? 還有就是在處理器和SRAM之間用VERILOG實現一個總線仲裁器怎么實現?謝謝高手指教!

2008-08-28 20:31:21

AVR對片內SRAM的訪問需要多久?

2023-10-24 07:49:15

28027片內有兩個比較器,想利用起來。從母線電流采集過來的信號輸入片內比較器的一個腳,跟給定電壓信號比較,超過后就翻轉觸發保護。可以這樣做嗎?

2020-07-22 14:58:01

最近接觸到了DSP處理器,關于定點處理器處理浮點運算有兩個疑問,我是用C語言開發的,16位處理器,兩個浮點數進行加減乘除,定點處理器運算出來結果的精度有多高,能保留幾位有效數字??另外,關于定點

2019-05-13 01:09:48

DSP處理器的選擇 Choosing a DSP Processor

DSP processors are microprocessors designed to performdigital

2010-04-10 11:00:49 20

20 一種具有功耗管理特性的DSP處理器的結構設計。該處理器采用4級流水線和增強型的哈佛并行系統結構及完善的時鐘管理模塊,提供了一種DSP處理器的集成設計。

2010-11-19 14:45:37 21

21 什么是雙核處理器 什么是雙核處理器呢?雙核處理器背后的概念蘊涵著什么意義呢?簡而言之,雙核處理器即是基于單個半導體的一個處理器上擁有兩個一樣功能的處理器核

2006-10-12 09:47:11 17682

17682 Linux下ColdFire片內SRAM的應用程序優化設計

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統下配置使用處理器片內SRAM的應用方案,有效提高了代碼的解碼效率,降

2010-02-05 09:11:36 811

811

信號處理器(DSP),信號處理器(DSP)是什么意思

DSP是(digital signal processor)的簡稱,是一種專門用來實現信號處理算法的微處理器芯片

2010-03-26 14:53:54 16529

16529 數字信號處理器(DSP)

數字信號處理器(digital signal processor, 簡寫 DSP)是一種專用于(通常為實時的)數字信號處理的微處理器。

2010-01-04 10:54:54 3702

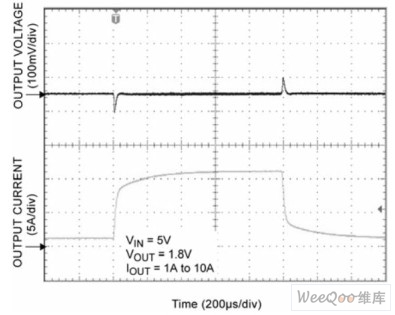

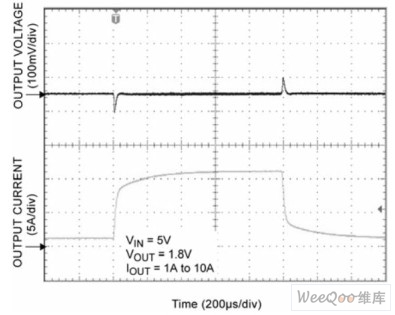

3702 為復雜的DSP處理器設計良好的電源是非常重要的。良好的電源應有能力應付動態負載切換并可以控制在高速處理器設計中存在的噪聲和串擾。DSP處理器中的不斷變化的瞬態是

2010-07-02 11:56:12 2150

2150

簡單來說,雙核處理器就是在一個硅片上集成兩個CPU。那么什么是雙核處理器呢?雙核處理器背后的概念蘊涵著什么

2010-10-08 18:21:50 1139

1139 摘 要:不斷發展的DSP技術迅速地拓寬擴展到了各應用領域,但傳統的DSP處理器由于以順序方式工作而數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。本文介紹一種嶄新的基于Matlab與QuartusII的DSP處理器的設計軟件DSP Builder,詳細介紹了其設計

2011-02-24 17:19:34 44

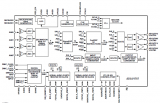

44 摘 要:以兩片由TI公司生產的數字信號處理器TMS320C6203B為核心,用可編程邏輯陣列CPLD進行邏輯控制,采用現場可編程門陣列FPGA作圖像的預處理和進行雙數字信號處理器(DSP)之間的通訊,實現了實時相關的圖像處理。此系統實時性好,可直接利用數字圖像的灰度特征,

2011-02-24 22:51:12 60

60 提供兩個獨立的DSP,可以插到帶有數據口的QSC功放后面板上,節省空間。 秉承DSP-3的優異表現,第二代DSP-4數字信號處理器在功能和性能上有了近一步提升,同時還結合了非常受歡迎的XLR平衡接口。這些新功能包括改善改善信噪比的新的轉換器和升級軟件,從而極

2011-02-28 11:15:14 58

58 現代的處理器(SoC)或DSP都內建有內存控制器,它是外部SDRAM、FLASH、EEPROM、SRAM……等內存的控制接口。但不同處理器內部的內存控制方式都不盡相同

2011-04-21 11:42:01 1374

1374 又有消息表示,小米目前已將有兩款松果處理器做好的發布的準備,其中一款就是上面提到的高通驍龍808,型號為松果V670。兩一款是相對高端的松果V970。

2017-02-09 16:11:45 1896

1896 的PS部分包含有兩個處理器內核,對于很多應用程序來說我們想要利用兩個處理器內核,這樣才能取得最大化的性能。

2017-02-11 10:06:11 2701

2701

小米將于2月28日(下周二)正式發布自家研發的松果處理器,最新的消息顯示,該處理器有V670和V970兩個版本,它們的細節信息也被曝光。

2017-02-23 11:41:19 803

803 如何選擇 DSP 處理器

2017-10-23 14:30:46 8

8 ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM,并集成

2017-10-24 15:45:33 7

7 為了滿足4G-LTE基站的需求,DSP制造商在其處理器中提供了更強大的處理能力和更大的吞吐量。這些多核處理器許多以GHz的速度運行并使用加速器來提高吞吐量。雖然這些新特性通過支持更多的通道提高了基站

2017-10-24 17:00:26 1

1 ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM,并集成

2017-10-25 10:04:46 0

0 利用賽靈思Zynq SoC 上的兩個ARM A9 內核可以顯著提高您的系統性能。賽靈思Zynq?-7000 全可編程SoC 的眾多優勢之一就是擁有兩個ARM? Cortex ? -A9板載處理器

2017-11-17 18:16:37 7649

7649

dsp數字信號處理器能實時快速地實現各種數字信號處理算法,它活躍于各種領域之中。

2018-01-03 09:26:07 22915

22915

目前DSP和EDA兩者都應用廣泛,二者之間有什么不同呢?本文帶來數字信號處理器DSP與EDA的區別介紹。

2018-01-03 10:33:19 6791

6791 OMAPL138B C6-Integra? DSP+ARM? 處理器是一款低功率應用處理器,此處理器基于一個 ARM926EJ-S? 和一個 C674x DSP 核心。 它消耗的功率大大低于TMS320C6000?平臺的其它 DSP 產品。

2018-04-13 15:57:12 6

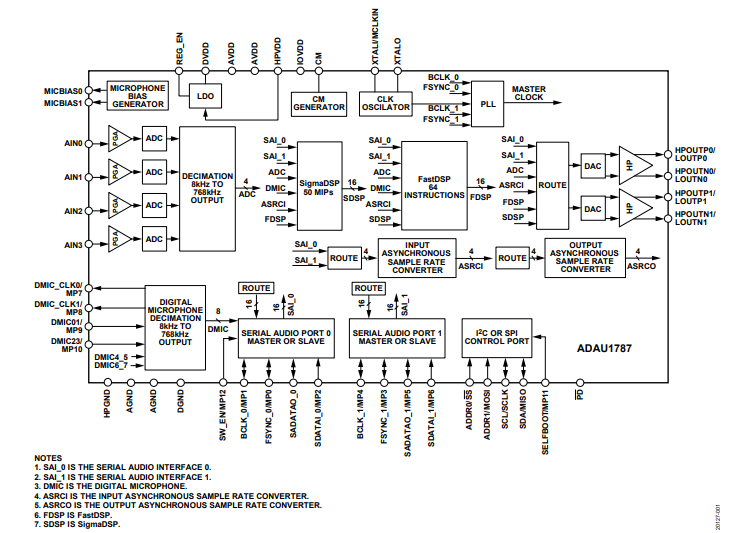

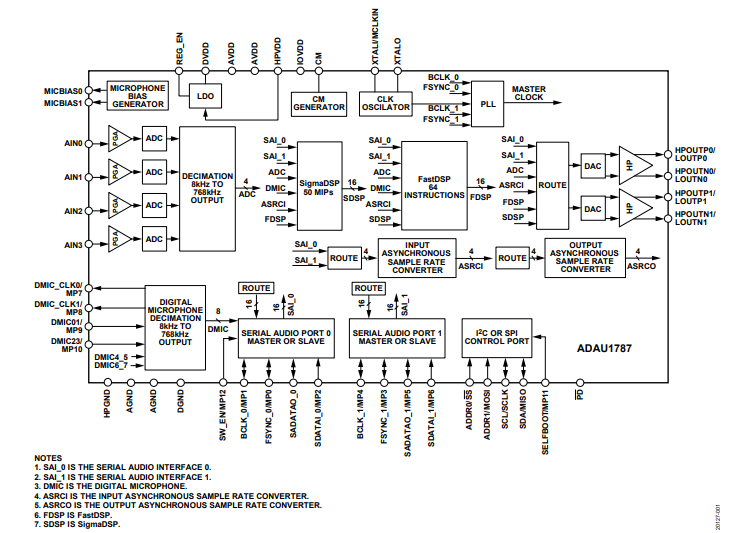

6 ADI公司的ADAU1787是集成了兩個數字信號處理器(DSP)的具有四個輸入和兩個輸出的編譯碼器(CODEC).ADAU1787具有可編程的FastDSP音頻處理引擎,高達768kHz取樣速率,雙

2019-05-01 16:24:00 7466

7466

嵌入式處理器分為嵌入式微控制器(MCU),嵌入式DSP處理器(DSP),嵌入式微處理器(MPU),嵌入式片上系統(system on chip)。

2019-10-05 17:39:00 5301

5301

基于TI TMS320VC5509A架構的定點DSP C55x音頻專用處理器,主頻200MHz,兩個ALU和兩個17x17位乘法累加器,高達400MMACS,支持DMA傳輸,運算能力強。

2019-11-11 14:38:51 3651

3651

大家都了解,CPU是負責計算和處理的,而存儲器則是負責互換數據信息的。有些人是那么形容的,說CPU便是技術工程師自己,運行內存就好像操作臺,必須妥善處理的物品必須先取得工作中臺子上才便捷解決。那么

2020-10-07 10:49:00 4758

4758

本文通過兩個變頻器不能啟動的故障處理案例,和大家分享控制電路設計存在缺陷和變頻器參數設置不符合應用要求導致的變頻器不能啟動的原因和處理辦法以及從這些故障處理中總結的經驗。

2020-11-01 11:04:15 6457

6457

統一編址,任何一片ADSP2106X都可以訪問其它ADSP2106X的片內存儲空間。由于片內SRAM為雙口存儲器,因而這種訪問并不中斷被訪問處理器的正常工作。在不增加輔助電路的條件下,通過外部總線接口(External Port)直接相連的處理器數量最多為6個,如圖1所示。

2020-11-10 10:24:58 1798

1798

ADAU1701:帶兩個ADC和四個DAC的SigmaDSP 28/56位音頻處理器產品手冊

2021-04-16 14:20:21 29

29 ADAU1401A:帶兩個ADC和四個DAC的SigmaDSP 28/56位音頻處理器產品手冊

2021-04-19 16:20:39 9

9 ADAU1772:四個ADC、兩個DAC低功耗編解碼器,帶音頻處理器數據表

2021-05-08 10:57:54 9

9 ADI處理器和DSP的μ模塊調節器

2021-05-14 21:21:02 3

3 EE-310:使用ADSP-BF537 Blackfin?處理器運行兩個網絡接口

2021-05-16 09:45:26 0

0 UG-477:評估采用音頻處理器的ADAU1772四個ADC、兩個DAC低功耗編解碼器

2021-05-24 09:09:08 5

5 EE-144:在兩個ADSP-2191 DSP之間創建主從SPI接口

2021-05-24 15:14:48 1

1 DSP處理器是設計用于執行數字信號處理的微處理器,。數字信號處理是快速處理的核心技術之一,不斷增長的應用領域,例如無線通信、音頻和視頻處理以及工業控制。

2021-06-23 10:01:18 26

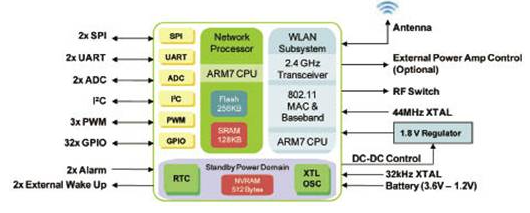

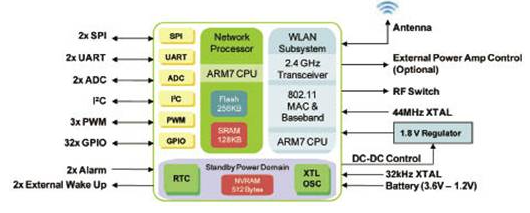

26 Freescale 公司的GS1011是一款高度集成的,超低功耗無線單晶片,它包含:一個無線802.11,媒體訪問控制器(MAC),基帶處理器,片上閃存,SRAM和一個應用處理器,全部在單一封裝內。

2021-06-26 14:28:36 2974

2974

/Processor,數字信號處理),另外兩個是MCU(Micro Control Unit,微控制器單元)和MPU(Micro Processor Unit,微處理器單元)。MCU集成了片上外圍器件;MP...

2021-10-28 11:20:59 23

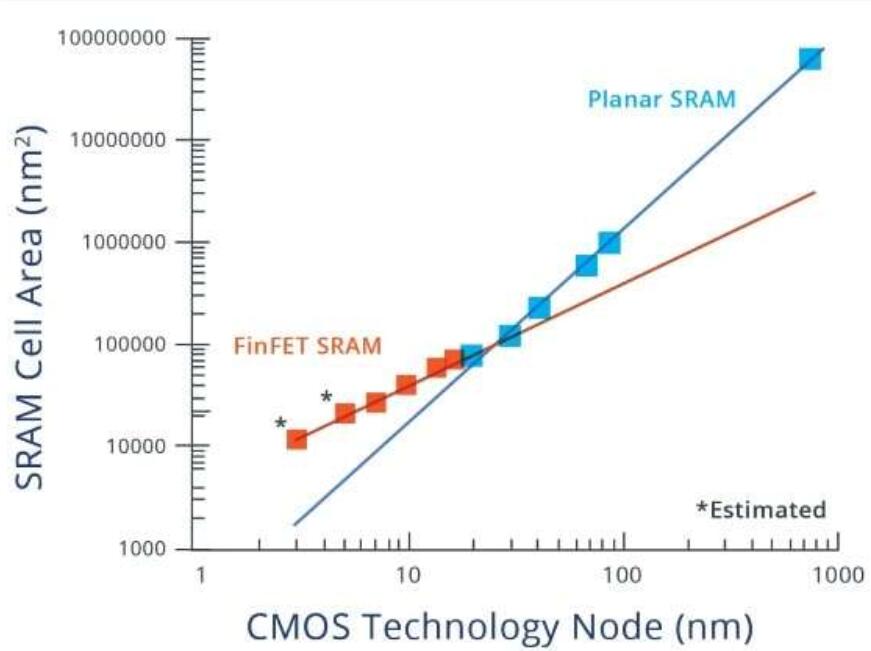

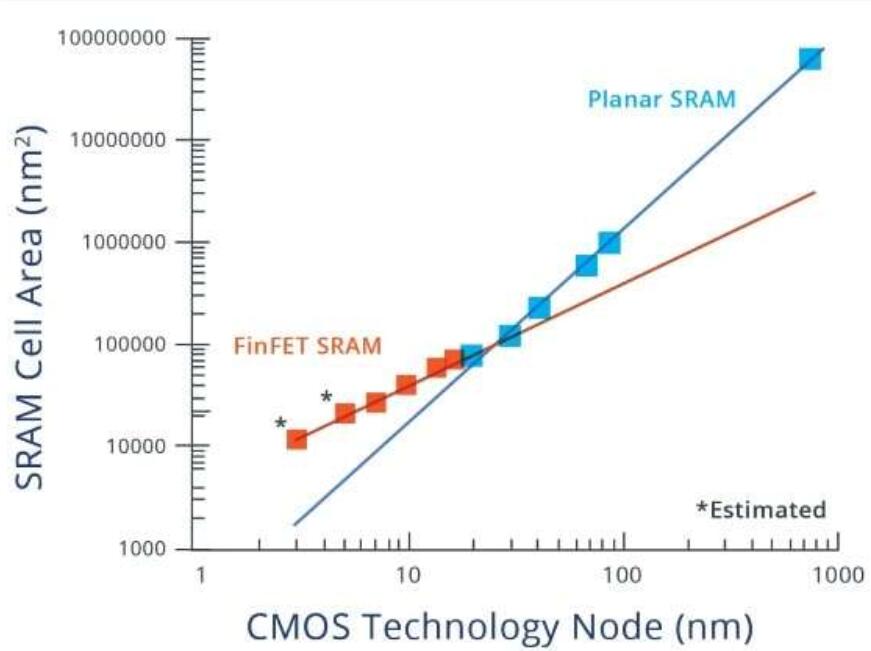

23 平面到FinFET的過渡對SRAM單元的布局效率有重大影響。使用FinFET逐漸縮小關鍵節距已導致SRAM單元尺寸的迅速減小。鑒于對更大的片上SRAM容量的需求不斷增長,這樣做的時機不會更糟。離SRAM將主導DSA處理器大小的局面并不遙遠。

2022-11-24 16:07:13 1556

1556

典型的DSP通常具有少量快速片上存儲器。微控制器通常可以訪問更大的外部存儲器。Blackfin處理器具有分層內存架構,結合了兩種方法的優點,提供具有不同性能級別的多個級別的內存。對于需要最大確定性

2023-02-02 13:50:09 1471

1471

摘要: 現代 信號 處理系統通常需要在不同處理器之間實現高速數據 通信 ,SRIO協議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實現SRIO協議的方法,并

2023-03-20 15:00:01 3756

3756 DSP處理器(Digital Signal Processor)是一種專門用于數字信號處理的處理器。與通用用途的微處理器(如普通的中央處理器)相比,DSP處理器具有更高的數據并行性和處理速度,更適合于實時信號處理和算法運算。

2023-07-27 17:21:51 6172

6172 許多處理器核心增加了一兩個乘法指令,就宣稱自己具有DSP功能,其實它還要有其它專門用于信號處理的處理器。但不是每個具有DSP功能的處理器都擁有完整的32位架構并以數百MHz的速度運行。許多應用只需16位功能和32位擴展即可。

2024-01-15 15:15:03 1607

1607

DSP(數字信號處理器)和嵌入式微處理器是兩種針對不同應用優化的處理器類型。本文將深入探討它們之間的技術差異、應用場景以及它們各自的優勢和局限。

2024-04-07 15:11:29 2849

2849 DSP(Digital Signal Processor,數字信號處理器)和嵌入式微處理器是兩種常見的處理器,用于不同的應用領域。 首先,讓我們了解一下DSP和嵌入式微處理器的基本概念。 DSP

2024-04-21 09:35:28 1929

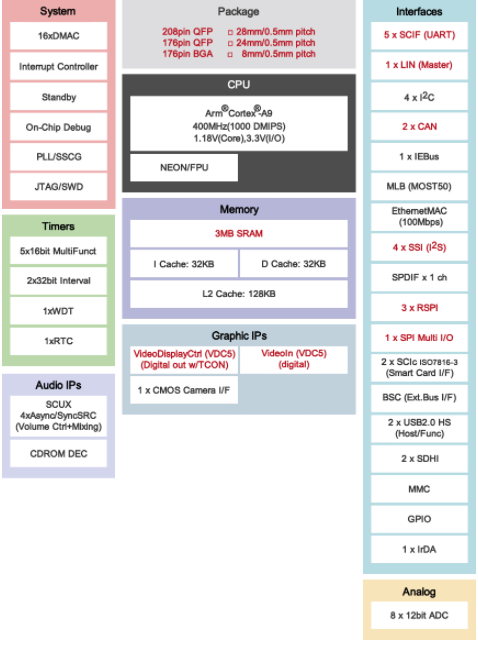

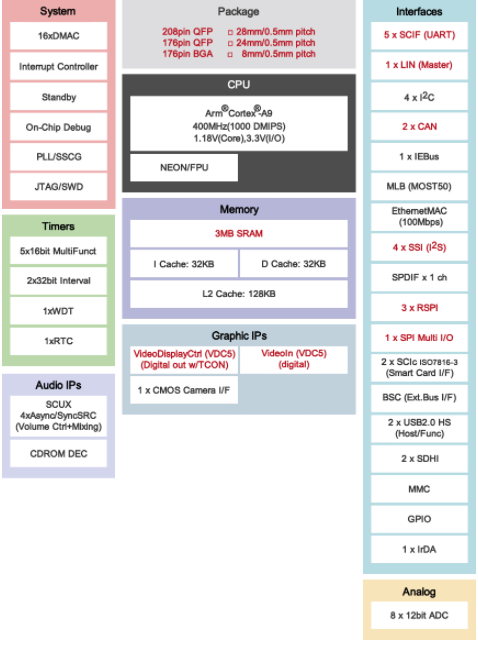

1929 RZ/A1L 系列微處理器(MPU)采用了運行頻率達 400MHz 的 Arm? Cortex? - A9 內核,并配備 3MB的片上靜態隨機存取存儲器(SRAM)。憑借這 3MB 的片上 SRAM

2025-03-10 16:14:20 981

981

ADAU1787 是一款具有四個輸入和兩個輸出的編解碼器,其中整合了兩個數字信號處理器 (DSP)。從模擬輸入到 DSP 內核再到模擬輸出的路徑已針對低延遲進行優化,適用于噪聲消除耳機。通過加入少量無源組件,ADAU1787 提供了完整的耳機解決方案。

2025-05-12 14:57:45 1289

1289

電子發燒友App

電子發燒友App

評論