FIFO是隊(duì)列機(jī)制中最簡(jiǎn)單的,每個(gè)接口上只有一個(gè)FIFO隊(duì)列,表面上看FIFO隊(duì)列并沒(méi)有提供什么QoS保證,甚至很多人認(rèn)為FIFO嚴(yán)格意義上不算做一種隊(duì)列技術(shù),實(shí)則不然,FIFO是其它隊(duì)列的基礎(chǔ)

2022-07-10 09:22:00 2156

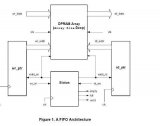

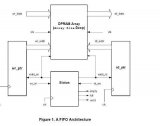

2156 FIFO (先入先出, First In First Out )存儲(chǔ)器,在 FPGA 和數(shù)字 IC 設(shè)計(jì)中非常常用。 根據(jù)接入的時(shí)鐘信號(hào),可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 3137

3137

FIFO自帶的set_max_delay生效? 對(duì)于異步FIFO,復(fù)位信號(hào)的使用要特別注意,如下圖所示。復(fù)位信號(hào)必須和wr_clk同步,如果異步,要在wr_clk時(shí)鐘下同步釋放,否則會(huì)出現(xiàn)數(shù)據(jù)無(wú)法寫(xiě)入

2023-11-02 09:25:01 2266

2266

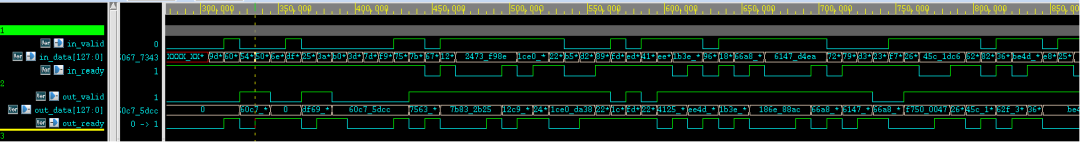

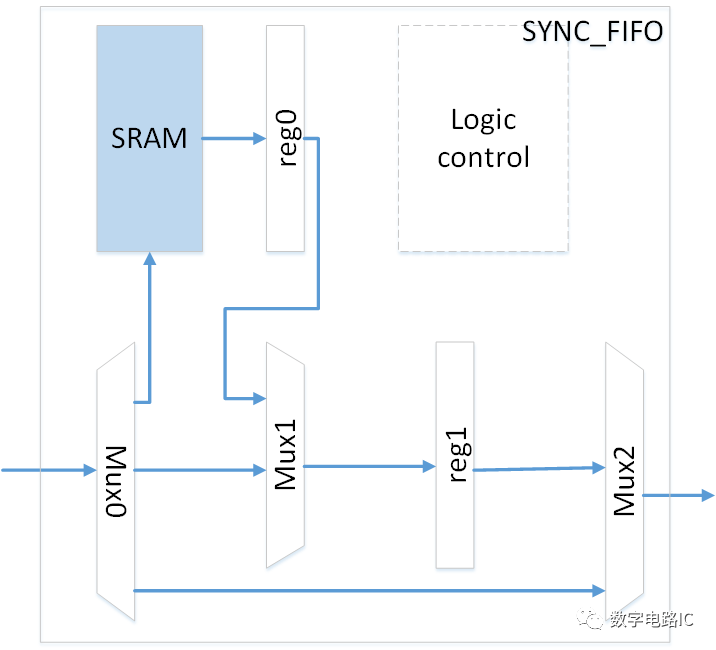

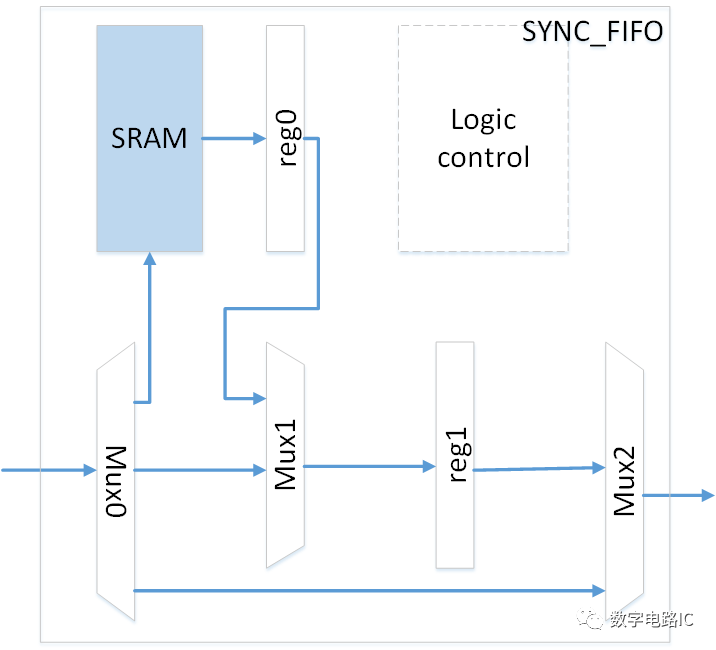

按照正常的思路,在前文完成前向時(shí)序優(yōu)化和后向時(shí)序優(yōu)化后,后面緊跟的應(yīng)該是雙向時(shí)序優(yōu)化策略了,不過(guò)不急,需要先實(shí)現(xiàn)一下握手型同步FIFO。

2023-12-04 14:03:49 1473

1473

FIFO是一種先進(jìn)先出數(shù)據(jù)緩存器,它與普通存儲(chǔ)器的區(qū)別是沒(méi)有外部讀寫(xiě)地址線,使用起來(lái)非常簡(jiǎn)單,缺點(diǎn)是只能順序讀寫(xiě),而不能隨機(jī)讀寫(xiě)。

2024-04-09 14:23:15 4603

4603

AXI接口FIFO是從Native接口FIFO派生而來(lái)的。AXI內(nèi)存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應(yīng)用外,AXI FIFO還可以用于AXI系統(tǒng)總線和點(diǎn)對(duì)點(diǎn)高速應(yīng)用。

2025-03-17 10:31:11 1914

1914

Verilog數(shù)字系統(tǒng)設(shè)計(jì)十二復(fù)雜數(shù)字電路設(shè)計(jì)2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計(jì)十二前言一、什么是FIFO控制器?二、編程1.要求:2.設(shè)計(jì)思路:3.FIFO控制器實(shí)現(xiàn):總結(jié)前言隨著人工智能

2022-02-09 07:23:50

我從黑金《verilog那些事兒,建模篇》5.5章節(jié)copy了程序又加入了網(wǎng)上找的fifo程序加以調(diào)用,結(jié)果串口調(diào)試助手需要發(fā)30個(gè)數(shù)才能收到發(fā)送的數(shù)據(jù),這是怎么回事?(FIFO深度是16啊)程序在附件中(vivado編譯),請(qǐng)求幫助

2016-08-10 21:01:45

我想問(wèn)一下什么情況下需要用異步FIFO,什么情況下用同步FIFO?

2014-11-03 17:19:54

Verilog教程-郝旭帥團(tuán)隊(duì) FIFO(first input first output或者first in first out),先入先出隊(duì)列,是一種數(shù)字電路中常用的緩沖器,先進(jìn)入的數(shù)據(jù)或者命令會(huì)

2023-03-15 16:19:35

UltraEdit支持Verilog和VHDL高亮顯示的方法加入verilog.uew文件。

2012-08-15 14:42:35

本帖最后由 630183258 于 2016-11-7 10:47 編輯

1、原理圖管腳定義:fifo_in輸入數(shù)據(jù)fifo_out輸出數(shù)據(jù)write寫(xiě)使能信號(hào),高電平有效fifo_full寫(xiě)

2016-11-07 00:18:04

跨時(shí)鐘域處理 & 亞穩(wěn)態(tài)處理&異步FIFO1.FIFO概述FIFO: 一、先入先出隊(duì)列(First Input First Output,FIFO)這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)

2022-02-16 06:55:41

異步fifo是用于跨時(shí)域時(shí)鐘傳輸?shù)模?b class="flag-6" style="color: red">同步fifo做緩存我就不是很理解了,到底這個(gè)緩存是什么意思,這樣一進(jìn)一出,不是數(shù)據(jù)的傳輸嗎,為什么加個(gè)fifo,還有,如果是兩組視頻流傳輸,在切換的過(guò)程中如何能保證無(wú)縫切換?希望哪位好心人幫我解答一下

2013-08-27 19:23:36

在FX3同步Slave FIFO的非突發(fā)傳輸中,F(xiàn)PGA在將SLRD拉低后,等兩個(gè)時(shí)鐘周期,然后采樣數(shù)據(jù)總線,采樣數(shù)據(jù)總線前要判斷對(duì)應(yīng)地址的FLAG是否為高,只有為高才采樣數(shù)據(jù)總線,請(qǐng)問(wèn)是這樣

2024-05-31 06:28:07

這是網(wǎng)上比較流行的一個(gè)異步fifo方案,但是fifo的空滿(mǎn)判斷不是應(yīng)該是立即的嗎,加上同步器之后變成寫(xiě)指針要延時(shí)兩個(gè)讀周期再去個(gè)讀指針做空比較,而讀指針要延時(shí)兩個(gè)寫(xiě)周期再去和寫(xiě)指針做滿(mǎn)比較,這樣雖然可以避免亞穩(wěn)態(tài)之類(lèi)的問(wèn)題,可是這個(gè)延時(shí)對(duì)總體的空滿(mǎn)判斷沒(méi)有影響嗎,如果沒(méi)有影響是怎么做到的呢,求解

2016-07-24 16:25:33

垂直投影進(jìn)行研究。二、方案基于Verilog的垂直投影的實(shí)現(xiàn),考慮使用雙口ram、fifo/shfit_rams 實(shí)現(xiàn),但是使用ram實(shí)現(xiàn)時(shí),由于要操作地址,控制邏輯復(fù)雜,而且在寫(xiě)回時(shí)消耗的拍數(shù)比較

2019-03-03 17:51:01

您好!我讀了AN694.4.PDF的數(shù)據(jù)表。在同步從屬FIFO寫(xiě)序列中,如果必須使用部分標(biāo)志以不丟失數(shù)據(jù),則從SLWRγ到標(biāo)記有3個(gè)周期延遲。如何用GPIF設(shè)計(jì)器修改代碼?謝謝! 以上來(lái)自于百度

2019-04-10 14:32:05

如圖所示的異步FIFO,個(gè)人覺(jué)得在讀寫(xiě)時(shí)鐘同步時(shí)會(huì)產(chǎn)生兩個(gè)時(shí)鐘周期的延時(shí),如果讀寫(xiě)時(shí)鐘頻率相差不大,某一時(shí)刻讀寫(xiě)指針相等,當(dāng)寫(xiě)指針同步到讀模塊時(shí)會(huì)產(chǎn)生延時(shí),實(shí)際同步到讀模塊的寫(xiě)指針是兩個(gè)時(shí)鐘周期之前的,這樣就不會(huì)產(chǎn)生空滿(mǎn)信號(hào),要兩個(gè)周期之后才能產(chǎn)生空滿(mǎn)信號(hào),結(jié)果是寫(xiě)溢出或讀空

2015-08-29 18:30:49

我自己寫(xiě)了一個(gè)FIFO,但是我總是不理解Paper中講的要把讀寫(xiě)指針同步,如果我將兩個(gè)不同時(shí)鐘產(chǎn)生的讀寫(xiě)地址直接比較,產(chǎn)生讀寫(xiě),請(qǐng)問(wèn)這個(gè)亞穩(wěn)態(tài)是怎么產(chǎn)生的,不要復(fù)制網(wǎng)上的那些東西,我都看了買(mǎi)就是不太

2016-04-11 23:13:45

XINLINX FPGA與CY7C68013通訊,異步slave fifo通訊方式,PKTEND信號(hào)的作用是什么,不用的話(huà)是不是應(yīng)該拉高 ,另外由于fifo adr用的都公用地址線,時(shí)序上怎么選擇,誰(shuí)能共享一下verilog HDL的例子。

2015-07-10 15:17:28

v2,SyncEth,ToP,TDM時(shí)鐘同步等,以滿(mǎn)足無(wú)線設(shè)備和傳輸設(shè)備的時(shí)鐘同步和傳輸需求。微波時(shí)鐘同步組網(wǎng)針對(duì)微波自身特點(diǎn),將對(duì)目前常用的幾種同步方法進(jìn)行簡(jiǎn)要介紹,以加深時(shí)鐘同步的認(rèn)識(shí)度。

2019-07-12 07:46:39

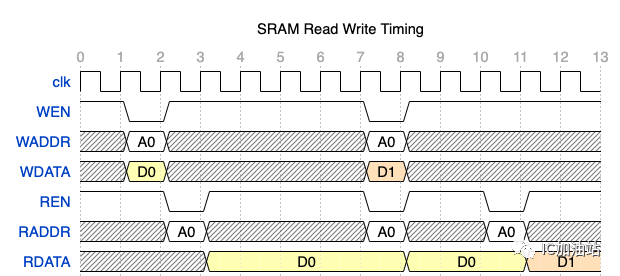

現(xiàn)有4路fifo數(shù)據(jù),要時(shí)分復(fù)用的存入SRAM里,請(qǐng)問(wèn)用verilog怎么寫(xiě)啊???新手,求賜教!!!

2012-10-27 13:28:17

各位大神,有沒(méi)有用過(guò)AXIStream-FIFO IP core的或不用core直接用verilog實(shí)現(xiàn)過(guò)AXIStream-FIFO功能的,我現(xiàn)在FPGA入門(mén)練習(xí)(據(jù)說(shuō)華為等大公司喜歡考這種

2014-02-21 16:24:45

本文針對(duì)該問(wèn)題給出了逐次比較、基于FIFO隊(duì)列和基于狀態(tài)機(jī)的3種幀同步方法。通過(guò)測(cè)試、分析和比較得出,基于有限狀態(tài)機(jī)的方法是嵌入式系統(tǒng)串口通信中很有效的幀同步方法,同時(shí)也是一種很不錯(cuò)的串口通信程序設(shè)計(jì)結(jié)構(gòu)。

2021-05-27 06:52:49

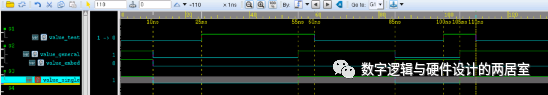

急需同步FIFO,我這有一個(gè),但是仿真圖不對(duì),我也不知道是不是代碼有問(wèn)題。

2015-03-15 09:25:06

,何必要眼巴巴的看FIFO的狀態(tài),你能接收了我才趕緊給準(zhǔn)備一個(gè)呢(當(dāng)真是慣的)~而上面的這種思想,和軟件中的“同步讀寫(xiě)”思路是很相像的,均伴隨著阻塞的概念。而別忘記,在邏輯設(shè)計(jì)中由于時(shí)序的概念,天然

2022-06-30 15:28:00

Applications often require FIFO buffers deeper than those offered by discrete devices. By depth

2009-05-25 14:29:36 20

20 1.什么是FIFO?FIFO是英文First In First Out 的縮寫(xiě),是一種先進(jìn)先出的數(shù)

2009-07-22 16:00:48 0

0 系統(tǒng)在上電復(fù)位時(shí),SPI工作在標(biāo)準(zhǔn)SPI模式,禁止FIFO功能。FIFO的寄存器SPIFFTX、SPIFFRX和SPIFFCT不起作用。通過(guò)將SPIFFTX寄存器中的SPIFFEN的位置為1,使能FIFO模式。SPIRST能在操作的任一階

2009-09-29 10:38:26 33

33 設(shè)計(jì)一個(gè)FIFO是ASIC設(shè)計(jì)者遇到的最普遍的問(wèn)題之一。本文著重介紹怎樣設(shè)計(jì)FIFO——這是一個(gè)看似簡(jiǎn)單卻很復(fù)雜的任務(wù)。一開(kāi)始,要注意,FIFO通常用于時(shí)鐘域的過(guò)渡,是雙時(shí)鐘設(shè)計(jì)

2009-10-15 08:44:35 94

94 Verilog HDL 華為入門(mén)教程

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能

2010-02-11 08:35:38 141

141 Verilog HDL入門(mén)教程(華為絕密資料)

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的

2010-04-02 11:52:21 0

0 給出了一個(gè)利用格雷碼對(duì)地址編碼的羿步FIFO 的實(shí)現(xiàn)方法,并給出了VHDL 程序,以解決異步讀寫(xiě)時(shí)鐘引起的問(wèn)題。

2010-07-16 15:15:42 26

26 設(shè)計(jì)工程師通常在FPGA上實(shí)現(xiàn)FIFO(先進(jìn)先出寄存器)的時(shí)候,都會(huì)使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對(duì)性變差,某些情況下會(huì)變得不方便或者將增加硬

2010-10-27 15:40:30 38

38 摘要:使用FIFO同步源自不同時(shí)鐘域的數(shù)據(jù)是在數(shù)字IC設(shè)計(jì)中經(jīng)常使用的方法,設(shè)計(jì)功能正確的FUFO會(huì)遇到很多問(wèn)題,探討了兩種不同的異步FIFO的設(shè)計(jì)思路。兩種思路

2006-03-24 12:58:33 1663

1663

什么是fifo (First Input First Output,先入先出隊(duì)列)這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。1.什么是FIFO

2007-12-20 13:51:59 13167

13167 什么是FID/FIFO/FFT

FID: (FID:Frequency identify,頻率鑒別號(hào)碼)奔騰III通過(guò)ID號(hào)來(lái)檢查CPU頻率的方法,能夠有效防止Remark。

&n

2010-02-04 11:53:32 1058

1058 本文采用VHDL描述語(yǔ)言,充分利用Xilinx公司Spartan II FPGA的系統(tǒng)資源,設(shè)計(jì)實(shí)現(xiàn)了一種非對(duì)稱(chēng)同步FIFO,它不僅提供數(shù)據(jù)緩沖,而且能進(jìn)行數(shù)據(jù)總線寬度的轉(zhuǎn)換。

2011-01-13 11:33:43 2240

2240 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來(lái)的數(shù)據(jù)不連續(xù)問(wèn)題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理,提出了一種設(shè)定 FIFO 深度的方法。對(duì)FIFO不同深度的實(shí)驗(yàn)表明,采

2011-09-26 13:45:17 7987

7987

本文討論了如何在Windows CE.net平臺(tái)上開(kāi)發(fā)基于FIFO的數(shù)據(jù)采集板的驅(qū)動(dòng)程序,以保證數(shù)據(jù)采集數(shù)據(jù)的準(zhǔn)確性。通過(guò)試驗(yàn)將常規(guī)方法與FIFO進(jìn)行比較,得到較好的結(jié)果

2012-04-16 16:37:15 1388

1388

本文簡(jiǎn)單介紹在使用Verilog HDL語(yǔ)言時(shí)文件的調(diào)用問(wèn)題之include使用方法介紹及舉例說(shuō)明,詳見(jiàn)本文...

2013-01-24 14:40:42 7391

7391

verilog verilog verilog verilog verilog verilog verilog verilog

2015-11-12 14:43:51 0

0 最經(jīng)典的FIFO原理,詳細(xì)講述了FIFO的原理,適合入門(mén)新手,仔細(xì)分析閱讀,也適合高手查閱。

2016-05-03 15:15:08 0

0 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2016-07-15 15:27:00 0

0 FIFO 很重要,之前參加的各類(lèi)電子公司的邏輯設(shè)計(jì)的筆試幾乎都會(huì)考到。

2017-02-11 06:51:50 5203

5203

傳輸時(shí)發(fā)生數(shù)據(jù)丟失問(wèn)題得目的,提出采用異步FIFO來(lái)緩存大量導(dǎo)航電文數(shù)據(jù)還有同步器來(lái)同步所傳輸?shù)妮d波控制字和偽碼控制字的方法。通過(guò)采用Altera公司的FIFO內(nèi)核來(lái)進(jìn)行外圍接口信號(hào)和控制邏輯設(shè)計(jì)以及兩級(jí)觸發(fā)器級(jí)聯(lián)來(lái)實(shí)現(xiàn)同步器的試驗(yàn)設(shè)計(jì)方法,得到所設(shè)計(jì)的緩存

2017-11-06 16:35:27 10

10 (每個(gè)數(shù)據(jù)的位寬) FIFO有同步和異步兩種,同步即讀寫(xiě)時(shí)鐘相同,異步即讀寫(xiě)時(shí)鐘不相同 同步FIFO用的少,可以作為數(shù)據(jù)緩存 異步FIFO可以解決跨時(shí)鐘域的問(wèn)題,在應(yīng)用時(shí)需根據(jù)實(shí)際情況考慮好fifo深度即可 本次要設(shè)計(jì)一個(gè)異步FIFO,深度為8,位寬也是8。

2017-11-15 12:52:41 9176

9176

在現(xiàn)代電路設(shè)計(jì)中,一個(gè)系統(tǒng)往往包含了多個(gè)時(shí)鐘,如何在異步時(shí)鐘間傳遞數(shù)據(jù)成為一個(gè)很重要的問(wèn)題,而使用異步FIFO可以有效地解決這個(gè)問(wèn)題。異步FIFO是一種在電子系統(tǒng)中得到廣泛應(yīng)用的器件,文中介紹了一種基于FPGA的異步FIFO設(shè)計(jì)方法。使用這種方法可以設(shè)計(jì)出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 8860

8860

上集成的高速FIFO實(shí)現(xiàn)采集數(shù)據(jù)的高速緩存并通過(guò)對(duì)高速FIFO的讀寫(xiě)操作實(shí)現(xiàn)總線同步數(shù)據(jù)傳輸,提高數(shù)據(jù)的傳輸速率。

2018-07-12 09:06:00 6077

6077

本文首先介紹了verilog的概念和發(fā)展歷史,其次介紹了verilog的特征與Verilog的邏輯門(mén)級(jí)描述,最后介紹了Verilog晶體管級(jí)描述與verilog的用途。

2018-05-14 14:22:44 47074

47074

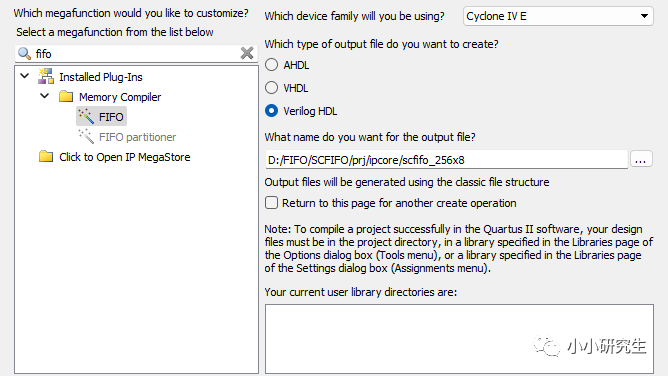

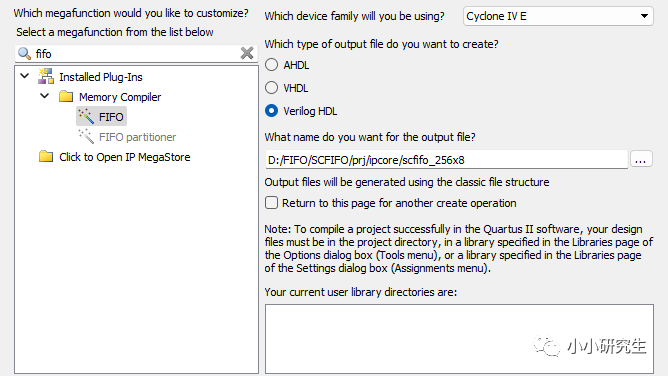

配置FIFO的方法有兩種:

一種是通過(guò)QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中選擇FIFO參數(shù)編輯器來(lái)搭建自己需要的FIFO,這是自動(dòng)生成FIFO的方法

2018-07-20 08:00:00 17

17 異步FIFO廣泛應(yīng)用于計(jì)算機(jī)網(wǎng)絡(luò)工業(yè)中進(jìn)行異步數(shù)據(jù)傳送,這里的異步是指發(fā)送用一種速率而接收用另一速率,因此異步FIFO有兩個(gè)不同的時(shí)鐘,一個(gè)為讀同步時(shí)鐘,一個(gè)為寫(xiě)同步時(shí)鐘。

2019-06-11 08:00:00 3853

3853

FIFO設(shè)計(jì)。本文提供了一種基于信元的FIFO設(shè)計(jì)方法以供設(shè)計(jì)者在適當(dāng)?shù)臅r(shí)候選用。這種方法也適合于不定長(zhǎng)包的處理。

2018-11-28 08:10:00 8891

8891

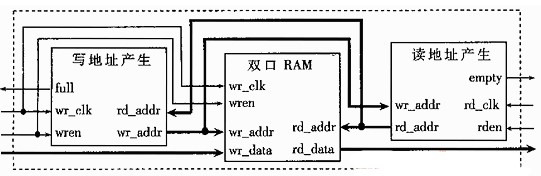

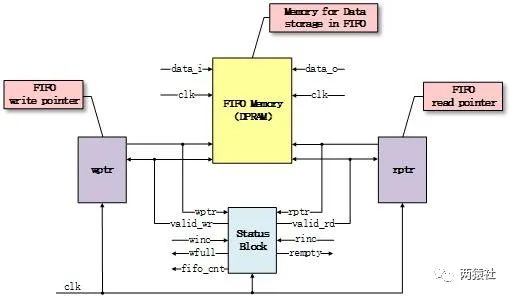

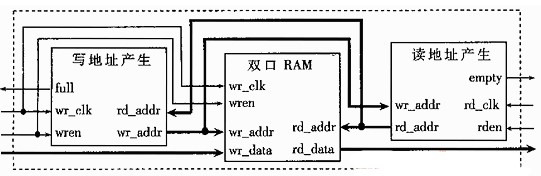

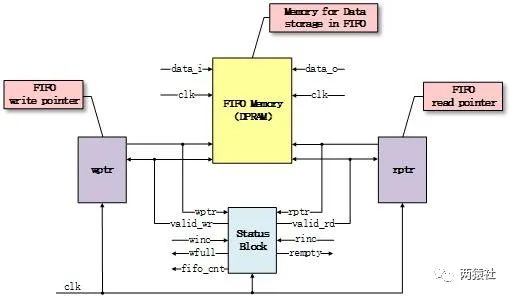

FIFO (先進(jìn)先出隊(duì)列)是一種在電子系統(tǒng)得到廣泛應(yīng)用的器件,通常用于數(shù)據(jù)的緩存和用于容納異步信號(hào)的頻率或相位的差異。FIFO的實(shí)現(xiàn)通常是利用雙口RAM和讀寫(xiě)地址產(chǎn)生模塊來(lái)實(shí)現(xiàn)的。FIFO的接口

2019-08-02 08:10:00 2872

2872

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來(lái)的數(shù)據(jù)不連續(xù)問(wèn)題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理,提出了一種設(shè)定FIFO深度的方法。對(duì)FIFO

2019-01-04 14:25:07 5203

5203

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL 設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2019-02-11 08:00:00 102

102 根據(jù)FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫(xiě)時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來(lái)臨時(shí)同時(shí)發(fā)生讀寫(xiě)操作。異步FIFO是指讀寫(xiě)時(shí)鐘不一致,讀寫(xiě)時(shí)鐘是互相獨(dú)立的。

2019-11-29 07:08:00 2265

2265 wire 和reg是Verilog程序里的常見(jiàn)的兩種變量類(lèi)型,他們都是構(gòu)成verilog程序邏輯最基本的元素。正確掌握兩者的使用方法是寫(xiě)好verilog程序的前提。

2020-03-08 17:18:00 12900

12900 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog教程之Verilog HDL數(shù)字集成電路設(shè)計(jì)方法和基礎(chǔ)知識(shí)課件

2020-12-09 11:24:19 53

53 1.定義 FIFO是英文First In First Out 的縮寫(xiě),是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲(chǔ)器的區(qū)別是沒(méi)有外部讀寫(xiě)地址線,這樣使用起來(lái)非常簡(jiǎn)單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序

2021-04-09 17:31:42 6216

6216

異步FIFO通過(guò)比較讀寫(xiě)地址進(jìn)行滿(mǎn)空判斷,但是讀寫(xiě)地址屬于不同的時(shí)鐘域,所以在比較之前需要先將讀寫(xiě)地址進(jìn)行同步處理,將寫(xiě)地址同步到讀時(shí)鐘域再和讀地址比較進(jìn)行FIFO空狀態(tài)判斷(同步后的寫(xiě)地址一定

2021-08-04 14:05:21 5131

5131 Verilog數(shù)字系統(tǒng)設(shè)計(jì)十二復(fù)雜數(shù)字電路設(shè)計(jì)2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計(jì)十二前言一、什么是FIFO控制器?二、編程1.要求:2.設(shè)計(jì)思路:3.FIFO控制器實(shí)現(xiàn):總結(jié)前言 隨著人工智能

2021-12-05 15:51:04 9

9 跨時(shí)鐘域處理 & 亞穩(wěn)態(tài)處理&異步FIFO1.FIFO概述FIFO: 一、先入先出隊(duì)列(First Input First Output,FIFO)這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)

2021-12-17 18:29:31 10

10 由于平時(shí)我們工作中,FIFO都是直接調(diào)用IP核,對(duì)于FIFO深度選擇并沒(méi)有很在意,而在筆試面試過(guò)程中,經(jīng)常被問(wèn)及的問(wèn)題之一就是如何計(jì)算FIFO深度。

2022-07-03 17:25:28 3564

3564 寫(xiě)代碼是給別人和多年后的自己看的。 關(guān)于Verilog代碼設(shè)計(jì)的一些風(fēng)格和方法之前也寫(xiě)過(guò)一些Verilog有什么奇技淫巧?

2022-10-24 15:23:54 2310

2310 FIFO的分類(lèi)根均FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫(xiě)時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來(lái)臨時(shí)同時(shí)發(fā)生讀寫(xiě)操作。異步FIFO是指讀寫(xiě)時(shí)鐘不一致,讀寫(xiě)時(shí)鐘是互相獨(dú)立的。

2022-11-01 09:57:08 2859

2859 同步FIFO的意思是說(shuō)FIFO的讀寫(xiě)時(shí)鐘是同一個(gè)時(shí)鐘,不同于異步FIFO,異步FIFO的讀寫(xiě)時(shí)鐘是完全異步的。同步FIFO的對(duì)外接口包括時(shí)鐘,清零,讀請(qǐng)求,寫(xiě)請(qǐng)求,數(shù)據(jù)輸入總線,數(shù)據(jù)輸出總線,空以及滿(mǎn)信號(hào)。

2022-11-01 09:58:16 2461

2461 FIFO 是我們?cè)O(shè)計(jì)中常用的工具,因?yàn)樗鼈兪刮覀兡軌蛟谶M(jìn)行信號(hào)和圖像處理時(shí)緩沖數(shù)據(jù)。我們還使用異步FIFO來(lái)處理數(shù)據(jù)總線的時(shí)鐘域交叉問(wèn)題。

2022-11-04 09:14:11 6431

6431 和寫(xiě)入數(shù)據(jù)(對(duì)于大型數(shù)據(jù)存儲(chǔ),在性能上必然緩慢),其數(shù)據(jù)地址是由內(nèi)部讀寫(xiě)指針自動(dòng)加一完成的,不能像普通的存儲(chǔ)器一樣,由地址線決定讀取或者寫(xiě)入某個(gè)特定地址的數(shù)據(jù),按讀寫(xiě)是否為相同時(shí)鐘域分為同步和異步FIFO,這里主要介紹異步FIFO,主要用于跨時(shí)鐘域傳輸數(shù)據(jù)。 FIFO是

2022-12-12 14:17:41 5421

5421 FIFO用于為匹配讀寫(xiě)速度而設(shè)置的數(shù)據(jù)緩沖buffer,當(dāng)讀寫(xiě)時(shí)鐘異步時(shí),就是異步FIFO。多bit的數(shù)據(jù)信號(hào),并不是直接從寫(xiě)時(shí)鐘域同步到讀時(shí)鐘域的。

2023-01-01 16:48:00 1858

1858 的verilog異步fifo設(shè)計(jì),仿真(代碼供參考)異步fifo適合處理不同時(shí)鐘域之間傳輸?shù)臄?shù)據(jù)組,但有時(shí)不同時(shí)鐘域之間僅僅傳遞脈沖,異步fifo就顯的有點(diǎn)大材小用的,因此單信號(hào)的跨時(shí)鐘域處理通常有, ? ? ? ? 兩級(jí)寄存器串聯(lián)。 ? ? ? ? 脈沖同步器。

2023-02-17 11:10:08 1588

1588 FIFO(First In First Out )先入先出存儲(chǔ)器,在FPG設(shè)計(jì)中常用于跨時(shí)鐘域的處理,FIFO可簡(jiǎn)單分為同步FIFO和異步FIFO。

2023-04-25 15:55:28 5975

5975

今天咱們開(kāi)始聊聊FIFO的設(shè)計(jì)。FIFO是一個(gè)數(shù)字電路中常見(jiàn)的模塊,主要作用是數(shù)據(jù)產(chǎn)生端和接受端在短期內(nèi)速率不匹配時(shí)作為數(shù)據(jù)緩存。FIFO是指First In, First Out,即先進(jìn)先出,跟大家排隊(duì)一樣。越早排隊(duì)的人排在越前面,輪到他的次序也越早,所以FIFO有些時(shí)候也被稱(chēng)為隊(duì)列queue。

2023-05-04 15:48:20 1504

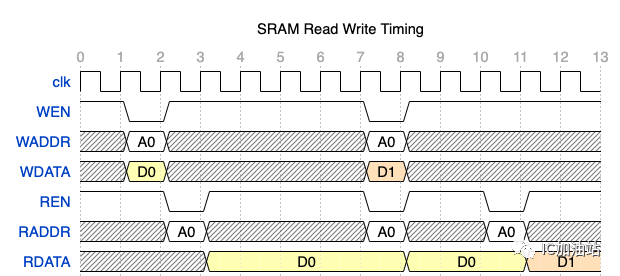

1504 開(kāi)始往下讀之前,老李先問(wèn)一個(gè)問(wèn)題,假如現(xiàn)在讓你設(shè)計(jì)一個(gè)深度為N的基于2port SRAM的同步FIFO,請(qǐng)問(wèn)至少需要多大的SRAM? 假設(shè)SRAM的位寬就是你的數(shù)據(jù)寬度,那么問(wèn)題就是問(wèn)你需要的SRAM的行數(shù)至少是多少?如果你覺(jué)得答案是顯而易見(jiàn)的N,那么你值得讀完這一篇。

2023-05-04 15:55:49 1705

1705

FIFO是異步數(shù)據(jù)傳輸時(shí)常用的存儲(chǔ)器,多bit數(shù)據(jù)異步傳輸時(shí),無(wú)論是從快時(shí)鐘域到慢時(shí)鐘域,還是從慢時(shí)鐘域到快時(shí)鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 2243

2243

異步FIFO主要由五部分組成:寫(xiě)控制端、讀控制端、FIFO Memory和兩個(gè)時(shí)鐘同步端

2023-05-26 16:17:20 2201

2201

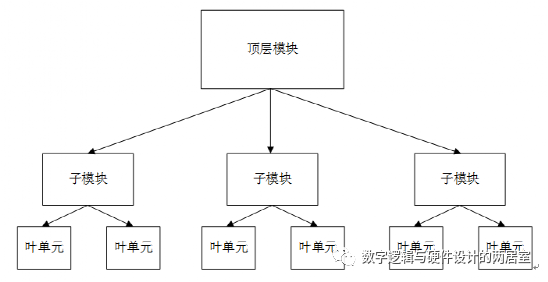

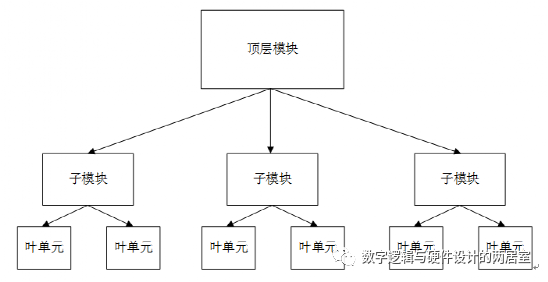

Verilog 的設(shè)計(jì)多采用自上而下的設(shè)計(jì)方法(top-down)。即先定義頂層模塊功能,進(jìn)而分析要構(gòu)成頂層模塊的必要子模塊;

2023-05-29 15:44:24 2145

2145

Verilog 提供了 2 大類(lèi)時(shí)序控制方法:時(shí)延控制和事件控制。事件控制主要分為邊沿觸發(fā)事件控制與電平敏感事件控制。

2023-06-02 11:44:05 1664

1664

FIFO,F(xiàn)irst In First Out,先入先出隊(duì)列,顧名思義,即第一個(gè)到達(dá)的數(shù)據(jù)也將會(huì)是第一個(gè)離開(kāi)。

2023-06-05 14:39:33 1600

1600

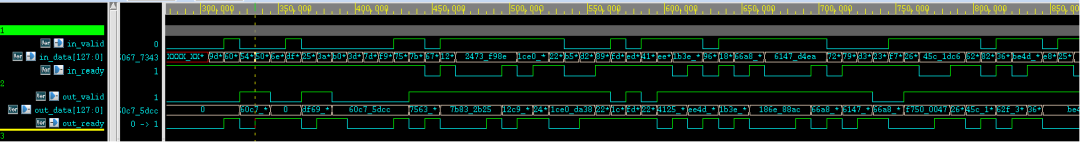

FIFO 是FPGA設(shè)計(jì)中最有用的模塊之一。FIFO 在模塊之間提供簡(jiǎn)單的握手和同步機(jī)制,是設(shè)計(jì)人員將數(shù)據(jù)從一個(gè)模塊傳輸?shù)搅硪粋€(gè)模塊的常用選擇。

2023-06-14 08:59:29 769

769 ? FIFO 是FPGA設(shè)計(jì)中最有用的模塊之一。FIFO 在模塊之間提供簡(jiǎn)單的握手和同步機(jī)制,是設(shè)計(jì)人員將數(shù)據(jù)從一個(gè)模塊傳輸?shù)搅硪粋€(gè)模塊的常用選擇。 在這篇文章中,展示了一個(gè)簡(jiǎn)單的 RTL 同步

2023-06-14 09:02:19 1415

1415 FIFO(First In First Out, 先入先出 ),是一種數(shù)據(jù)緩沖器,用來(lái)實(shí)現(xiàn)數(shù)據(jù)先入先出的讀寫(xiě)方式。數(shù)據(jù)按順序?qū)懭?FIFO,先被寫(xiě)入的數(shù)據(jù)同樣在讀取的時(shí)候先被讀出,所以 FIFO存儲(chǔ)器沒(méi)有地址線,有一個(gè)寫(xiě)端口和一個(gè)讀端口。

2023-09-07 18:30:11 6578

6578

模塊雖小但是要有新意,首先寫(xiě)一個(gè)同步FIFO,這是一個(gè)爛大街的入門(mén)級(jí)項(xiàng)目,但是我肯定不會(huì)寫(xiě)的那么簡(jiǎn)單

2023-09-11 17:11:07 1212

1212

單片機(jī)自定義協(xié)議FIFO高效發(fā)送數(shù)據(jù)方法

2023-09-28 17:32:56 1422

1422

為什么異步fifo中讀地址同步在寫(xiě)時(shí)鐘域時(shí)序分析不通過(guò)? 異步FIFO中讀地址同步在寫(xiě)時(shí)鐘域時(shí)序分析不通過(guò)的原因可能有以下幾個(gè)方面: 1. 讀地址同步在寫(xiě)時(shí)鐘域時(shí)序分析未覆蓋完全 在時(shí)序分析時(shí),可能

2023-10-18 15:23:55 1422

1422 同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO各在什么情況下應(yīng)用? 1. 同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO在處理時(shí)序有明顯的區(qū)別。同步FIFO相對(duì)來(lái)說(shuō)是較為

2023-10-18 15:23:58 2603

2603 Verilog是一種硬件描述語(yǔ)言,用于設(shè)計(jì)和模擬數(shù)字電路。在Verilog中,同步和異步是用來(lái)描述數(shù)據(jù)傳輸和信號(hào)處理的兩種不同方式,而阻塞賦值和非阻塞賦值是兩種不同的賦值方式。本文將詳細(xì)解釋

2024-02-22 15:33:04 2897

2897 1. FIFO簡(jiǎn)介 FIFO是一種先進(jìn)先出數(shù)據(jù)緩存器,它與普通存儲(chǔ)器的區(qū)別是沒(méi)有外部讀寫(xiě)地址線,使用起來(lái)非常簡(jiǎn)單,缺點(diǎn)是只能順序讀寫(xiě),而不能隨機(jī)讀寫(xiě)。 2. 使用場(chǎng)景 數(shù)據(jù)緩沖:也就是數(shù)據(jù)寫(xiě)入過(guò)快

2024-06-04 14:27:37 3489

3489

本文繼續(xù)介紹Verilog HDL基礎(chǔ)知識(shí),重點(diǎn)介紹賦值語(yǔ)句、阻塞與非阻塞、循環(huán)語(yǔ)句、同步與異步、函數(shù)與任務(wù)語(yǔ)法知識(shí)。

2024-10-24 15:00:35 1792

1792

介紹幾種自動(dòng)生成verilog代碼的方法。

2024-11-05 11:45:43 1678

1678

Verilog測(cè)試平臺(tái)設(shè)計(jì)方法是Verilog FPGA開(kāi)發(fā)中的重要環(huán)節(jié),它用于驗(yàn)證Verilog設(shè)計(jì)的正確性和性能。以下是一個(gè)詳細(xì)的Verilog測(cè)試平臺(tái)設(shè)計(jì)方法及Verilog FPGA開(kāi)發(fā)

2024-12-17 09:50:06 1631

1631 前言:TSMaster目前有兩種讀取報(bào)文的模式:回調(diào)函數(shù)模式和fifo模式。fifo函數(shù)是TSMaster近期新增的函數(shù),本文將重點(diǎn)介紹fifo模塊。關(guān)于回調(diào)函數(shù)的使用方法可以參考幫助模塊的《快速

2025-03-14 20:04:21 1019

1019

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論