【Linux + C語言】話說,你真的了解system接口的調用嗎?

2022-09-12 16:33:38 5356

5356

談談SiC MOSFET的短路能力

2023-08-25 08:16:13 3282

3282

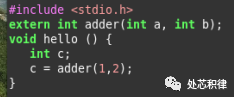

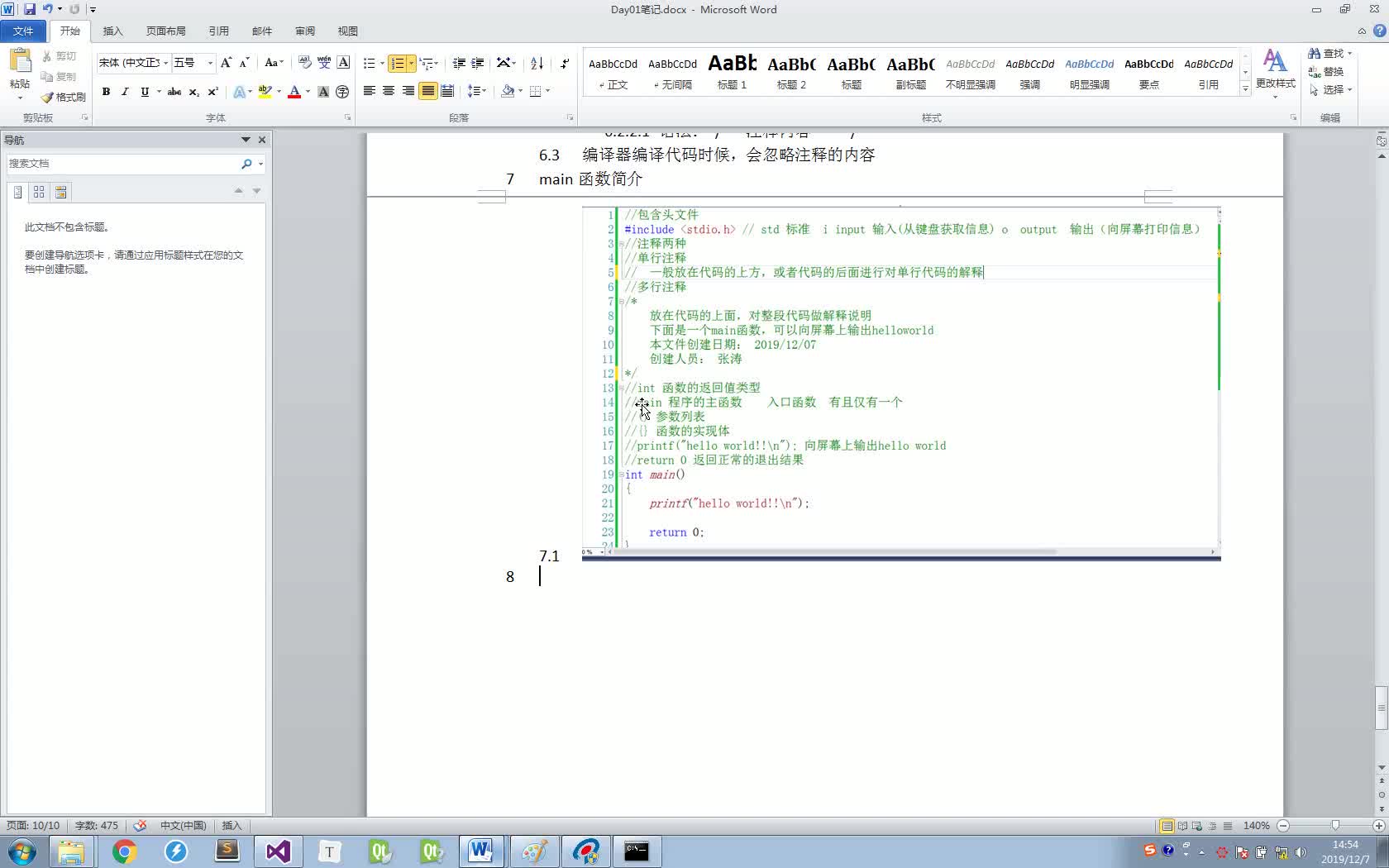

對代碼執行時間要求很嚴格的算法,例如很多個點的FFT、IFFT中,匯編代碼的高效仍然是C/C++所不能替代的。這些就涉及到了C/C++代碼與匯編代碼的接口問題,在此我們就來了解一下它們是如何交互的。首先要遵循以下的九大原則:

2021-02-01 07:12:42

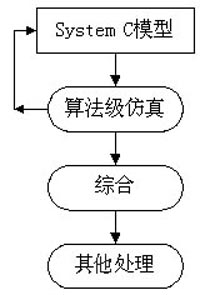

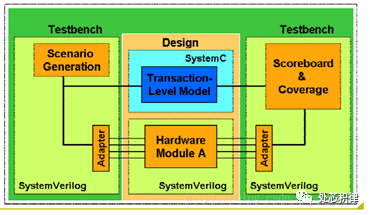

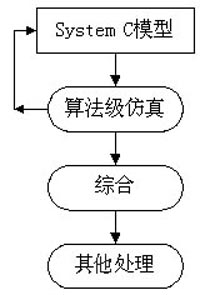

SYSTEM C 是什么?它是怎樣被提出來的?SYSTEM C有哪些顯著的特點?SYSTEM C設計與傳統設計比較,有哪些優點?

2021-04-14 07:10:12

本文討論了一些System Verilog問題以及相關的SystemVerilog 語言參考手冊規范。正確理解這些規格將有助于System Verilog用戶避免意外的模擬結果。

2020-12-11 07:19:58

本文討論了一些System Verilog問題以及相關的SystemVerilog 語言參考手冊規范。正確理解這些規格將有助于System Verilog用戶避免意外的模擬結果。

2020-12-24 07:07:04

Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結構描述

2019-09-06 09:14:16

談談C語言中指針有什么好處,請各位高手們談談自己的體會...

2012-09-01 17:38:47

談談TD-LTE及其測量技術

2021-05-26 06:55:49

談談ZigBee SoC的定位功能

2021-05-25 06:23:42

information:-1.Does itsupport System verilog forverification?2. Code coverage support.3.Assertion support.Whichversionof Modelsim XE supports these feature.

2018-11-27 14:20:41

你能否告訴我,自2014年4月以來Vivado 2016.3中對任何System Verilog功能的支持是否有所改變?你能告訴我這段代碼是否適用于2014.4?interface ibb_if

2020-05-14 08:57:57

翻譯成verilog,在FPGA里面實現,即system generator。altera有沒有類似的接口,與matlab可以互連,直接在matlab里設計我所需要的算法,在翻譯成verilog?

2015-01-14 14:20:50

。Verilog HDL 從 C 語言中繼承了多種操作符和結構。Verilog HDL 提供了擴展的建模能力和擴展模塊。Verilog HDL 語言的核心子集非常易于學習和使用,這對大多數建模應用來說已經足夠

2018-09-18 09:33:31

CO_SIMULATION獲取所有信號。我在SYSTEM C中用verilog HDL和Firmaware編寫了RTL。但我沒有得到任何適用于HW / FW協同仿真的文件。請幫我解決這個問題。謝謝

2020-04-17 10:09:54

這種設計方法與現在常用的設計方法相比有很多優點: 1.精煉的設計方法。使用System C設計系統,系統設計人員不必花費很大的精力將整個系統設計由C語言描述轉換為HDL描述。系統設計人員可以通過在C

2019-07-10 08:14:51

大家好,我試圖在verilog文件中將命令傳遞給系統。 (在最初的開始循環中)我嘗試使用$ system命令行。它現在處于verilog標準,但它似乎不適用于vivado。誰知道怎么做?這是我想要

2020-05-22 15:23:42

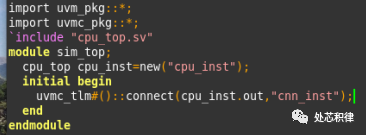

新手學習SystemVerilog & UVM指南 從剛接觸System Verilog以及后來的VMM,OVM,UVM已經有很多年了,隨著電子工業的逐步發展,國內對驗證人才的需求也會急劇

2015-03-11 16:24:35

求大佬分享一些System Verilog的學習經驗

2021-06-21 06:29:54

IEEE Standard Verilog Hardware Description Language

(This introduction is not part of IEEE Std

2008-10-21 15:37:44 0

0 The Verilog language is a hardware description language that provides a means ofspecifying a

2009-02-12 09:33:26 82

82 In-System FLASH Programming with hardwareimplemented bank switching capabilityThe following

2009-04-01 21:42:19 16

16 pcit32 verilog lattice源代碼:The evolution of digital systems over the past two decades has placed new

2009-06-14 08:46:27 29

29 The Mindshare Architecture book series ISA System Architecture,EISA Syseten Architecture,80486

2009-07-17 16:55:47 41

41 The Mindshare Architecture book series includes:ISA System Architecture,EISA System Architecture

2009-07-17 17:36:58 0

0 The Verilog Programming Language Interface, commonly called the Verilog PLI,is one of the more

2009-07-22 09:55:36 0

0 The Verilog Programming Language Interface, commonly called the Verilog PLI,is one of the more

2009-07-22 09:57:33 0

0 This book is on the IEEE Standard Hardware Description Languagebased on the Verilog® Hardware

2009-07-23 08:59:50 0

0 提出了采用Verilog HDL 設計I2C 總線分析器的方法,該I2C 總線分析器支持三種不同的工作模式:被動、主機和從機模式,并提供了嵌入式系統設計接口。通過硬件總體框架分析,分

2009-08-10 15:32:18 40

40 簡述了I2C總線的特點;介紹了開發FPGA時I2C總線模塊的設計思想;給出并解釋了用Verilog HDL實現部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時序圖。

2009-10-19 10:49:16 104

104 談談電路中的“地” 無論是在模擬電路中還是在數字電路

2006-04-16 23:34:00 3114

3114 摘要: 簡述了I2C總線的特點;介紹了開發FPGA時I2C總線模塊的設計思想;給出并解釋了用Verilog HDL實現部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時序圖

2009-06-20 13:17:08 7138

7138

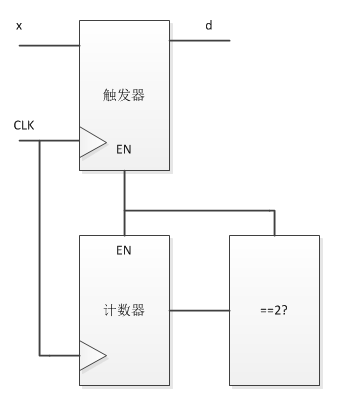

針對C語言編程者的Verilog開發指南實例

本文舉例說明了如何用軟件實現脈寬調制(PWM),如何將該設計轉換成一個可以在FPGA中運行的邏輯塊,并能利用

2009-12-27 13:26:43 1173

1173 什么是C-3/C3 system (Command、Control and Communication System)

英文縮寫: C-3、C3 system (Command、Control and Communication System)

中文譯名:

2010-02-22 10:54:48 1187

1187 一、概述 SYSTEM C 是由 Synospy Inc. 提出的,目前最新的版本為V2.0。它提出的目的就是以一種系統設計的思想進行系統設計。它將軟件算法與硬件實現很好的結合在一起,提

2010-07-19 09:31:47 3259

3259

Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。

2011-01-11 10:45:29 1580

1580 以前在貼Verilog代碼時,都只能挑C++或者C#的語法著色,但兩者的主題詞畢竟不太一樣,透過dudu的幫助,我將Verilog 2001年的主題詞加上了,現在博客園也能漂亮的顯示Verilog代碼了!

2011-05-10 08:25:22 1244

1244 本文簡單討論并總結了VHDL、Verilog,System verilog 這三中語言的各自特點和區別 As the number of enhancements

2012-01-17 11:32:02 0

0 本資料是關于夏宇聞老師優秀的verilog教程課件,其中包括verilog講稿PPT、verilog課件、verilog例題等。

2012-09-27 15:00:49 473

473 verilog verilog verilog verilog verilog verilog verilog verilog

2015-11-12 14:43:51 0

0 基于EP1C3的FPGA程序之seg7_verilog

2016-01-20 15:22:50 11

11 基于EP1C3的進階實驗_reference_verilog

2016-01-21 11:29:32 14

14 基于EP1C3的進階實驗seg7_verilog

2016-10-27 18:20:05 2

2 基于EP1C3的進階實驗eference_verilog

2016-10-27 18:20:05 3

3 基于EP1C3的進階實驗_reference_verilog

2016-11-18 16:05:02 4

4 基于EP1C3的FPGA程序之seg7_verilog

2016-11-18 16:05:02 0

0 《Visual C# 2005開發技術》與用戶交互

2017-02-07 15:17:36 0

0 前一陣一直在忙,所以沒有來得及寫博文。弄完雜七雜八的事情,又繼續FPGA的研究。使用Verilog HDL語言和原理圖輸入來完成FPGA設計的方法都試驗過了,更高級的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8716

8716

基于System Verilog中的隨機化激勵

2017-10-31 09:25:00 9

9 現在的FPGA算法的實現有下面幾種方法: 1. Verilog/VHDL 語言的開發 ; 2. system Generator; 3. ImpulsC 編譯器實現從 C代碼到 HDL 語言; 4.

2017-11-17 14:29:06 8946

8946 Xilinx System Generator 是專門為數字信號算法處理而推出的模型化設計平臺,可以快速、簡單地將DSP系統的抽象算法轉換成可綜合的、可靠的硬件系統,彌補了大部分對C語言以及Matlab工具很熟悉的DSP工程師對于硬件描述語言VHDL和Verilog HDL認識不足的缺陷。

2018-07-19 09:32:00 4453

4453

數據傳遞是比較麻煩的事情。兩者之間數據的傳遞有這樣幾種情況:java和c之間基本數據類型的交互,java向c傳遞對象類型,c向java返回對象類型,c調用java類。

2017-11-27 10:22:58 1974

1974 Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。而C語言是一門通用計算機編程語言,應用廣泛。

2017-12-08 16:43:30 12969

12969 采用System Verilog語言設計了一種具有層次化結構的可重用驗證平臺,該平臺能夠產生各種隨機、定向、錯誤測試向量,并提供功能覆蓋率計算。將驗證平臺在Synopsys公司的VCS仿真工具上運行

2018-01-12 11:28:24 3225

3225

本文首先介紹了verilog的概念和發展歷史,其次介紹了verilog的特征與Verilog的邏輯門級描述,最后介紹了Verilog晶體管級描述與verilog的用途。

2018-05-14 14:22:44 47074

47074

本文檔的主要內容詳細介紹的是Verilog HDL入門教程之Verilog HDL數字系統設計教程。

2018-09-20 15:51:26 86

86 本文檔的主要內容詳細介紹的是Verilog HDL教程之Verilog HDL的命令格式資料說明。

2019-01-09 08:00:00 32

32 Verilog HDL是一種用于數字系統設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結構描述的語言。

2019-03-08 14:29:12 13726

13726 system的原理其實就是調用fork創建子進程去執行shell命令,然后返回最后一條shell命令的狀態值。linux下man system可以看到返回值說明:?1.如果返回值等于

2019-04-02 14:41:05 1450

1450 Verilog與C語言還是存在許多差別。另外,作為一種與普通計算機編程語言不同的硬件描述語言,它還具有一些獨特的語言要素,例如向量形式的線網和寄存器、過程中的非阻塞賦值等。總的來說,具備C語言的設計人員將能夠很快掌握Verilog硬件描述語言。

2019-12-11 07:02:00 2375

2375

本文檔的主要內容詳細介紹的是Verilog教程之Verilog HDL程序設計語句和描述方式。

2020-12-09 11:24:23 53

53 和EDA工具之間交互的C語言例程。(模擬器、波形顯示器)

SDF:標準延遲格式-一個文件,用于向模擬器和其他工具反注釋精確的定時信息。

2021-02-02 16:19:23 9

9 發展歷史 1984年,Verilog開始作為一種專用的硬件建模語言使用,取得了相當大的成功。1990年,Cadence Design Systems公司將該語言面向公眾開放,作為試圖與VHDL相抗衡

2021-06-21 14:46:08 12174

12174 SystemVerilog語言簡介 SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充

2021-09-28 17:12:33 4472

4472 SystemVerilog是一種 硬件描述和驗證語言 (HDVL),它 基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充了C語言數據類型、結構、壓縮

2021-10-19 10:58:05 5218

5218 ,用它可以表示邏輯電路圖、邏輯表達式等數字邏輯功能。特點:verilog很多操作符和結構類似與C語言,比如

2021-11-06 09:05:57 15

15 公眾號自取代碼MSP430的代碼Verilog和VHDL都有,80C51的是Verilog寫的,感興趣的可以下載參考。關注公眾號:AriesOpenFPGA回復:MSP430

2021-11-20 15:06:08 14

14 #ifndef HC32L1XX_LL_SYSTEM_H_#define HC32L1XX_LL_SYSTEM

2021-11-23 18:06:52 9

9 /*! \brief setup the microcontroller system, initialize the system \param[in] none

2021-12-06 10:36:10 7

7 Verilog HDL入門教程-Verilog HDL的基本語法

2022-01-07 09:23:42 189

189 Verilog HDL(Hardware Description Language)是在用途最廣泛的C語言的基礎上發展起來的一種硬件描述語言,具有靈活性高、易學易用等特點。Verilog HDL可以在較短的時間內學習和掌握,目前已經在FPGA開發/IC設計領域占據絕對的領導地位。

2022-09-13 14:34:20 1858

1858 第一句話是:還沒學數電的先學數電。然后你可以選擇verilog或者VHDL,有C語言基礎的,建議選擇VHDL。因為verilog太像C了,很容易混淆,最后你會發現,你花了大量時間去區分這兩種語言,而

2022-11-03 09:02:56 5102

5102 一個掌握Verilog語言的工程師初次看SystemVerilog都會有這樣的感受,這就是Verilog啊,很容易啊,So easy啊。沒錯,確實是這樣,System Verilog的產生

2022-12-09 15:08:05 5582

5582 一個復雜電路系統的完整Verilog HDL模型是由若干個Verilog HDL模塊構成的,每一個模塊又可以由若干個子模塊構成。其中有些模塊需要綜合成具體電路,而有些模塊只是與用戶所設計的模塊有交互聯系的現存電路或激勵信號源。

2023-02-02 10:03:38 12465

12465 fpga學習,verilog學習,verilog經典學習代碼

2023-02-13 09:32:15 23

23 System Verilog(SV)語言的Class本身就帶有“打包”的基因。眾所周知,SV語言的很多特性是派生自C++語言的。

2023-03-15 13:55:25 1417

1417 FPGA需要良好的數電模電基礎,verilog需要良好C語言基礎。

2023-05-11 17:30:07 3320

3320

FPGA需要良好的數電模電基礎,verilog需要良好C語言基礎。

2023-05-22 15:04:29 1434

1434

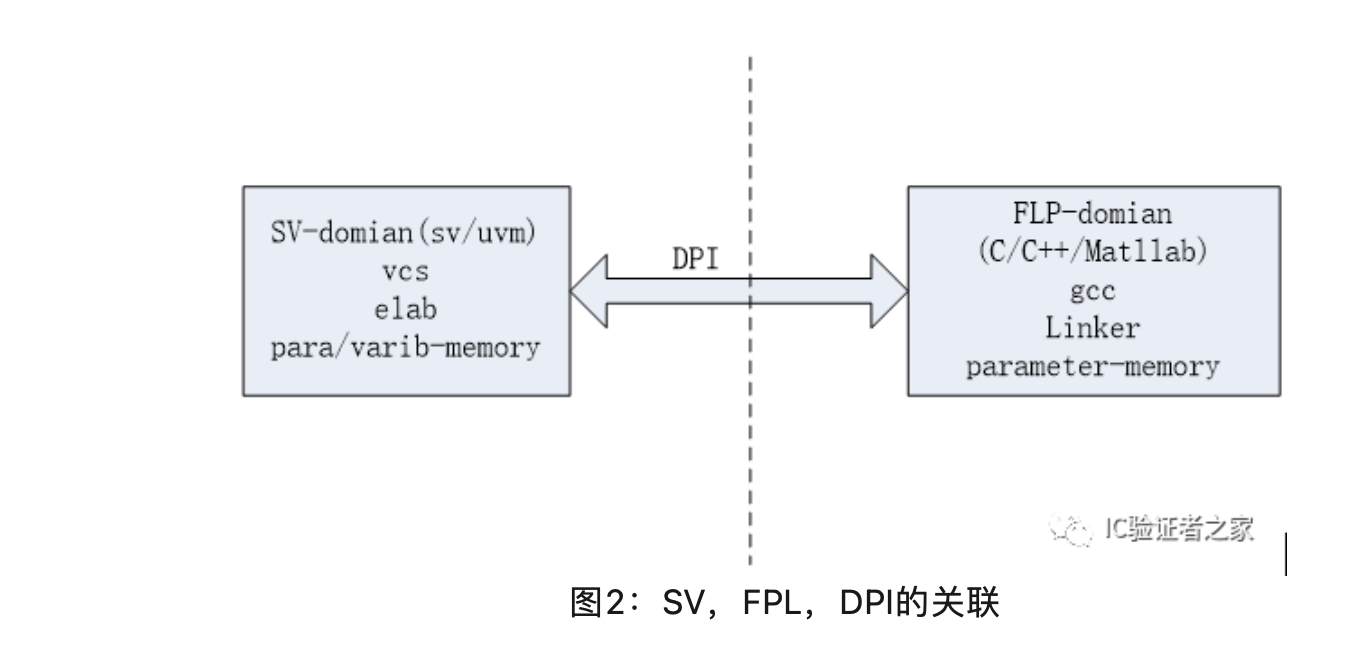

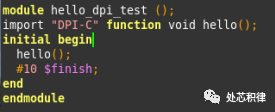

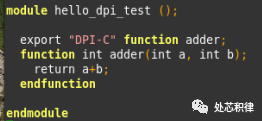

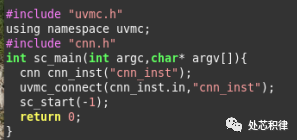

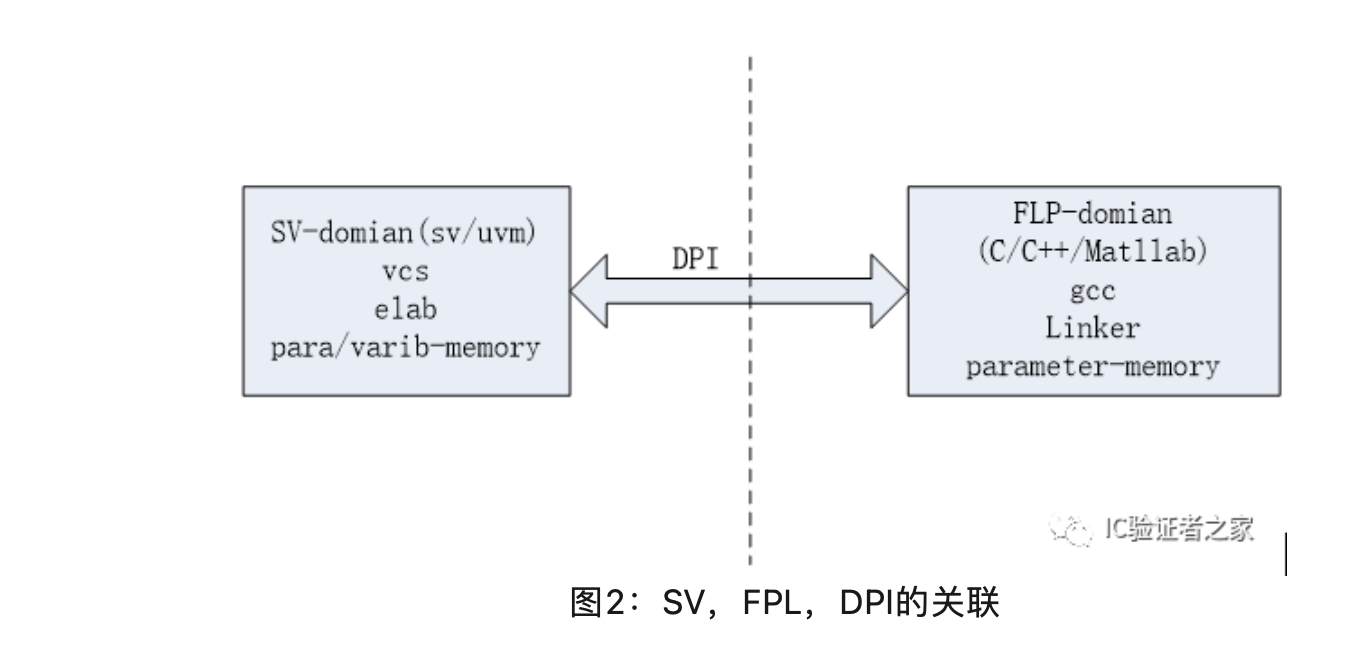

System Verilog(SV)把其他編程語言統一成為外語,Foreign Programming Language(FPL)。

2023-05-23 15:39:00 3529

3529

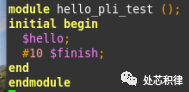

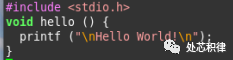

PLI全稱 Program Language Interface,程序員可以通過PLI在verilog中調用C函數,這種訪問是雙向的。

2023-06-01 17:32:22 2625

2625

Verilog模塊之間的連接是通過模塊端口進行的。 為了給組成設計的各個模塊定義端口,我們必須對期望的硬件設計有一個詳細的認識。 不幸的是,在設計的早期,我們很難把握設計的細節。 而且,一旦模塊

2023-06-12 10:05:01 2277

2277 讀者如果學習了verilog,并且有了一定的實踐經驗的話應該強烈的感受到,verilog和軟件(諸如C/C++)有著本質且明顯的差別,是一條不可跨越的鴻溝。

2023-06-28 10:44:32 1111

1111

Verilog大量例程(簡單入門到提高)

2023-08-16 11:49:31 5

5 電子發燒友網為你提供ADI(ADI)DS28C40EVKIT: Evaluation System for the DS28C40 Data Sheet相關產品參數、數據手冊,更有

2023-10-17 19:20:20

Verilog中的模塊端口對應方式,并提供示例代碼和詳細解釋,以幫助讀者更好地理解和應用。 首先,我們來了解一下Verilog中的模塊和模塊端口。一個Verilog模塊被定義為包含一組聲明和語句的代碼塊,類似于C語言中的函數。模塊可以有輸入端口(input)、輸出端口(output)

2024-02-23 10:20:32 3071

3071 FPGA(現場可編程邏輯門陣列)開發主要使用的編程語言是硬件描述語言(HDL),其中Verilog是最常用的編程語言之一。而C語言通常用于傳統的軟件編程,與FPGA的硬件編程有所區別。

2024-03-27 14:38:14 3907

3907 談談 十折交叉驗證訓練模型

2024-05-15 09:30:17 2481

2481 ICer需要System Verilog語言得加成,這是ICer深度的表現。

2024-11-01 10:44:36 0

0 Verilog 與 VHDL 比較 1. 語法和風格 Verilog :Verilog 的語法更接近于 C 語言,對于有 C 語言背景的工程師來說,學習曲線較平緩。它支持結構化編程,代碼更直觀,易于

2024-12-17 09:44:44 2877

2877 Verilog測試平臺設計方法是Verilog FPGA開發中的重要環節,它用于驗證Verilog設計的正確性和性能。以下是一個詳細的Verilog測試平臺設計方法及Verilog FPGA開發

2024-12-17 09:50:06 1631

1631 Verilog與ASIC設計的關系 Verilog作為一種硬件描述語言(HDL),在ASIC設計中扮演著至關重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52:26 1543

1543 ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之間的數據交互是系統設計的核心。

2025-10-15 10:33:19 738

738

電子發燒友App

電子發燒友App

評論