來源:《Verilog數(shù)字系統(tǒng)設(shè)計(jì)(夏宇聞)》 阻塞和非阻塞賦值的語言結(jié)構(gòu)是Verilog 語言中最難理解概念之一。甚至有些很有經(jīng)驗(yàn)的Verilog 設(shè)計(jì)工程師也不能完全正確地理解:何時(shí)使用非阻塞

2021-08-17 16:18:17 7048

7048 今天給大俠帶來的是一周掌握FPGA Verilog HDL 語法,今天開啟第一天,下面咱們廢話就不多說了,一起來看看吧。

2022-07-18 09:47:40 4520

4520 今天給大俠帶來的是一周掌握FPGA Verilog HDL 語法,今天開啟第二天。上一篇提到了整數(shù)型以及參數(shù)型,此篇我們繼續(xù)來看變量以及后續(xù)其他內(nèi)容,結(jié)合實(shí)例理解理論語法,會讓你理解運(yùn)用的更加透徹。下面咱們廢話就不多說了,一起來看看吧。

2022-07-18 09:52:36 2532

2532 可綜合的語法是指硬件能夠?qū)崿F(xiàn)的一些語法,這些語法能夠被EDA工具支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數(shù)據(jù)流。

2023-07-23 12:25:10 2600

2600 Verilog HDL語法,要的拿

2016-01-24 22:53:48

Verilog HDL的基本語法 .pdf

2012-08-15 15:06:11

Verilog 變量聲明與數(shù)據(jù)類型一Verilog語法中最基本的數(shù)據(jù)類型有 線網(wǎng)(wire),寄存器(reg)和整數(shù)(integer)三種類型,這三種數(shù)據(jù)類型是可綜合的數(shù)據(jù)類型,在Verilog

2021-08-10 14:01:06

Verilog 紅寶書_語法基礎(chǔ)(恒創(chuàng)科技原創(chuàng))

2013-09-27 22:02:08

本帖最后由 lee_st 于 2017-10-31 08:46 編輯

Verilog語法基礎(chǔ)講解之參數(shù)化設(shè)計(jì)

2017-10-21 20:56:17

Verilog比較細(xì)節(jié)的`語法

2012-09-17 23:47:41

Verilog中阻塞賦值與非阻塞賦值的區(qū)別

2020-12-30 06:22:29

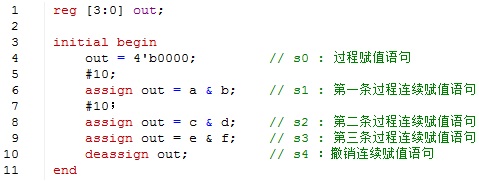

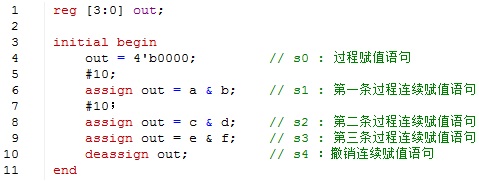

[table][tr][td] Verilog中有兩種為變量賦值的方法。一種叫做連續(xù)賦值,另一種叫做過程賦值。過程賦值又分為阻塞賦值和非阻塞賦值。阻塞性賦值使用“=”為變量賦值,在賦值結(jié)束前不可以進(jìn)行其他操作,在賦值結(jié)束之后繼續(xù)后面的操作。這個(gè)過程就好像阻斷了程序的運(yùn)行。非阻塞賦值使用“

2018-07-03 03:06:04

Verilog基礎(chǔ)語法

2021-05-27 08:00:00

本帖最后由 richthoffen 于 2021-3-3 10:30 編輯

Verilog紅寶書_語法篇_恒創(chuàng)科技出品 V1.0

2021-03-03 10:29:22

Verilog紅寶書_基本語法_上_恒創(chuàng)科技出品 V1.4

2016-10-09 08:55:47

Verilog紅寶書_基本語法_下_恒創(chuàng)科技出品 V1.1

2016-10-09 08:53:42

verilog 語法在復(fù)習(xí)進(jìn)階

2013-09-19 08:18:00

。 建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時(shí)應(yīng)注意以下要點(diǎn): (1)不使用初始化語句。 (2)不使用帶有延時(shí)的描述。 (3)不使用循環(huán)次數(shù)不確定的循環(huán)語句,如

2012-10-20 08:10:13

verilog HDL語法總結(jié)

2020-03-16 14:26:27

剛學(xué)verilog,試了一下非阻塞賦值,代碼如下, 很簡單module test(clk,in,out);input clk;input in;output reg out;always @(posedge clk)out

2012-10-30 09:20:14

verilog語法學(xué)習(xí)心得1.數(shù)字電路基礎(chǔ)知識: 布爾代數(shù)、門級電路的內(nèi)部晶體管結(jié)構(gòu)、組合邏輯電路分析與設(shè)計(jì)、觸發(fā)器、時(shí)序邏輯電路分析與設(shè)計(jì)2.數(shù)字系統(tǒng)的構(gòu)成: 傳感器AD數(shù)字處理器DA執(zhí)行部件3.

2012-01-12 15:15:21

verilog語法練習(xí)晉級篇

2016-09-02 13:40:12

、assign、always、task等語句或者模塊進(jìn)行復(fù)制。在generate語句中可以引入if-else和case語句,根據(jù)條件不同產(chǎn)生不同的實(shí)例化。在設(shè)計(jì)中,很多情況下需要編寫很多結(jié)構(gòu)相同但是參數(shù)

2020-12-23 16:59:15

verilog是什么?基本語法有哪些?

2021-09-18 07:41:04

在CAD電氣制圖的弱電平面設(shè)計(jì)中,經(jīng)常會需要給設(shè)備賦值,可是當(dāng)CAD圖紙中有很多設(shè)備都需要賦值時(shí),如果一個(gè)個(gè)進(jìn)行設(shè)備參數(shù)賦值的話又會很麻煩,此時(shí)就需要用到浩辰CAD電氣制圖軟件中的CAD批量賦值功能

2021-06-29 16:47:45

FPGA-Verilog HDL語法參考語法規(guī)范下列規(guī)范應(yīng)用于語法描述,規(guī)則采用巴科斯—諾爾范式(B N F)書寫:1) 語法規(guī)則按自左向右非終結(jié)字符的字母序組織。2) 保留字、操作符和標(biāo)點(diǎn)標(biāo)記

2012-08-11 10:33:08

Verilog語法是指硬件能夠?qū)崿F(xiàn)的語法。它的子集很小。常用的RTL語法結(jié)構(gòu)如下:

1、模塊聲明:module ... end module

2、端口聲明:input, output, inout

2024-06-23 14:58:32

本書主要講解verilog語法知識,只需看前7章,后面是例子。

2014-10-10 09:38:56

VHDL與verilog 的比較1vhdl語法要求嚴(yán)格 如賦值的數(shù)據(jù)類型必須一致, 左邊為整數(shù),右邊必須也為整數(shù), 左邊為矢量右邊必須也為矢量左右的數(shù)據(jù)的 位寬必須也一致,例如: library

2013-05-30 15:12:47

本帖最后由 eehome 于 2013-1-5 09:56 編輯

《Verilog HDL實(shí)驗(yàn)練習(xí)與語法手冊》-夏宇聞

2012-08-09 14:09:08

、命名端口連接等。目前,Verilog-2001是Verilog的最主流版本,被大多數(shù)商業(yè)電子設(shè)計(jì)自動化軟件支持。5.1.2為什么需要Verilog在FPGA設(shè)計(jì)里面,我們有多種設(shè)計(jì)方式,如原理圖

2020-09-21 16:48:48

】parameter聲明常量

第22練:【verilog每日一練】參數(shù)傳遞

第23練:【verilog每日一練】條件編譯的使用

第24練:【verilog每日一練】變量位寬截取語法

第25練:【verilog每日一練

2023-08-01 10:37:52

` 本帖最后由 小梅哥 于 2015-12-17 12:26 編輯

在Verilog語法中,可以實(shí)現(xiàn)參數(shù)化設(shè)計(jì)。所謂參數(shù)化設(shè)計(jì),就是在一個(gè)功能模塊中,對于一個(gè)常量,其值在不同的應(yīng)用場合需要設(shè)置為

2015-11-26 10:50:51

FPGA常用的基本類型wire、reg和parameter。wire:線網(wǎng)型數(shù)據(jù),表示硬件單元之間的物理連線,是verilog中默認(rèn)的數(shù)據(jù)類型,由assign操作關(guān)鍵字賦值,可以是一個(gè)賦值表達(dá)式

2022-06-23 14:51:52

什么是Verilog HDL阻塞賦值?主要應(yīng)用在哪些方面?

2019-08-02 06:22:43

示寄存器,可用來存儲數(shù)據(jù)的。

②、如何對變量進(jìn)行賦值呢?

學(xué)習(xí)C語言可以知道賦值就是用=號,比方int a = 15;//將15賦值給a;然而在verilog語法中也有 =(阻塞賦值) 這種賦值方式

2024-05-31 18:31:46

always@(posedge XXX)的塊語句內(nèi)的賦值符號使用的是 “<=” 注:摘自夏宇文老師的書學(xué)識淺薄出拙文,如察錯誤望賜教,小弟在此感涕零。欲瞧凔海筆記之單片機(jī)、FPGA等系列文章,請戳下面鏈接(*^__^*) 嘻嘻……凔海筆記``

2016-03-16 10:45:02

可綜合的Verilog語法和語義(劍橋大學(xué),影印)

2012-08-06 13:03:57

)中,\"<=\"作為非阻塞賦值的一部分。

verilog中,一個(gè)語法結(jié)構(gòu)不可能同時(shí)允許“表達(dá)式”和“語句”,

如果某處可以出現(xiàn)表達(dá)式,那么就不允許出現(xiàn)語句;

如果

2023-08-08 09:32:07

有沒有人對如何用參數(shù)化加法器樹編寫Verilog有任何建議,輸入參數(shù)是操作數(shù)的數(shù)量?加布里埃爾以上來自于谷歌翻譯以下為原文Does anyone have any suggestions

2019-04-25 13:28:42

b代表二進(jìn)制,d代表十進(jìn)制,那么這2個(gè)語句是否起到相同的效果呢?如果都是賦值0的話,應(yīng)該是無論在什么情況下的賦值,結(jié)果都不會變化吧?都是0?目前Verilog的語法是完全不懂,大家有什么好的Verilog語法書推薦嗎?

2017-08-29 16:42:05

在工程中,參數(shù)化設(shè)計(jì)是非常常見的。模塊接口的位寬,常見的有8位、16位、32位、64位和128位等;雖然功能相同,僅因?yàn)槲粚挷煌鸵硗鈱懸粋€(gè)模塊,那設(shè)計(jì)工作就很繁復(fù)了。為此,我們可以采用參數(shù)化來

2020-01-04 18:39:22

有沒有verilog語法手冊可以方便查找

2013-04-18 17:47:10

誰有STM8S ADC1初始化的函數(shù)例程呢?

2023-10-25 07:45:55

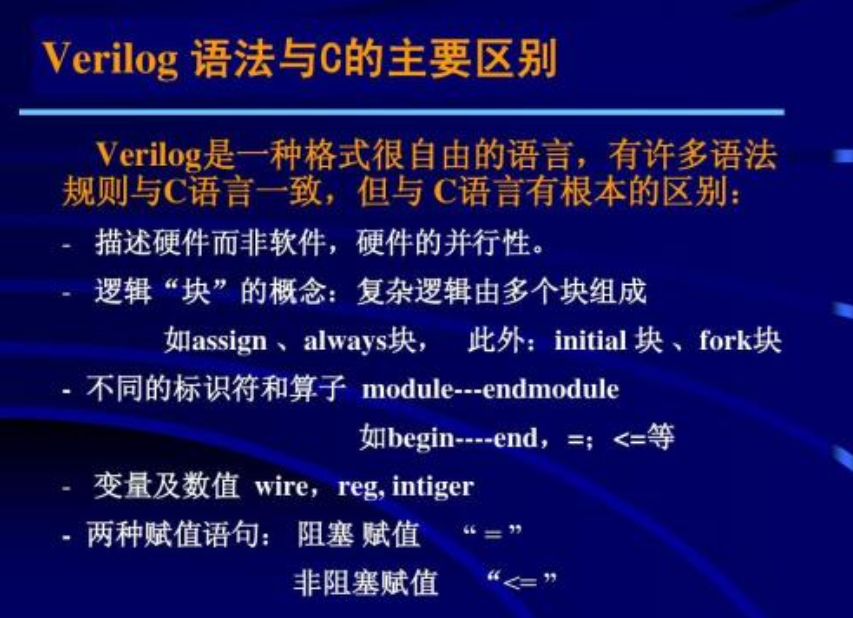

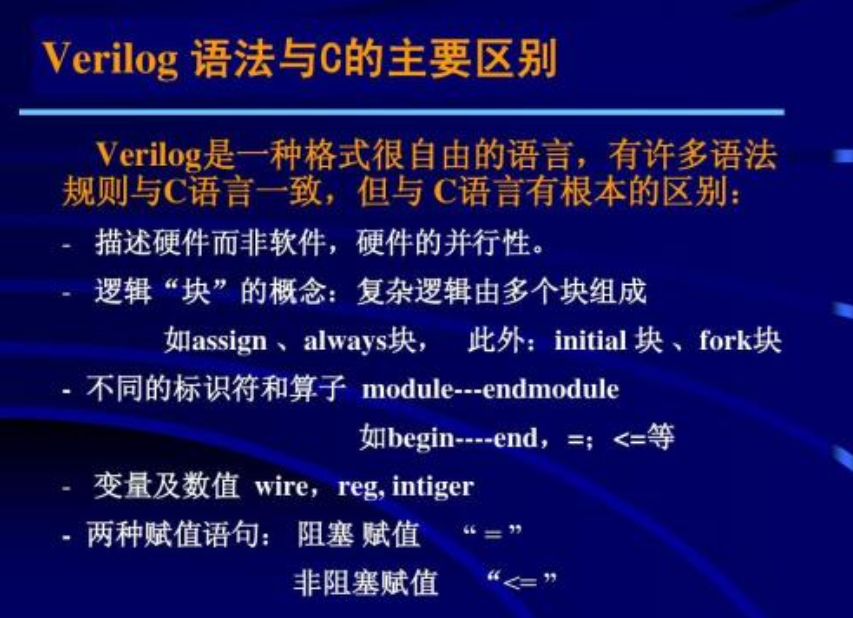

今天的學(xué)習(xí)吧!哈哈~這幾天復(fù)習(xí)了一下Verilog的語法知識,就借此寫寫我對這些東西的想法吧。感覺呢,是和C語言差不多,具有C語言基礎(chǔ)的朋友學(xué)起來應(yīng)該沒什么問題,和C語言相同的地方就不說了吧,重點(diǎn)說一下

2015-04-07 17:44:42

Synthesizable Verilog is a subset of the full Verilog HDL [9] that lies within the domain

2011-03-03 15:46:01 0

0 阻塞和非阻塞語句作為verilog HDL語言的最大難點(diǎn)之一,一直困擾著FPGA設(shè)計(jì)者,即使是一個(gè)頗富經(jīng)驗(yàn)的設(shè)計(jì)工程師,也很容易在這個(gè)點(diǎn)上犯下一些不必要的錯誤。阻塞和非阻塞可以說是血脈相連,但是又有著本質(zhì)的差別

2011-03-15 10:57:34 7239

7239 以前在貼Verilog代碼時(shí),都只能挑C++或者C#的語法著色,但兩者的主題詞畢竟不太一樣,透過dudu的幫助,我將Verilog 2001年的主題詞加上了,現(xiàn)在博客園也能漂亮的顯示Verilog代碼了!

2011-05-10 08:25:22 1244

1244 可綜合的Verilog語法和語義(劍橋大學(xué),影印):第七版

2012-05-21 14:50:14 27

27 Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結(jié)

2012-10-08 14:48:31 0

0 Verilog HDL實(shí)驗(yàn)練習(xí)與語法手冊-高教

2016-05-11 11:30:19 0

0 Verilog_HDL語言的學(xué)習(xí),為FPGA編程打下堅(jiān)實(shí)的基礎(chǔ)

2016-05-19 16:40:52 14

14 學(xué)習(xí)verilog最重要的不是語法,“因?yàn)?0%的語法就能完成90%的工作”,verilog語言常用語言就是always@(),if~else,case,assign這幾個(gè)了。

2018-03-26 14:06:00 3186

3186

常見的Verilog描述語句與對應(yīng)的邏輯關(guān)系;熟悉語法與邏輯之間的關(guān)系

2018-09-15 08:18:03 10862

10862

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之Verilog語法基礎(chǔ)的詳細(xì)資料說明資料免費(fèi)下載

2019-03-01 11:35:00 18

18 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述的語言。

2019-03-08 14:29:12 13726

13726 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之Verilog中兩種不同的賦值語句的資料說明免費(fèi)下載。

2019-03-27 10:55:59 6

6 Verilog與C語言還是存在許多差別。另外,作為一種與普通計(jì)算機(jī)編程語言不同的硬件描述語言,它還具有一些獨(dú)特的語言要素,例如向量形式的線網(wǎng)和寄存器、過程中的非阻塞賦值等。總的來說,具備C語言的設(shè)計(jì)人員將能夠很快掌握Verilog硬件描述語言。

2019-12-11 07:02:00 2375

2375

硬件描述語言基本語法和實(shí)踐

(1)VHDL 和Verilog HDL的各自特點(diǎn)和應(yīng)用范圍

(2)Verilog HDL基本結(jié)構(gòu)語言要素與語法規(guī)則

(3) Verilog HDL組合邏輯語句結(jié)構(gòu)

2019-07-03 17:36:00 54

54 本文檔的主要內(nèi)容詳細(xì)介紹的是有關(guān)Verilog中的一些語法詳細(xì)資料說明。

2019-07-25 17:08:33 2

2 HDL和VHDL的使用比率大概是80%和20%,在中國,大多數(shù)電子行業(yè)企業(yè)都采用Verilog。而模塊化的設(shè)計(jì)讓Verilog HDL語言具有思路清晰、邏輯關(guān)系明確、可讀性強(qiáng)等特點(diǎn),模塊化的設(shè)計(jì)在 Verilog HDL語法設(shè)計(jì)中也成為主流。

2020-03-25 08:00:00 4

4 1、阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進(jìn)程語句(initial和always)中,當(dāng)前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當(dāng)前的賦值語句執(zhí)行完畢才能執(zhí)行。而且阻塞賦值可以看成是一步完成的,即:計(jì)算等號右邊的值并同時(shí)賦給左邊變量。

2020-04-25 08:00:00 0

0 阻塞賦值對應(yīng)的電路往往與觸發(fā)沿沒有關(guān)系,只與輸入電平的變化有關(guān)系。非阻塞賦值對應(yīng)的電路結(jié)構(gòu)往往與觸發(fā)沿有關(guān)系,只有在觸發(fā)沿時(shí)才有可能發(fā)生賦值的情況。

2020-06-17 11:57:41 12065

12065

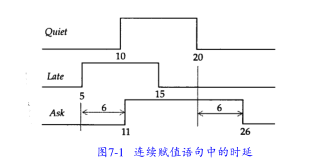

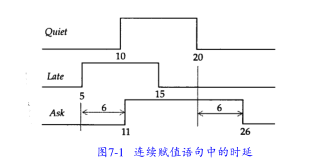

連續(xù)賦值語句總是處于激活狀態(tài)。只要任意一個(gè)操作數(shù)發(fā)生變化,表達(dá)式就會被立即重新計(jì)算,并且將結(jié)果賦給等號左邊的線網(wǎng)。

2020-11-26 10:04:44 4194

4194

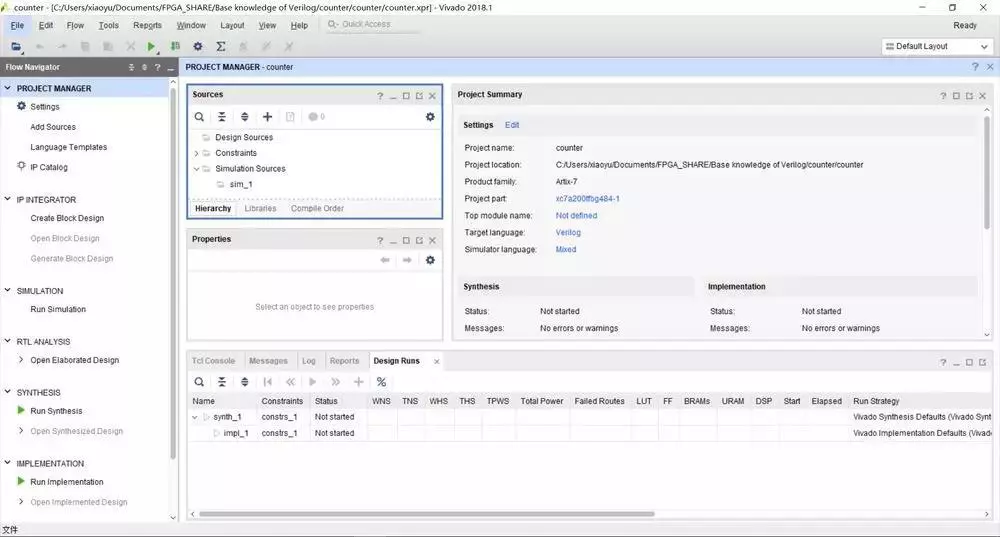

作者:小魚,Xilinx學(xué)術(shù)合作 一.概述 在文章《Verilog HDL入門思路梳理》我們說過應(yīng)該如何去學(xué)習(xí)Verilog HDL描述。然而第一步,我們需要知道Verilog有哪些語法,它是否可以

2021-01-02 09:45:00 2234

2234

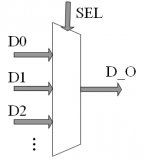

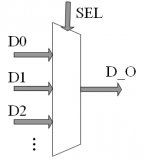

本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Verilog語言實(shí)現(xiàn)持續(xù)賦值方式定義的2選1多路選擇器程序免費(fèi)下載。

2020-10-28 16:54:27 14

14 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Verilog語言實(shí)現(xiàn)持續(xù)賦值方式定義的2選1多路選擇器程序免費(fèi)下載。

2020-10-28 16:54:27 6

6 數(shù)據(jù)流模型化 本章講述Verilog HDL語言中連續(xù)賦值的特征。連續(xù)賦值用于數(shù)據(jù)流行為建模;相反,過程賦值用于(下章的主題)順序行為建模。組合邏輯電路的行為最好使用連續(xù)賦值語句建模。 7.1 連續(xù)

2021-03-05 15:38:21 4839

4839

電子發(fā)燒友網(wǎng)為你提供+:和-:符號,Verilog標(biāo)準(zhǔn)文檔中的一個(gè)語法資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:41:41 15

15 Verilog語法進(jìn)階說明。

2021-05-06 16:14:58 30

30 簡單介紹Verilog HDL語言和仿真工具。

2021-05-06 16:17:10 619

619 阻塞賦值和非阻塞賦值的可綜合性 Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進(jìn)程管理的術(shù)語。由于Verilog團(tuán)隊(duì)是從C語言發(fā)展

2021-05-12 09:45:09 3264

3264

Verilog入門教程,介紹Verilog的語法知識,基本程序編寫。

2021-08-13 10:56:40 2

2 阻塞賦值,但從字面意思來看,阻塞就是執(zhí)行的時(shí)候在某個(gè)地方卡住了,等這個(gè)操作執(zhí)行完在繼續(xù)執(zhí)行下面的語句,而非阻塞就是不管執(zhí)行完沒有,我不管執(zhí)行的結(jié)果是什么,反正我繼續(xù)下面的事情。而Verilog中的阻塞賦值與非阻塞賦值正好也是這個(gè)意思,通過執(zhí)行一個(gè)例子

2021-12-02 18:24:36 7318

7318

Verilog HDL入門教程-Verilog HDL的基本語法

2022-01-07 09:23:42 189

189 從仿真結(jié)果可以看出:在順序塊中,15ns的時(shí)候,l1被賦值為8’h2,在25ns的時(shí)候,l2被賦值為8’h8;而在并行塊中,10ns的時(shí)候,k2被賦值為8’h8,在15ns的時(shí)候,k1被賦值為8’h2。可以很容易明白順序塊和并行塊的特性。

2022-03-15 11:51:15 2503

2503 綜合工具讀入源文件,通過綜合算法將設(shè)計(jì)轉(zhuǎn)化為網(wǎng)表,比如DC。能夠綜合的特性要求Verilog語言能夠描述信號的各種狀態(tài)(0,1,x,z)、信號和模塊的連接(例化)以及模塊的邏輯(賦值以及各種運(yùn)算符)。

2022-07-07 09:53:52 1106

1106 方法:實(shí)際應(yīng)用里,通常需要在上電復(fù)位過程中對變量進(jìn)行初始化,如果數(shù)組個(gè)數(shù)少時(shí),直接賦初始值即可,但是數(shù)組個(gè)數(shù)多時(shí),可以用循環(huán)實(shí)現(xiàn)賦值,通常的循環(huán)語句有FOR和WHILE。(注意變量的賦值方式)

2022-09-23 14:20:08 13759

13759 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述的語言。

2022-12-08 14:00:57 3655

3655 阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進(jìn)程語句(initial和always)中,當(dāng)前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當(dāng)前的賦值語句執(zhí)行完畢才能執(zhí)行。

2022-12-19 16:49:28 9356

9356 FPGA 設(shè)計(jì)的硬件語言Verilog中的參數(shù)化有兩種關(guān)鍵詞:define 和 paramerter,參數(shù)化的主要目的是代碼易維護(hù)、易移植和可讀性好。

2022-12-26 09:53:10 1349

1349 Verilog-2005中有3個(gè)generate 語句可以用來很方便地實(shí)現(xiàn)重復(fù)賦值和例化(generate for)或根據(jù)條件選擇性地進(jìn)行編譯(generate if和generate case)等功能。接下來就一起看下這3個(gè)語句的應(yīng)用場景和應(yīng)用方法吧。

2022-12-28 15:21:43 3954

3954 )和連線(wire)息息相關(guān)。Verilog便具有將ASM圖表和電路框圖用計(jì)算機(jī)語言表達(dá)的能力,本文將講述Vivado綜合支持的Verilog硬件描述語言; Verilog提供了行為化和結(jié)構(gòu)化兩方面的語言結(jié)構(gòu),描述設(shè)計(jì)對象時(shí)可以選擇高層次或低層次的抽象等級。使用V

2022-12-29 10:30:09 7505

7505 ,因?yàn)槲覀兛梢愿p松地將代碼從一個(gè)設(shè)計(jì)移植到另一個(gè)設(shè)計(jì)。

我們在verilog中有兩個(gè)可用的結(jié)構(gòu),可以幫助我們編寫可重用的代碼 - 參數(shù)化和generate語句。這兩種結(jié)構(gòu)都允許我們創(chuàng)建更通用的代碼,當(dāng)我們實(shí)例化組件時(shí),我們可以輕松修改這些代碼以滿足我們的需求。

2023-05-11 15:59:21 1759

1759 只作為語法設(shè)定來介紹,忽略了Verilog語言的軟件特性和仿真特性。使得初學(xué)者無法理解Verilog語言在行為級語法(過程塊、賦值和延遲)背后隱藏的設(shè)計(jì)思想。本文嘗試從仿真器的角度對Verilog語言的語法規(guī)則進(jìn)行一番解讀。

2023-05-25 15:10:21 1496

1496

只作為語法設(shè)定來介紹,忽略了Verilog語言的軟件特性和仿真特性。使得初學(xué)者無法理解Verilog語言在行為級語法(過程塊、賦值和延遲)背后隱藏的設(shè)計(jì)思想。本文嘗試從仿真器的角度對Verilog語言的語法規(guī)則進(jìn)行一番解讀。

2023-05-25 15:10:44 1379

1379

對于VerilogHDL語言中,經(jīng)常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學(xué)者,往往非常迷惑這兩種賦值方式的用法,本章節(jié)主要介紹這兩種文章的用法。其實(shí),有時(shí)候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2023-06-01 09:21:57 2709

2709 ”=“阻塞賦值與”<=“非阻塞賦值是verilog語言中的兩種不同的賦值方式,下面將對兩種賦值方式進(jìn)行比較。方便進(jìn)行理解和使用。

2023-09-12 09:06:15 1790

1790

verilog極簡語法手冊

2023-10-23 09:28:46 2

2 Verilog是一種硬件描述語言,用于設(shè)計(jì)和模擬數(shù)字電路。在Verilog中,同步和異步是用來描述數(shù)據(jù)傳輸和信號處理的兩種不同方式,而阻塞賦值和非阻塞賦值是兩種不同的賦值方式。本文將詳細(xì)解釋

2024-02-22 15:33:04 2897

2897 本文繼續(xù)介紹Verilog HDL基礎(chǔ)知識,重點(diǎn)介紹賦值語句、阻塞與非阻塞、循環(huán)語句、同步與異步、函數(shù)與任務(wù)語法知識。

2024-10-24 15:00:35 1792

1792

verilog語法中使用以下兩個(gè)運(yùn)算符可以簡化我們的位選擇代碼。

2024-10-25 15:17:55 3413

3413

Verilog 與 VHDL 比較 1. 語法和風(fēng)格 Verilog :Verilog 的語法更接近于 C 語言,對于有 C 語言背景的工程師來說,學(xué)習(xí)曲線較平緩。它支持結(jié)構(gòu)化編程,代碼更直觀,易于

2024-12-17 09:44:44 2877

2877

電子發(fā)燒友App

電子發(fā)燒友App

評論