VHDL和Verilog數組的定義、初始化、賦值的方法不只一種,以下是本人常用的方法,可能不是最方便的,但是比較好理解,文中包含了源代碼和modelsim仿真,供大家參考學習。

1. VHDL數組定義、初始化、賦值

1)VHDL數組定義方法:通過TYPE定義個matri_index的數組,數組包含50個數據,數據位數為16;申明了receive_data和send_data兩個matri_index的數據。

--define a 16 bit array

constant

matrix_num:

integer := 49; TYPE

matrix_index is array (matrix_num downto 0) of std_logic_vector(15 downto 0);signal

receive_data, send_data:

matrix_index;signal

send_cnt:

STD_LOGIC_VECTOR(7 downto 0);

2)VHDL數組初始方法:實際應用里,通常需要在上電復位過程中對變量進行初始化,如果數組個數少時,直接賦初始值即可,但是數組個數多時,可以用循環實現賦值,通常的循環語句有FOR LOOP和WHILE LOOP。

(注意變量i申明的位置,需要在process內部,注意變量的賦值方式)

process(clk,reset_n)

--循環變量定義并初始化

variable i: integer := 0;

begin

if (reset_n = ‘0’)then

i := 0;

--利用while loop循環賦值

while(i《=matrix_num) loop

receive_data(i) 《=X“0000”;

i := i+1;

end loop;

elsif (rising_edge(clk)) then

--CONV_std_logic_vector(A,位寬)

將無符號的無符號整數轉換為std_logic_vector

--CONV_INTEGER(A)

將std_logic_vector轉換為整數

--直接賦值方式

send_cnt《= X“02”;

send_data(0) 《= X“0000”;

send_data(1) 《= X“0000”;

send_data(CONV_INTEGER(send_cnt)) 《= X“0000”;

end if;end process;

3)VHDL數組賦值

賦值語句分信號賦值語句和變量賦值語句兩種。每一種都有下面三個基本組成部分:賦值目標:是所賦值的受體,它的基本元素只能是信號或變量。

賦值符號:是賦值符號只有兩種。一種是信號賦值符號”《=”;另一種是變量賦值符號”:=”。賦值源:賦值源是賦值的主體,它可以是一個數值,也可以是一個邏輯或運算表達式。

可以直接賦值,如果變量為矢量時,需要將矢量轉為整型。(不管三七二十一,建議程序中增加以下包,否則類型轉換用不了)

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_arith.all;USE ieee.std_logic_unsigned.all;--CONV_std_logic_vector(A,位寬)

將無符號的無符號整數轉換為std_logic_vector--CONV_INTEGER(A)

將std_logic_vector轉換為整數 --直接賦值方式

send_cnt《= X“02”;send_data(0) 《= X“0000”;send_data(1) 《= X“0000”; send_data(CONV_INTEGER(send_cnt)) 《= X“0000”;

4)VHDL數組test代碼

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_arith.all;USE ieee.std_logic_unsigned.all; --this is commentENTITY array_test IS PORT( reset_n

: IN STD_LOGIC;

clk

: IN STD_LOGIC );

END array_test; ARCHITECTURE behavioural OF array_test IS--define a 16 bit array

constant

matrix_num:

integer := 49; TYPE

matrix_index is array (matrix_num downto 0) of std_logic_vector(15 downto 0);signal

receive_data, send_data:

matrix_index;signal

send_cnt:

STD_LOGIC_VECTOR(7 downto 0);BEGIN process(clk,reset_n)

--循環變量定義并初始化

variable i: integer := 0;

begin

if (reset_n = ‘0’)then

i := 0;

--利用while loop循環賦值

while(i《=matrix_num) loop

receive_data(i) 《=X“0000”;

i := i+1;

end loop;

elsif (rising_edge(clk)) then

--CONV_std_logic_vector(A,位寬)

將無符號的無符號整數轉換為std_logic_vector

--CONV_INTEGER(A)

將std_logic_vector轉換為整數

--直接賦值方式

send_cnt《= X“02”;

send_data(0) 《= X“0000”;

send_data(1) 《= X“0000”;

send_data(CONV_INTEGER(send_cnt)) 《= X“0000”;

end if;end process; END behavioural;

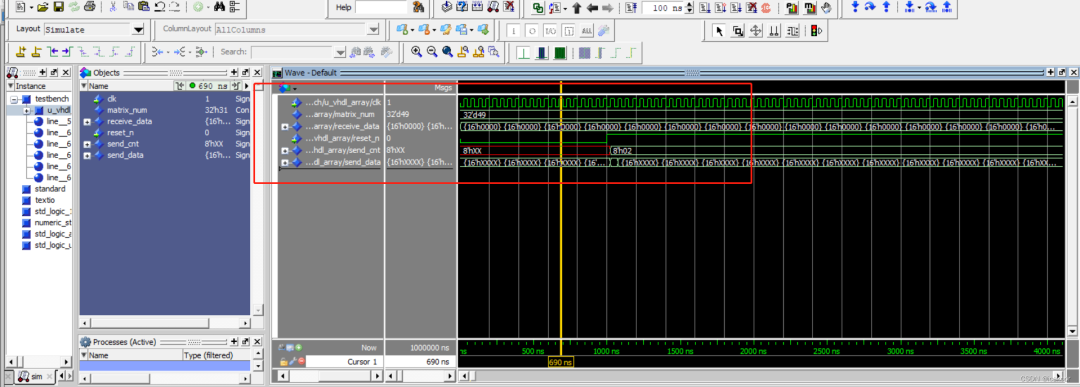

5)modesim 仿真結果

2. Verilog數組定義、初始化、賦值

1)Verilog數組定義方法:reg[n-1 : 0]

定義了存儲器中每個寄存器單元的大小,即存儲單元是一個n位的寄存器;存儲器后面的[m-1 : 0]則定義了該存儲器中有多少個這樣的寄存器。

reg[n-1 : 0] 存儲器名 [m-1 : 0];或者 reg[n : 1] 存儲器名 [m : 1];

//define a 16 bit array parameter wordsize = 16, memsize = 49;reg [wordsize-1 : 0] send_data[memsize-1 : 0], receive_data[memsize-1 : 0];integer i = 0;reg [7:0] send_cnt

;2)Verilog數組初始方法:實際應用里,通常需要在上電復位過程中對變量進行初始化,如果數組個數少時,直接賦初始值即可,但是數組個數多時,可以用循環實現賦值,通常的循環語句有FOR和WHILE。

(注意變量的賦值方式)

always@(posedge clk, reset_n)beginif(!reset_n) beginwhile(i 《=memsize)beginreceive_data[i] 《= 16‘h0000;i = i+1;

//阻塞賦值endendelse begin

//直接賦值方式send_cnt 《= 8’h02;send_data[0] 《= 16‘h0000;send_data[1] 《= 16’h0000;send_data[send_cnt] 《=16‘h0000;

//不需要類型轉換endend

3)Verilog數組賦值不像VHDL那樣,可以直接賦值。

//直接賦值方式send_cnt 《= 8’h02;send_data[0] 《= 16‘h0000;send_data[1] 《= 16’h0000;send_data[send_cnt] 《=16‘h0000;

//不需要類型轉換

4)Verilog數組test代碼

module verilog_test(clk,reset_n);inputclk;inputreset_n; // /////define a 16 bit array parameter wordsize = 16,

memsize = 49;reg [wordsize-1 : 0] send_data[memsize-1 : 0],

receive_data[memsize-1 : 0];integer i = 0;reg [7:0] send_cnt; always@(posedge clk, reset_n)beginif(!reset_n) beginwhile(i 《=memsize)beginreceive_data[i] 《= 16’h0000;i = i+1;

//非阻塞賦值endendelse begin

//直接賦值方式send_cnt 《= 8‘h02;send_data[0] 《= 16’h0000;send_data[1] 《= 16‘h0000;send_data[send_cnt] 《=16’h0000;

//不需要類型轉換endendendmodule

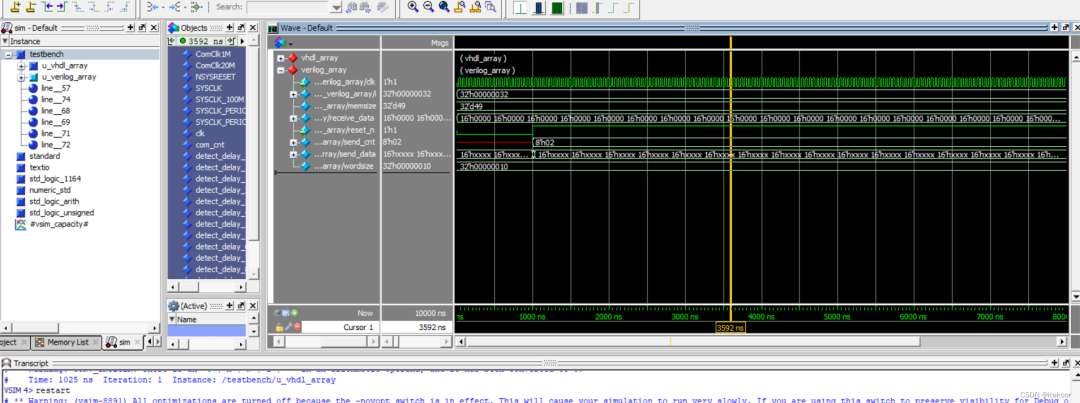

5)modelsim仿真結果

審核編輯 :李倩

-

Verilog

+關注

關注

30文章

1374瀏覽量

114520 -

vhdl

+關注

關注

30文章

822瀏覽量

131680 -

數組

+關注

關注

1文章

420瀏覽量

27351

原文標題:FPGA學習-VHDL和Verilog中數組定義、初始化、賦值方法

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

MCU工程初始化,到底該不該交給工具?

EtherCAT總線初始化步驟

瀚海微SD NAND TF卡硬件識別與初始化類問題探討

串口通信基石:Air8000下Modbus RTU串口初始化詳解!

NVMe高速傳輸之擺脫XDMA設計33:初始化功能驗證與分析

GraniStudio:IO初始化以及IO資源配置例程

GraniStudio:初始化例程

MCU外設初始化:為什么參數配置必須優先于使能

定義IO初始化結構體

IM系列設備過載故障:界面初始化終止的診斷流程與修復指南

IM 系列設備過載保護機制下界面初始化中斷的底層邏輯與解決方案

在testbench中如何使用阻塞賦值和非阻塞賦值

VHDL和Verilog中數組定義、初始化、賦值方法

VHDL和Verilog中數組定義、初始化、賦值方法

評論