基于PLD的CCD Sensor驅(qū)動(dòng)邏輯設(shè)計(jì)

0 引 言

視覺(jué)信息是客觀世界中非常豐富,非常重要的部分。隨著多媒體系統(tǒng)的發(fā)展,圖像傳感器應(yīng)用越

2010-01-14 11:33:27 1861

1861

電器應(yīng)用中常用的隔離器件有光耦、繼電器、變壓器。

2022-07-30 14:23:26 5770

5770 在 Rust 語(yǔ)言中,Tokio 是一個(gè)非常流行的異步編程框架。它提供了一系列的模塊,其中最常用的就是 Stream 模塊。Stream 模塊允許我們以異步的方式處理數(shù)據(jù)流,這在很多情況下非常

2023-09-19 15:33:09 2013

2013 2.2 筆記本電腦中常用芯片的種類(lèi)和功能特點(diǎn)筆記本, 筆記本入門(mén)2.2 筆記本電腦中常用芯片的種類(lèi)和功能特點(diǎn) 在筆記本電腦中有許多集成電路芯片,常見(jiàn)的主要有時(shí)鐘芯片、I/O芯片、電源管理芯片和邏輯

2010-12-26 22:11:48

STREAM DEV BOARD

2023-03-29 19:42:39

邏輯設(shè)計(jì)和校驗(yàn)工具v3.3版本下載完整資料。大小:61.1M[hide]邏輯設(shè)計(jì)和校驗(yàn)工具v3.3.rar[/hide]

2009-10-29 14:32:52

偏硬件:接口電路中的門(mén)組合電路;偏軟件:算法、接口控制器實(shí)現(xiàn)中的狀態(tài)機(jī)群或時(shí)序電路。隨著邏輯設(shè)計(jì)的深入,復(fù)雜功能設(shè)計(jì)一般基于同步時(shí)序電路方式。此時(shí),邏輯設(shè)計(jì)基本上就是在設(shè)計(jì)狀態(tài)機(jī)群或計(jì)數(shù)器等時(shí)序電路

2021-11-10 06:39:25

Altium_designer中常用庫(kù)及常用操作

2015-11-12 16:07:44

圖像采集系統(tǒng)的結(jié)構(gòu)及工作原理是什么FPGA邏輯設(shè)計(jì)中的常見(jiàn)問(wèn)題有哪些

2021-04-29 06:18:07

請(qǐng)教各位,F(xiàn)PGA在邏輯設(shè)計(jì)中有哪些注意事項(xiàng)?

2021-05-07 07:21:53

及路線(xiàn)圖詳見(jiàn)報(bào)到通知)四、 課程簡(jiǎn)介本課程為期三天,旨在幫助已經(jīng)掌握一定設(shè)計(jì)基礎(chǔ)的工程師進(jìn)一步了解FPGA邏輯設(shè)計(jì)的方法與優(yōu)化技巧。講述了邏輯設(shè)計(jì)的驗(yàn)證、高級(jí)狀態(tài)機(jī)的設(shè)計(jì)、基于FPGA的DSP設(shè)計(jì)方法

2009-07-24 13:13:48

`MCS-51單片機(jī)與FPGA接口的邏輯設(shè)計(jì).........`

2013-06-08 11:25:29

MPEG-2編碼復(fù)用器中的FPGA邏輯設(shè)計(jì),看完你就懂了

2021-04-29 06:13:34

用過(guò)Matlab的同學(xué)應(yīng)該都知道,Matlab的慢是出了名的,但是再慢也有優(yōu)化的方式,下面我們給出幾個(gè)Matlab編程中常用的優(yōu)化技巧。??在講優(yōu)化方法之前,首先要說(shuō)的就是Matlab中用tic

2021-02-19 06:40:41

Multisim中常用的IGBT驅(qū)動(dòng)芯片有哪些求大神指教,急急急

2013-12-24 14:51:13

Sequential Logic Design principles 時(shí)序邏輯設(shè)計(jì)原則[hide][/hide]

2009-09-26 13:00:22

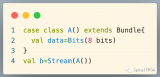

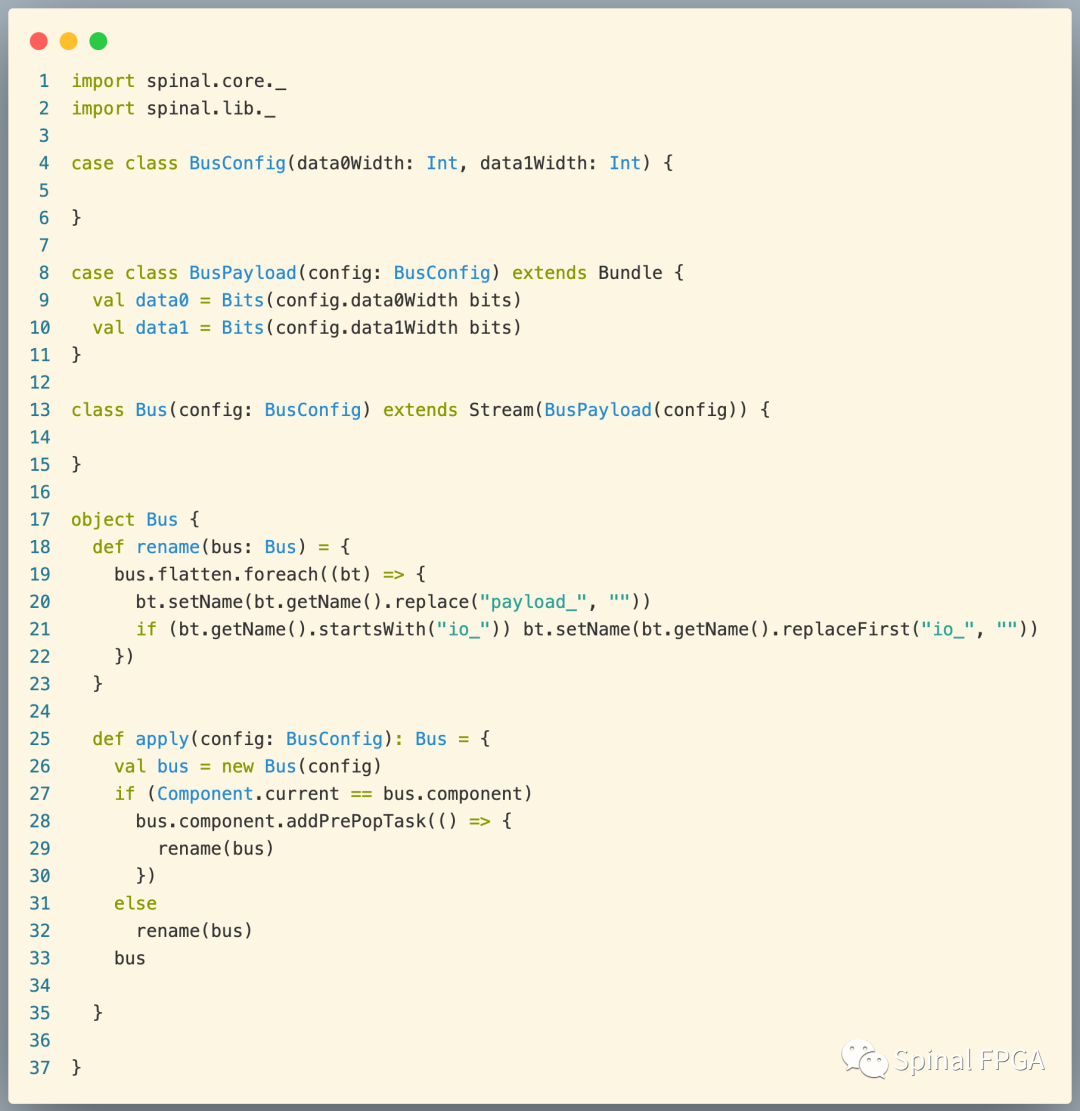

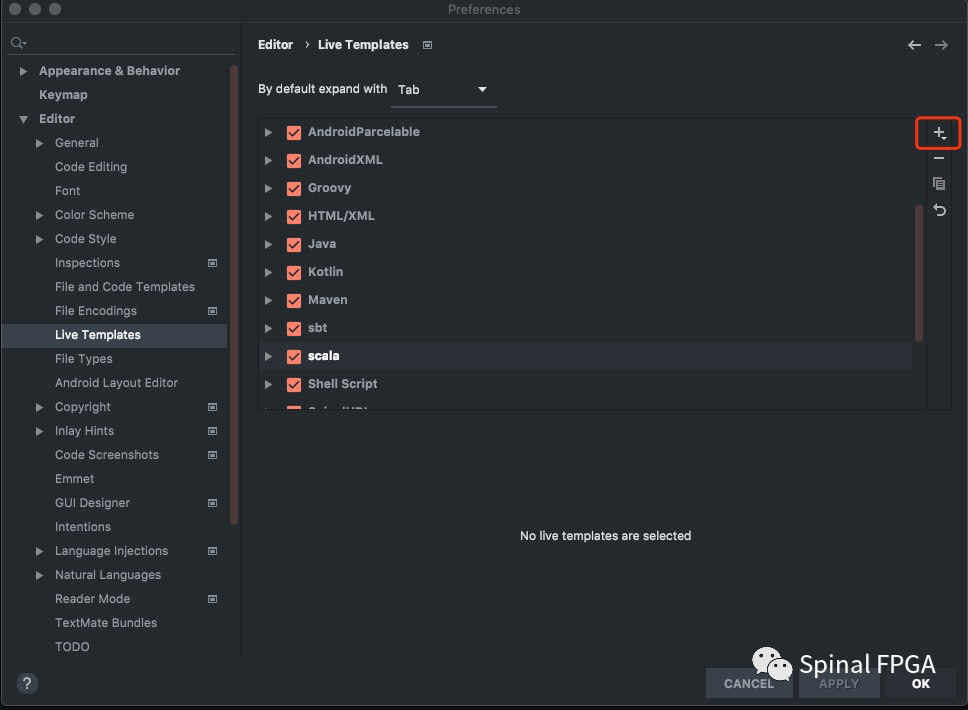

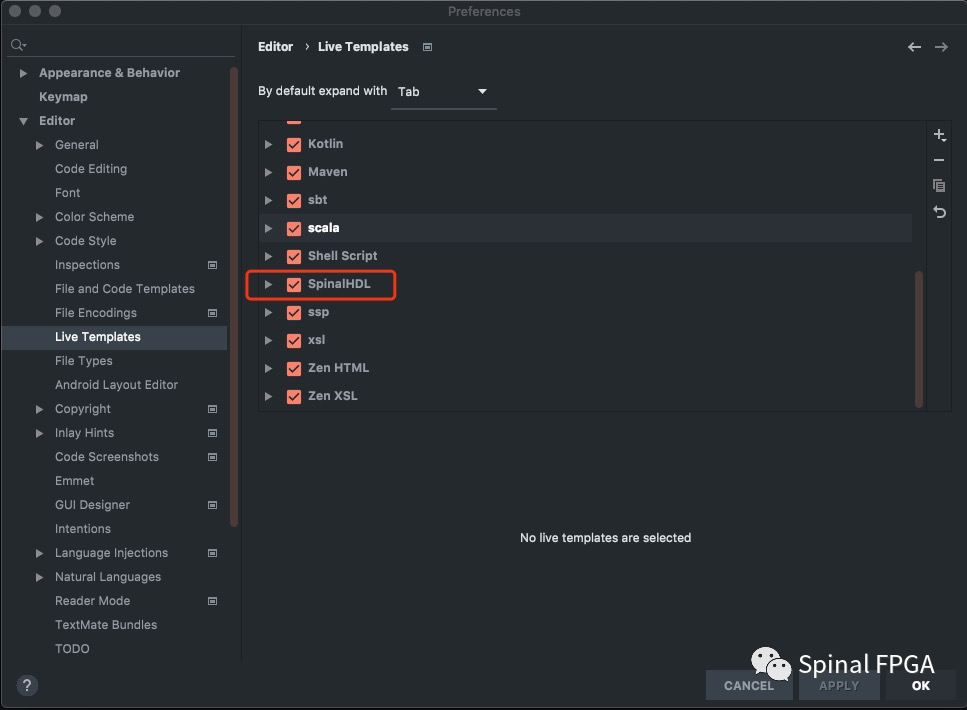

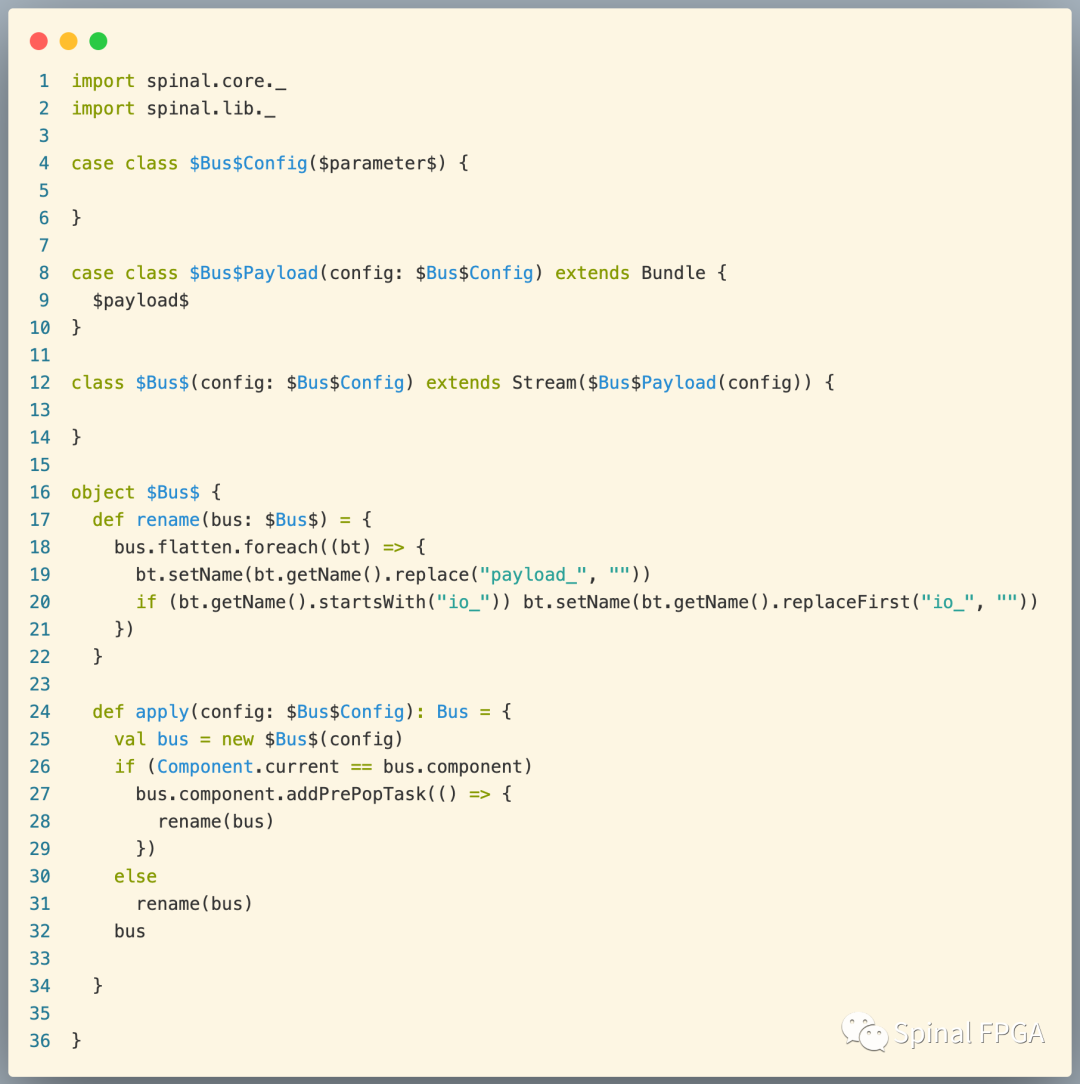

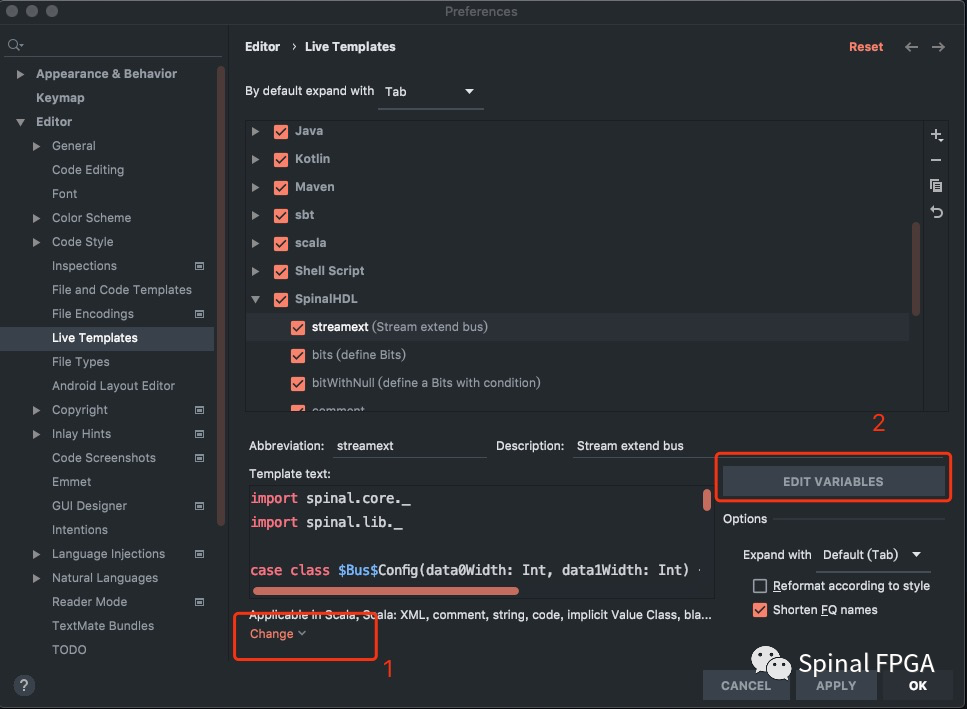

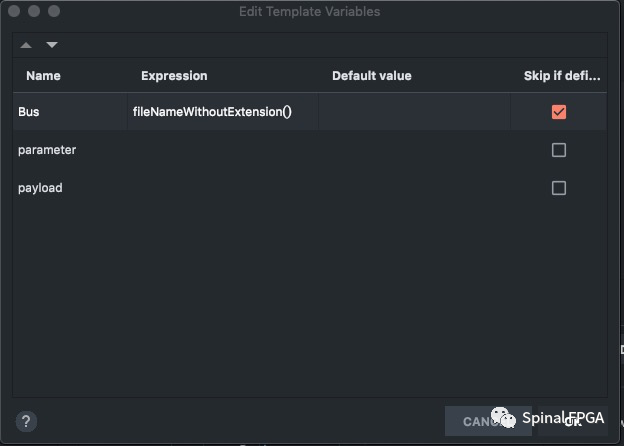

編 者 按在邏輯設(shè)計(jì)中,基于Stream握手這種形式的總線(xiàn)行為是很常見(jiàn)的,在自定義總線(xiàn)時(shí)Stream這類(lèi)總線(xiàn)代碼寫(xiě)起來(lái)千篇一律,完全可以利用IDEA的live template來(lái)自動(dòng)生成。常用

2023-01-31 16:38:03

本篇講解一個(gè)小的example,帶你一起看點(diǎn)兒SpinalHDL里有趣地玩兒法。不講理—總線(xiàn)插隊(duì)先來(lái)看一個(gè)波形圖:這里有一組輸入Stream總線(xiàn)接口、一組輸出Stream總線(xiàn),它的電路規(guī)則描述

2022-07-21 14:31:07

c語(yǔ)言中常用的宏定義有哪些?

2021-04-28 06:01:10

各位大神們,誰(shuí)有proteus中常用的英文單詞啊,給小弟發(fā)一下

2013-12-05 22:27:29

靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)

2015-05-27 12:28:46

交通燈控制邏輯設(shè)計(jì)n 1、紅、綠、黃發(fā)光二極管作信號(hào)燈,用傳感器或邏輯開(kāi)關(guān)作檢測(cè)車(chē)輛是否到來(lái)的信號(hào),實(shí)驗(yàn)電路用邏輯開(kāi)關(guān)代替。n 2、主干道處于常允許通行的狀態(tài),支干道有車(chē)來(lái)時(shí)才允許通行。主干道亮綠

2017-09-15 10:25:06

在SpinalHDL中,Stream的抽象可謂諸多設(shè)計(jì)的核心,今天,一同來(lái)看下不帶數(shù)據(jù)的Stream——Event。》不帶數(shù)據(jù)的Stream在邏輯設(shè)計(jì)里,握手信號(hào)處處可見(jiàn),在SpinalHDL里

2022-06-27 16:07:04

以保證速度。PLC編程也一樣,建筑中的預(yù)制標(biāo)準(zhǔn)件就像我們編程中的庫(kù)函數(shù),可以使我們?cè)诰幊痰倪^(guò)程中節(jié)約大量的時(shí)間和精力。 下面就給大家介紹一些PLC編程中常用的基礎(chǔ)邏輯。我們的編程以S7-200為例

2023-03-13 17:20:33

華為 大規(guī)模邏輯設(shè)計(jì)指導(dǎo)書(shū) 方法 論

2019-11-22 22:52:12

本帖最后由 eyesee 于 2017-3-2 09:29 編輯

華為_(kāi)大規(guī)模邏輯設(shè)計(jì)指導(dǎo)書(shū)

2017-03-01 11:56:34

華為_(kāi)大規(guī)模邏輯設(shè)計(jì)指導(dǎo)書(shū)

2012-08-18 08:11:53

華為大規(guī)模邏輯設(shè)計(jì)指導(dǎo)書(shū)

2015-04-20 13:41:35

華為大規(guī)模邏輯設(shè)計(jì)指導(dǎo)書(shū)。非常詳細(xì)地介紹了邏輯設(shè)計(jì)的規(guī)范要求及方法。

2020-01-27 17:58:38

華為靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)

2014-05-20 22:55:09

單片機(jī)與FPGA總線(xiàn)接口邏輯設(shè)計(jì)1、利用FPGA內(nèi)部RAM存儲(chǔ)256個(gè)字節(jié)數(shù)據(jù),并將數(shù)據(jù)發(fā)送到單片機(jī)并在串口調(diào)試工具顯示;2、通過(guò)串口調(diào)試工具經(jīng)單片機(jī)發(fā)送數(shù)據(jù)到FPGA,并通過(guò)LED顯示。

2012-03-04 13:09:58

單片機(jī)項(xiàng)目設(shè)計(jì)中常用的NMOS+PMOS控制電路是什么?

2022-02-11 06:12:37

了如何通過(guò)FPGA實(shí)現(xiàn)RS 232接口的時(shí)序邏輯設(shè)計(jì)。關(guān)鍵詞:FPGA;時(shí)序電路;RS 232;串行通信

2019-06-19 07:42:37

本文使用符合PCI電氣特性的FPGA芯片進(jìn)行簡(jiǎn)化的PCI接口邏輯設(shè)計(jì),實(shí)現(xiàn)了33MHz、32位數(shù)據(jù)寬度的PCI從設(shè)備模塊的接口功能,節(jié)約了系統(tǒng)的邏輯資源,且可以將其它用戶(hù)邏輯集成在同一塊芯片,降低了成本,增加了設(shè)計(jì)的靈活性。

2021-05-08 08:11:59

前言FPGA 可以實(shí)現(xiàn)高速硬件電路,如各種時(shí)鐘,PWM,高速接口,DSP計(jì)算等硬件功能。這是Cortex-M 處理器軟件無(wú)法比擬的。要實(shí)現(xiàn)FPGA 的邏輯設(shè)計(jì),對(duì)于嵌入式系統(tǒng)工程師又是比較復(fù)雜和具有

2021-12-21 06:13:49

盤(pán)點(diǎn)嵌入式開(kāi)發(fā)中常用的總線(xiàn)與接口

2021-02-01 07:25:47

本帖最后由 eehome 于 2013-1-5 09:51 編輯

工業(yè)中常用的總線(xiàn)技術(shù)

2012-08-20 21:22:14

微機(jī)中常見(jiàn)的各類(lèi)總線(xiàn)技術(shù)有哪幾種?

2021-10-14 06:28:52

本帖最后由 daworencai 于 2016-1-21 14:46 編輯

崗位職責(zé):1.負(fù)責(zé)部門(mén)存儲(chǔ)系列產(chǎn)品的邏輯設(shè)計(jì)開(kāi)發(fā)工作;2.負(fù)責(zé)存儲(chǔ)系列產(chǎn)品的BCH算法優(yōu)化、高速存儲(chǔ)技術(shù)實(shí)現(xiàn)等;負(fù)責(zé)

2016-01-21 14:42:39

屬于系統(tǒng)總線(xiàn)的有哪幾種?什么是總線(xiàn)復(fù)用?總線(xiàn)復(fù)用有何功能?總線(xiàn)特性包括哪幾種?控制總線(xiàn)中常見(jiàn)的控制信號(hào)包括哪些?

2021-08-11 07:28:49

數(shù)字電路與邏輯設(shè)計(jì)數(shù)字邏輯電路的分析和方法,常用集成數(shù)字邏輯電路的功能和應(yīng)用;主要內(nèi)容包括:邏輯代數(shù)基礎(chǔ)、組合邏輯電路分析和設(shè)計(jì)、常用組合邏輯電路及MSI組合電路模塊的應(yīng)用,時(shí)序邏輯電路的分析

2021-08-06 07:33:41

MOS管具有哪些特性?模塊電源中常用的MOSFET驅(qū)動(dòng)電路有哪些?

2021-11-01 06:45:05

要使用哪種方法去驗(yàn)證 FPGA 的邏輯設(shè)計(jì)?FPGA的優(yōu)缺點(diǎn)是什么?

2021-04-08 06:57:32

請(qǐng)問(wèn)一下印制電路板中常用標(biāo)準(zhǔn)是什么?

2021-04-23 06:26:03

請(qǐng)問(wèn)一下在POE網(wǎng)絡(luò)變壓器中常用的POE電流路徑是什么?

2021-10-12 09:38:10

靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)

2017-12-08 14:49:57

中規(guī)模集成時(shí)序邏輯設(shè)計(jì):計(jì)數(shù)器:在數(shù)字邏輯系統(tǒng)中,使用最多的時(shí)序電路要算計(jì)數(shù)器了。它是一種對(duì)輸入脈沖信號(hào)進(jìn)行計(jì)數(shù)的時(shí)序邏輯部件。9.1.1 計(jì)數(shù)器的分類(lèi)1.按數(shù)制

2009-09-01 09:09:09 13

13 設(shè)計(jì)一種基于MCS-51 單片機(jī)與FPGA/CPLD 的總線(xiàn)接口邏輯,實(shí)現(xiàn)單片機(jī)與可編程邏輯器件數(shù)據(jù)與控制信息的可靠通信,使可編程邏輯器件與單片機(jī)相結(jié)合,優(yōu)勢(shì)互補(bǔ),組成靈活的、軟硬件

2009-09-22 10:16:40 83

83 時(shí)序邏輯設(shè)計(jì)原則 (Sequential Logic Design principles):A sequential logic circuit is one whose outputs

2009-09-26 12:54:35 33

33 時(shí)序邏輯設(shè)計(jì)實(shí)踐 (Sequential Logic Design Practices)The purpose of this chapter is to familiarize you

2009-09-26 12:57:53 13

13 基于PLD芯片的時(shí)序邏輯設(shè)計(jì)與實(shí)現(xiàn):原理圖輸入設(shè)計(jì)直觀、便捷、操作靈活;1-1、原理圖設(shè)計(jì)方法簡(jiǎn)介QuartusII已包含了數(shù)字電路的基本邏輯元件庫(kù)(各類(lèi)邏輯門(mén)及觸發(fā)器),宏

2009-10-29 22:03:10 0

0 本文介紹了一種基于FPGA 的用自定義串口命令的方式實(shí)現(xiàn)MDIO 接口邏輯設(shè)計(jì)的方法,并對(duì)系統(tǒng)結(jié)構(gòu)進(jìn)行了模塊化分解以適應(yīng)自頂向下的設(shè)計(jì)方法。所有功能的實(shí)現(xiàn)全部采用VHDL 進(jìn)行描

2009-12-26 16:48:44 103

103

針對(duì)1553B 總線(xiàn)協(xié)議控制器基本依賴(lài)于進(jìn)口專(zhuān)用芯片現(xiàn)狀,提出了以Xilinx 公司

Virtex-II Pro FPGA 為核心實(shí)現(xiàn)1553B 總線(xiàn)接口邏輯的系統(tǒng)設(shè)計(jì)方案。采用SOPC 技術(shù),將

PowerPC 40

2010-01-25 14:38:57 31

31 華為大規(guī)模邏輯設(shè)計(jì)指導(dǎo)書(shū)

目的編寫(xiě)該規(guī)范的目的是提高書(shū)寫(xiě)VHDL代碼的可讀性可修改性可重用性?xún)?yōu)化代碼綜合和仿真的結(jié)果指導(dǎo)設(shè)計(jì)工程師使用VHDL規(guī)范

2010-03-13 15:02:03 0

0 摘要:“邏輯設(shè)計(jì)”課是近二、三十年隨著信息類(lèi)一批新專(zhuān)業(yè)(自動(dòng)化、計(jì)算機(jī)、通信和信息等)陸續(xù)建立而開(kāi)設(shè)的一門(mén)重要的學(xué)科基礎(chǔ)課。只要掌握“邏輯設(shè)計(jì)”課的特點(diǎn)和主要問(wèn)題

2010-05-25 10:10:29 0

0 ASIC與大型邏輯設(shè)計(jì)實(shí)習(xí)課

AgendaCell Base IC DesignModelSimLibraryProjectVHDL Compiler & SimulationSimulation WindowsTutorialLab

2010-06-19 09:45:20 0

0 工作站中常用的內(nèi)存類(lèi)型

目前工作站中常用的內(nèi)存有SDRAM、DDR及RAMBUS等幾種內(nèi)存。 SDRAM

2009-12-18 12:08:54 1361

1361 本文討論了高速串行鏈路中常用的測(cè)試碼型偽隨機(jī)碼流的原理,以及不同的測(cè)試碼型對(duì)物理層測(cè)試結(jié)果的影響。

高速串行總線(xiàn)的常用測(cè)試碼型

在當(dāng)今的

2011-01-04 10:40:19 4869

4869 為了提高溫度保護(hù)系統(tǒng)的可靠性,在溫度保護(hù)的邏輯設(shè)計(jì)中可采用容錯(cuò)設(shè)計(jì),即盡可能考慮測(cè)溫環(huán)節(jié)在運(yùn)行中容易出現(xiàn)的故障,并通過(guò)預(yù)先設(shè)置的邏輯措施來(lái)識(shí)別錯(cuò)誤的溫度信號(hào),以防保護(hù)系統(tǒng)誤動(dòng)。

2011-01-21 11:16:21 1854

1854

組合邏輯設(shè)計(jì)實(shí)例_國(guó)外:

2011-12-16 15:08:59 24

24 《數(shù)字電路與邏輯設(shè)計(jì)》答案

2012-06-25 08:19:15 23

23 Allegro中常用快捷鍵說(shuō)明,初學(xué)者可以根據(jù)這個(gè)來(lái)熟悉操作

2015-11-13 15:05:53 0

0 多分辨率圖像實(shí)時(shí)采集系統(tǒng)的FPGA邏輯設(shè)計(jì)

2016-08-29 15:02:03 6

6 華為靜態(tài)時(shí)序分析與邏輯設(shè)計(jì),基礎(chǔ)的資料,快來(lái)下載吧

2016-09-01 15:44:10 57

57 在線(xiàn)座談回放資料:5月27日 Altera 如何令邏輯設(shè)計(jì)在新一代CPLD中盡顯優(yōu)勢(shì) (問(wèn)答記錄)

2017-01-08 14:27:49 0

0 PADSLayout中常用的快捷鍵

2017-02-27 15:45:39 0

0 使用標(biāo)準(zhǔn)集成電路的邏輯設(shè)計(jì)課題

2017-09-19 11:41:06 19

19 基于AXI4Stream總線(xiàn)協(xié)議,在Xilinx公司提供的FPGA上實(shí)現(xiàn)了一個(gè)具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實(shí)時(shí)圖像采集與顯示功能的視頻系統(tǒng)。AXI4Stream總線(xiàn)協(xié)議由ARM公司

2017-11-17 08:58:01 5344

5344 IC前端設(shè)計(jì)(邏輯設(shè)計(jì))和后端設(shè)計(jì)(物理設(shè)計(jì))的區(qū)分:以設(shè)計(jì)是否與工藝有關(guān)來(lái)區(qū)分二者;從設(shè)計(jì)程度上來(lái)講,前端設(shè)計(jì)的結(jié)果就是得到了芯片的門(mén)級(jí)網(wǎng)表電路。

2017-12-25 16:08:21 34132

34132

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之FPGA設(shè)計(jì)中時(shí)序邏輯設(shè)計(jì)要點(diǎn)的詳細(xì)資料說(shuō)明免費(fèi)下載。

2019-03-27 10:56:04 20

20 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL語(yǔ)言組合邏輯設(shè)計(jì)方法以及QuartusII軟件的一些高級(jí)技巧。

2019-07-03 17:36:12 20

20 大幅度的削減,并適當(dāng)引進(jìn)與h刀應(yīng)用和現(xiàn)代邏輯設(shè)計(jì)有關(guān)的新概念、新方法,如vhdl、邏輯仿真等,由于未涉及器件內(nèi)部電路,故可在模擬電子線(xiàn)路前開(kāi)設(shè);第4—7章為“算術(shù)運(yùn)算電路”、“存儲(chǔ)器”、“終端、總線(xiàn)與接口(含a/d和d/a轉(zhuǎn)

2020-03-12 08:00:00 10

10 組合邏輯設(shè)計(jì)法適合于設(shè)計(jì)開(kāi)關(guān)量控制程序,它是對(duì)控制任務(wù)進(jìn)行邏輯分析和綜合,將元件的通、斷電狀態(tài)視為以觸點(diǎn)通、斷狀態(tài)為邏輯變量的邏輯函數(shù),對(duì)經(jīng)過(guò)化簡(jiǎn)的邏輯函數(shù),利用PLC邏輯指令可順利地設(shè)計(jì)出滿(mǎn)足要求且較為簡(jiǎn)練的程序。這種方法設(shè)計(jì)思路清晰,所編寫(xiě)的程序易于優(yōu)化。

2020-05-22 08:49:00 4638

4638 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路與邏輯設(shè)計(jì)實(shí)驗(yàn)報(bào)告模板。

2020-06-05 08:00:00 8

8 邏輯設(shè)計(jì) 開(kāi)始于高層次設(shè)計(jì)規(guī)范和芯片架構(gòu)。芯片架構(gòu)描述高層次功能、功耗和時(shí)序(設(shè)計(jì)運(yùn)行的速度)需求。緊接著對(duì)設(shè)計(jì)進(jìn)行寄存器傳輸層的描述,通常稱(chēng)為RTL(register transfer level

2021-03-08 14:39:34 5141

5141 機(jī)載機(jī)電管理系統(tǒng)的通道故障邏輯設(shè)計(jì)

2021-06-22 14:15:49 16

16 一、邏輯設(shè)計(jì) (1)組合邏輯設(shè)計(jì) 下面是一些用Verilog進(jìn)行組合邏輯設(shè)計(jì)時(shí)的一些注意事項(xiàng): ①組合邏輯可以得到兩種常用的RTL 級(jí)描述方式。第一種是always 模塊的觸發(fā)事件為電平敏感信號(hào)列表

2021-06-23 17:45:10 6056

6056

PCB中常用的快捷鍵匯總

2021-09-28 10:12:54 40

40 《數(shù)字電路與邏輯設(shè)計(jì)》李曉輝版課后答案詳解

2021-12-27 11:18:39 0

0 代理池是滲透測(cè)試中常用的工具,用來(lái)躲避各種各樣的封IP的防火墻,也幫助自身隱藏蹤跡.

2022-10-27 09:24:47 2749

2749 我在數(shù)字邏輯設(shè)計(jì)方面并沒(méi)有經(jīng)驗(yàn)。也就是說(shuō),直到最近我才決定嘗試設(shè)計(jì)自己的 CPU,并在 FPGA 上運(yùn)行!如果你也是一名軟件工程師,并對(duì)硬件設(shè)計(jì)有興趣,那么我希望這一系列關(guān)于我所學(xué)到的知識(shí)的文章能夠?qū)δ阌兴鶐椭⒆屇愀械接腥ぁ1鞠盗形恼碌牡谝徊糠种校瑢⒒卮鹨韵聠?wèn)題:

2022-11-01 09:25:03 2703

2703 上文中我們指出,不管我們是創(chuàng)建自定義 ASIC 芯片還是配置 FPGA,都可以使用相同的數(shù)字邏輯設(shè)計(jì)工具。

2022-11-01 09:23:39 3201

3201 Vivado是Xilinx推出的可編程邏輯設(shè)備(FPGA)軟件開(kāi)發(fā)工具套件,提供了許多TCL命令來(lái)簡(jiǎn)化流程和自動(dòng)化開(kāi)發(fā)。本文將介紹在Vivado中常用的TCL命令,并對(duì)其進(jìn)行詳細(xì)說(shuō)明,并提供相應(yīng)的操作示例。

2023-04-13 10:20:23 5477

5477 Stream、Flow是在電路描述里經(jīng)常用到的對(duì)象。

2023-05-15 17:36:11 1027

1027

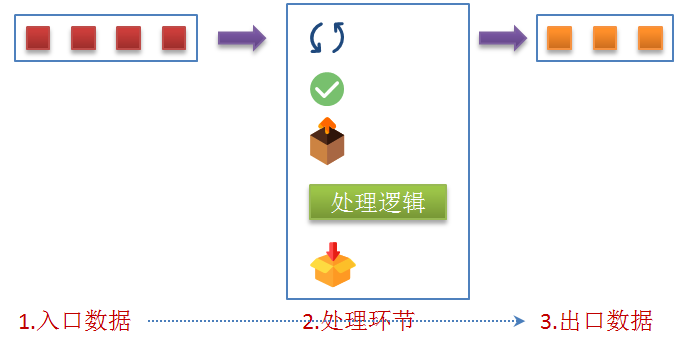

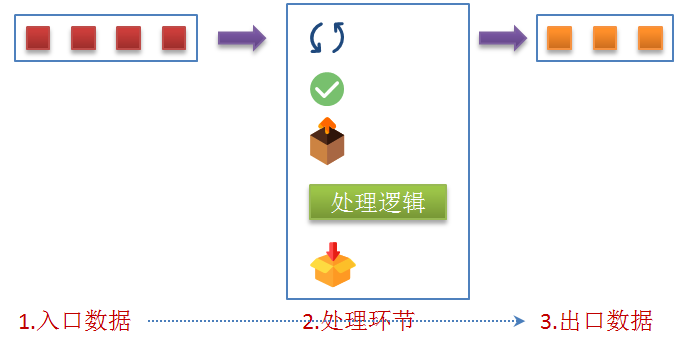

?我們都知道,傳統(tǒng)的處理中,每一步我們都需要通過(guò)循環(huán)控制,邏輯控制,解包,重新裝箱這些工作。 非生產(chǎn)線(xiàn)示意處理圖 這些步驟讓我們的程序的業(yè)務(wù)邏輯支離破碎,經(jīng)常處理數(shù)據(jù)類(lèi)的小伙伴尤為痛苦。幸運(yùn)的是,Java8為我們引入了Stream,使用Stream后我們只關(guān)注數(shù)據(jù)處理

2023-10-11 15:45:13 962

962

電子發(fā)燒友網(wǎng)站提供《基于TouchGFX的智能手表設(shè)計(jì) —MVP 架構(gòu)下的邏輯設(shè)計(jì).pdf》資料免費(fèi)下載

2024-01-05 11:21:38 1

1 電子發(fā)燒友網(wǎng)站提供《數(shù)字電路與邏輯設(shè)計(jì).ppt》資料免費(fèi)下載

2024-03-11 09:21:44 12

12 電子發(fā)燒友網(wǎng)站提供《基于VHDL的組合邏輯設(shè)計(jì).ppt》資料免費(fèi)下載

2024-03-11 09:23:29 2

2 嵌入式系統(tǒng)中常用的總線(xiàn)種類(lèi)繁多,它們各自具有不同的特點(diǎn)和應(yīng)用場(chǎng)景。以下將詳細(xì)介紹幾種嵌入式開(kāi)發(fā)中常用的總線(xiàn),包括UART、I2C、SPI、RS-232、RS-485、CAN以及USB等,每種總線(xiàn)將從其定義、特點(diǎn)、工作原理、應(yīng)用場(chǎng)景等方面進(jìn)行闡述。

2024-09-10 11:34:35 1977

1977

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論