阻塞與非阻塞賦值 首先從名字上理解,阻塞賦值即賦值沒完成,后邊的語句將無法執行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續程序的執行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看

2017-09-19 18:32:43 14061

14061 來源:《Verilog數字系統設計(夏宇聞)》 阻塞和非阻塞賦值的語言結構是Verilog 語言中最難理解概念之一。甚至有些很有經驗的Verilog 設計工程師也不能完全正確地理解:何時使用非阻塞

2021-08-17 16:18:17 7048

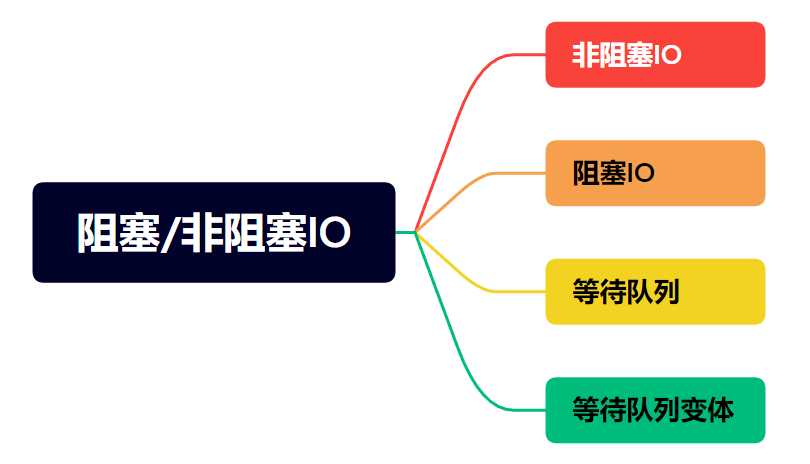

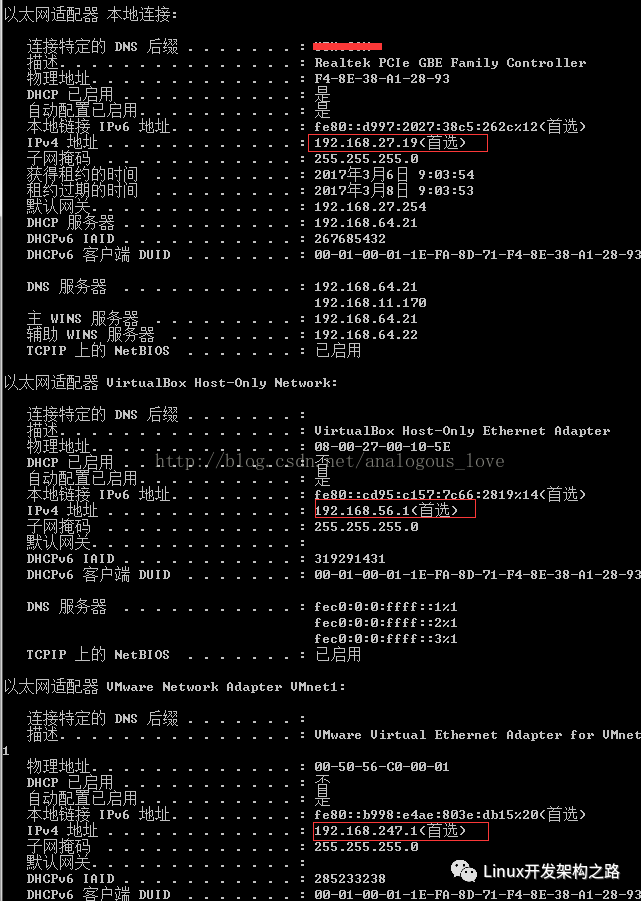

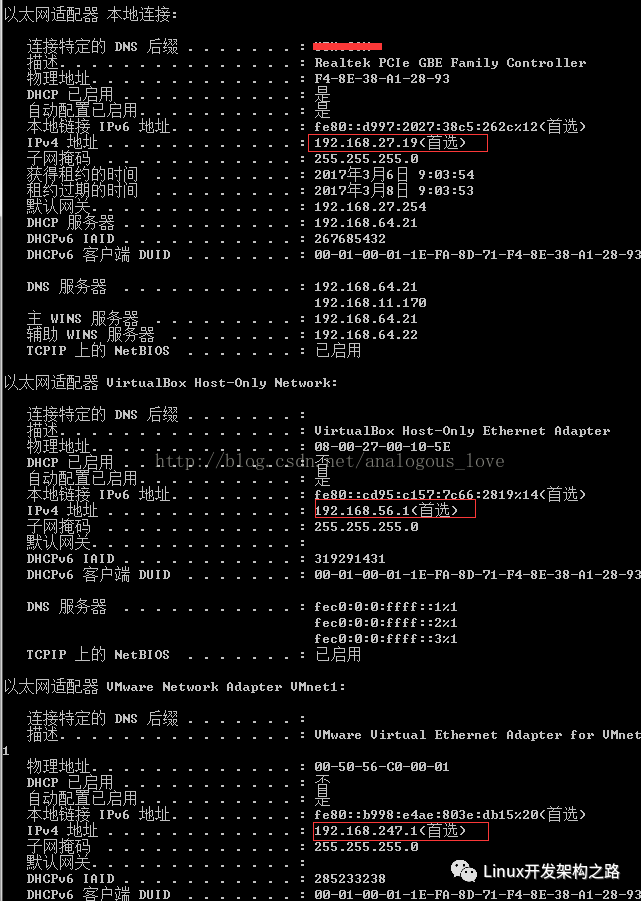

7048 在應用程序中,使用open函數打開一個`/dev`目錄下的一個設備文件時,默認是以阻塞的方式打開。

2023-06-12 16:22:12 1351

1351

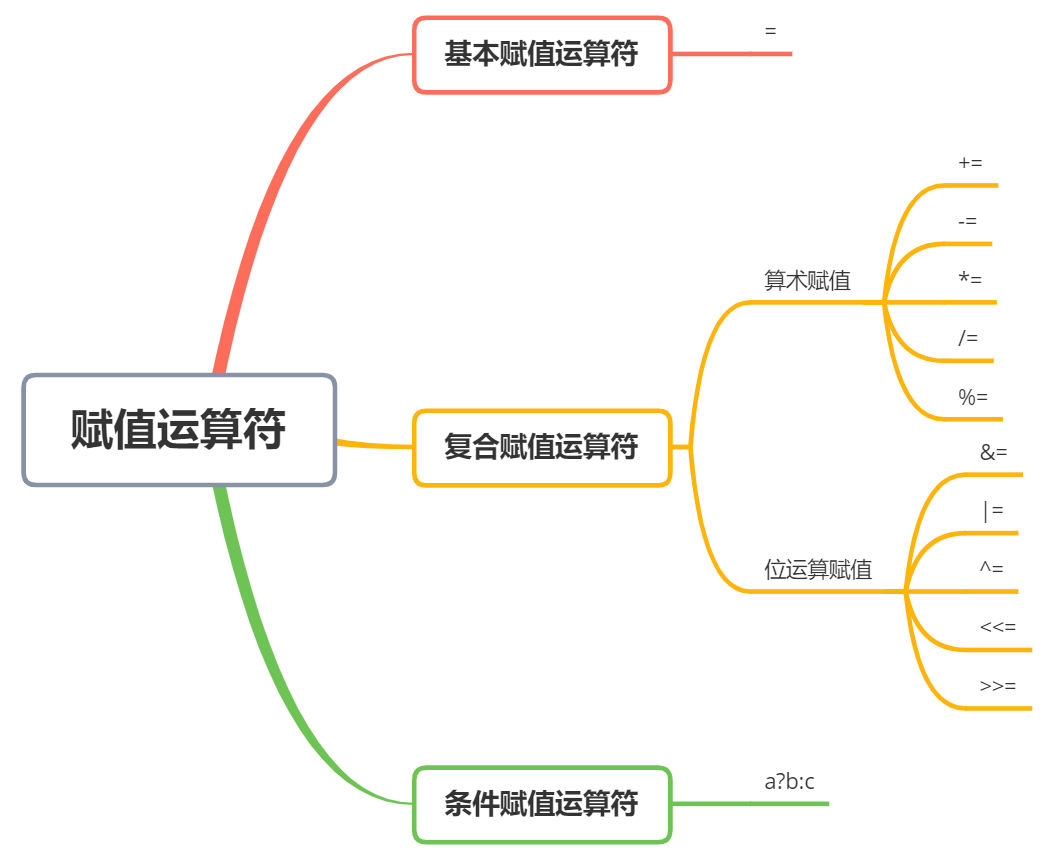

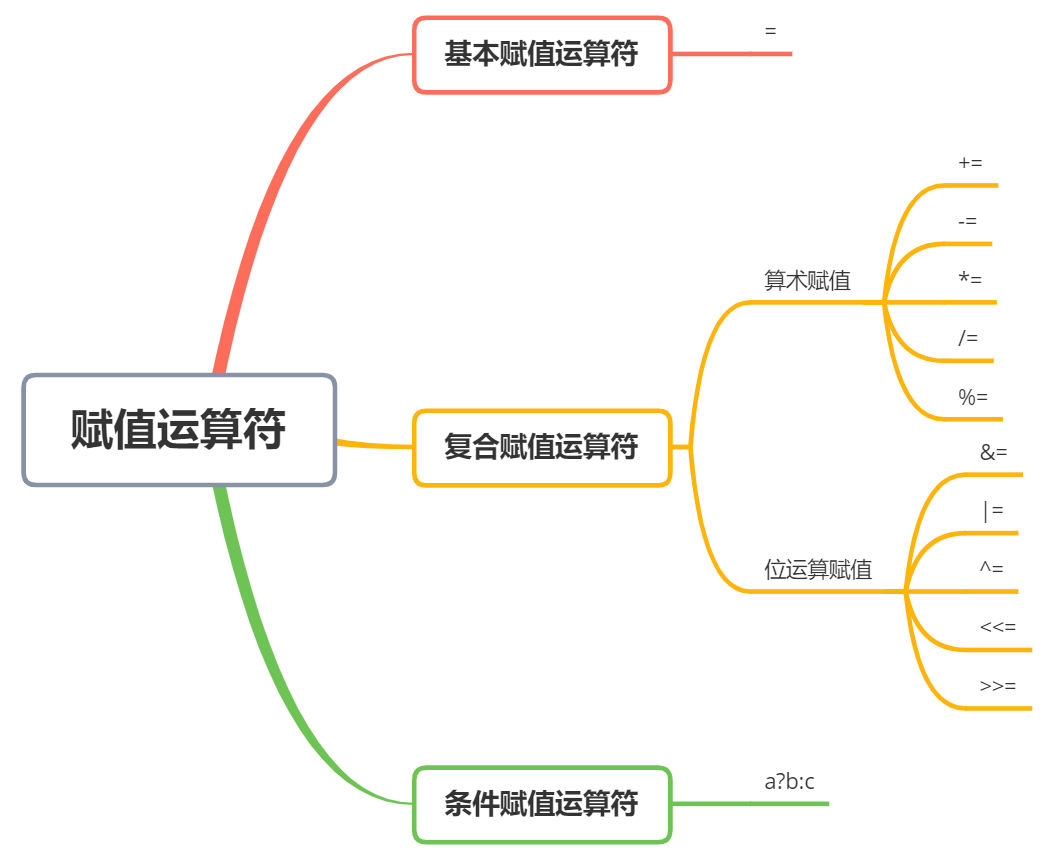

在C語言中,賦值運算符用于將一個值賦給變量。

2023-08-18 16:38:13 2890

2890

本文詳細闡述了在一個testbench中,應該如何使用阻塞賦值與非阻塞賦值。首先說結論,建議在testbench中,對時鐘信號(包括分頻時鐘)使用阻塞賦值,對其他同步信號使用非阻塞賦值。

2025-04-15 09:34:24 1092

1092

阻塞賦值左式延時實驗的設計,適合新手學習參考

2023-09-22 07:12:59

本文通過Verilog事件處理機制,詳細討論了阻塞與非阻塞賦值的區別、聯系及其應用示例。

2021-05-10 06:59:23

//處理按鍵標志位always @(posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) key_flag[1:0]

2019-05-15 23:20:39

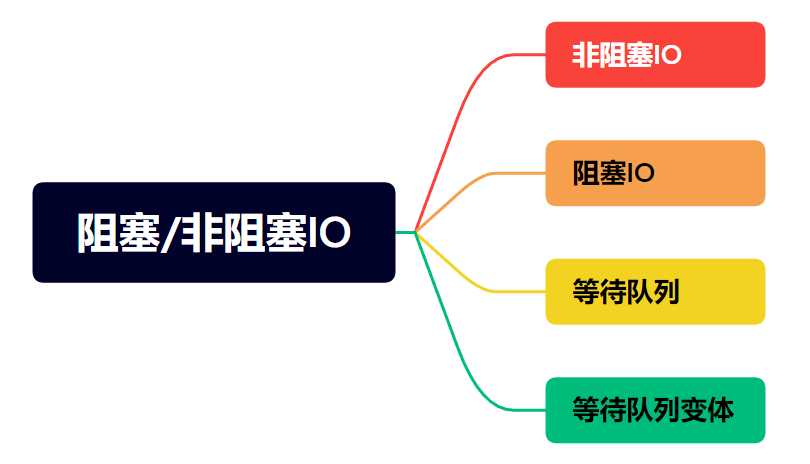

里面,因為硬件資源獲得的同時往往伴隨著一個中斷。 注意:驅動程序需要提供阻塞(等待隊列,中斷)和非阻塞方式(輪詢,異步通知)訪問設備。 休眠(被阻塞)的進程處于一個特殊的不可執行狀態。這點非常重要,否則

2018-07-09 08:19:59

語句的執行,延遲后才執行賦值,這種賦值語句是不可綜合的,在需要綜合的模塊設計中不可使用這種風格的代碼。 非阻塞賦值操作符用小于等于號(即

2018-07-03 10:23:19

語句的執行,延遲后才執行賦值,這種賦值語句是不可綜合的,在需要綜合的模塊設計中不可使用這種風格的代碼。 非阻塞賦值操作符用小于等于號(即

2018-07-09 05:08:55

本帖最后由 eehome 于 2013-1-5 10:05 編輯

非阻塞賦值容易錯語法點討論請教下大家!我發現光盤里的例程有一段是這樣子的:always @(dac_sta

2012-12-22 09:53:14

嗨!我不明白非阻塞分配是如何按順序或并行執行的?永遠@(posedge clk)開始x = 2;y = x;結束VS永遠@(posedge clk)叉子x = 2;y = x;加入VS賦值x = 2

2019-04-22 10:02:08

非阻塞式如何讀取矩陣按鍵?

2022-01-17 08:17:56

1,在阻塞賦值中,說是前邊賦值阻塞后邊賦值,但是看波形明明是同時變化,這是為什么?2,在if ,else if, else語句中說是順序執行,是時鐘跳一個周期判斷一次嗎,還是同時判斷,如果是同時判斷為什么說是順序執行?3,是組合邏輯中用=,非組合邏輯中用

2019-05-29 01:09:27

Verilog的兩個誤區:使用Reg類 型還是Net類型:Reg類 型只在過程塊中被賦值;而Net類型則在過 程塊外面被賦值或者驅動.阻塞賦值和非阻塞賦值:Verilog中競爭發生的條件:兩個或多個

2019-03-26 08:00:00

Verilog阻塞和非阻塞原理分析在Verilog語言最難弄明白的結構中“非阻塞賦值”要算一個。甚至是一些很有經驗的工程師也不完全明白“非阻塞賦值”在仿真器(符合IEEE標準的)里是怎樣被設定執行

2009-11-23 12:02:57

Verilog中阻塞賦值與非阻塞賦值的區別

2020-12-30 06:22:29

[table][tr][td] Verilog中有兩種為變量賦值的方法。一種叫做連續賦值,另一種叫做過程賦值。過程賦值又分為阻塞賦值和非阻塞賦值。阻塞性賦值使用“=”為變量賦值,在賦值結束前不可以進行其他操作,在賦值結束之后繼續后面的操作。這個過程就好像阻斷了程序的運行。非阻塞賦值使用“

2018-07-03 03:06:04

圖一圖二圖三圖四最近寫了一個16位二級流水線加法器,并進行了一下仿真。發現在always塊中采用阻塞賦值(=)和非阻塞賦值(

2016-09-09 09:18:13

時,dreg還是變成了areg這樣不就是延時3個時鐘周期了嗎?為什么不是這樣呢?另外,阻塞型賦值語句,規定是,順序執行語句,每種狀態一個接一個執行,非阻塞型賦值語句,規定是,并行賦值語句,當執行語句時同事計算

2017-09-20 15:10:01

`阻塞與非阻塞賦值首先從名字上理解,阻塞賦值即賦值沒完成,后邊的語句將無法執行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續程序的執行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看

2017-04-05 09:53:11

一般情況下串口通信中read()函數都是阻塞的。當然也可以通過設置文件等方法把串口設為非阻塞的。這里就有一個問題,當串口設置為阻塞狀況下,如果讀不到數據程序應該掛起。這種所謂的讀不到數據是指讀不到

2011-07-14 15:57:26

剛學verilog,試了一下非阻塞賦值,代碼如下, 很簡單module test(clk,in,out);input clk;input in;output reg out;always @(posedge clk)out

2012-10-30 09:20:14

這個是非阻塞賦值,b的值為0,仿真結果也是0module TOP(input clk,input rst,output reg b );reg a,c;always@(posedge clk or negedge rst)beginif(~rst)begina

2015-09-13 15:55:05

語句完成執行;? 非阻塞性過程賦值:對目標的賦值是非阻塞的(因為時延),但可預定在將來某個時間發生。阻塞性過程賦值用操作符“=”完成,例如下面的實例:always@ (A or B or Cin

2018-09-26 09:16:55

阻塞賦值與非阻塞賦值原理分析實驗目的:掌握阻塞賦值與非阻塞賦值的區別實驗平臺:無實驗原理:阻塞賦值,操作符為“=”,“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后

2016-12-25 01:51:24

:1) 在賦值時刻開始時,計算非阻塞賦值RHS表達式。2) 在賦值時刻結束時,更新非阻塞賦值LHS表達式。 這段代碼在posedge clk到來時,計算所有的RHS(Right Hand Side)的值

2016-11-03 20:26:38

的賦值語句會阻斷其后語句的正常執行,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。而且阻塞賦值可以看成是一步完成的,即:計算等號右邊的值并同時賦給左邊變量。非阻塞賦值,操作符為“

2020-02-24 20:09:13

阻塞與非阻塞作者:小黑同學一、 概述1、阻塞賦值對應的電路往往與觸發沿沒有關系,只與電平的變化有關系。阻塞賦值符號“=”。2、非阻塞賦值對應的電路結構往往與邊沿觸發有關系,只有在觸發沿時才有可能發生賦值的情況。非阻塞賦值符號“

2020-04-24 14:49:45

立即學習>>夢翼師兄FPGA培訓(純視頻),手把手帶你入門FPGA寫在前面的話開發過程中,我們用的最多的恐怕就是賦值語句了,我們常用的賦值方式有兩種:阻塞賦值和非阻塞賦值。夢翼師兄剛開始

2019-12-22 14:21:37

,主要通過簡單的例子對比了Verilog語法中阻塞賦值和非阻塞賦值的區別,通過證明非阻塞賦值多種賦值順序生產電路的唯一性,與非阻塞賦值多種賦值書序生成電路的不確定性,來展示使用非阻塞賦對設計可預測性

2015-09-24 14:02:15

設計③ 如何給端口選擇正確的數據類型④ Verilog語言中latch的產生⑤ 組合邏輯反饋環⑥ 阻塞賦值與非阻塞賦值的不同⑦ FPGA的靈魂狀態機⑧ 代碼風格的重要性[hide][/hide]

2016-08-17 05:56:55

什么是Verilog HDL阻塞賦值?主要應用在哪些方面?

2019-08-02 06:22:43

@ (posedge GlobalClk)RegC = RegB;由于過程性賦值立即發生,即沒有任何時延,所以根據首先執行哪一條always語句,RegC取不同的值,這就產生了競爭。書上說使用非阻塞性賦值可以避免產生競爭狀態,為什么??求助...

2013-11-07 10:16:34

我打開這個串口的時候沒有設置非阻塞的標志,應該是默認阻塞的吧,但是上位機不向串口發送東西,也就是read沒有讀到東西的時候下面的printf還是會一直打印。我理解的阻塞就是程序一直等待在阻塞的地方,是不是我理解的有問題

2017-03-15 16:51:06

完成時刻,即把 RHS 賦值給 LHS 的時刻,它才允許別的賦值語句的執行。非阻塞賦值操作符用小于等于號 (即

2013-10-28 15:44:13

同步與異步,阻塞與非阻塞的區別

2021-01-26 06:12:37

)中,\"<=\"作為非阻塞賦值的一部分。

verilog中,一個語法結構不可能同時允許“表達式”和“語句”,

如果某處可以出現表達式,那么就不允許出現語句;

如果

2023-08-08 09:32:07

使用Select實現非阻塞網絡編程

2021-03-30 07:34:03

用的verilog hdl。always塊里的每個賦值語句間,有延遲的嗎?如果有延遲是多大?還有非阻塞語句是并行執行的還是說在always塊結束的時候再一句一句執行?之前一直搞C語言,到這里好多東西不習慣

2018-05-15 15:07:37

Verilog HDL語言中存在兩種賦值語言:● 非阻塞型賦值語句● 阻塞型賦值語句1. 非阻塞型語句以賦值操作符“

2015-03-22 10:23:44

使用 _IT 函數轉移到一個非阻塞系統。只是將傳輸命令從 HAL_I2C_Master_Transmit 更改為 HAL_I2C_Master_Transmit_IT 突然將我所有的結果變成了屏幕上的亂碼,而不是像我以前那樣漂亮的文本。我需要做什么才能從阻塞 I2C 命令變為非阻塞 I2C 命令?

2023-02-06 06:00:18

本文針對Java NIO 的特性做出分析與闡述,對網絡應用中阻塞通信與非阻塞通信、NIO的非阻塞工作機制以及網絡通信中非阻塞套接字的實現等問題進行了研究和探討,提出了系統地

2009-08-10 10:15:22 18

18 非阻塞賦值

2010-02-09 10:14:52 41

41 阻塞和非阻塞語句作為verilog HDL語言的最大難點之一,一直困擾著FPGA設計者,即使是一個頗富經驗的設計工程師,也很容易在這個點上犯下一些不必要的錯誤。阻塞和非阻塞可以說是血脈相連,但是又有著本質的差別

2011-03-15 10:57:34 7239

7239 原標題:Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill! ATTN:所有括號內外注為理解方便或有疑問的地方,原文里并沒有。所有翻譯都是為遵循共同進步的理想但并沒有去努力得

2011-03-29 16:25:53 0

0 本文通過Verilog事件處理機制,詳細討論了阻塞與非阻塞賦值的區別、聯系及其應用示例。由本文可知,阻塞與非阻塞賦值靈活多變,底層實現也差異甚大。因而在數字電路設計時,依據

2011-08-28 17:59:19 862

862

VerilogHDL 中,有兩種過程賦值方式,即阻塞賦值(blocking)和非阻塞賦值(nonblocking)。阻塞賦值執行時,RHS(righthandstatement)估值與更新LHS(lefthandstatement)值一次執行完成,計算完畢,立即更新。

2012-05-23 09:55:51 1598

1598

這是一個很好的學習阻塞和非阻塞的資料,對于FPGA的學習有很大幫助。

2016-04-22 11:00:45 11

11 學verilog 一個月了,在開發板上面寫了很多代碼,但是始終對一些問題理解的不夠透徹,這里我們來寫幾個例子仿真出阻塞和非阻塞的區別

2017-02-11 03:23:12 1730

1730 在一開始學到阻塞和非阻塞的時候,所被告知的兩者的區別就在于阻塞是串行的,非阻塞是并行的。但是雖然知道這個不同點,有些時候還是很難真正區分用兩者電路的區別,下載資料內以一個簡單的串行流水線寄存器為例進行了分析。

2017-09-16 09:34:07 4

4 《Linux設備驅動開發詳解》第8章、Linux設備驅動中的阻塞與非阻塞IO

2017-10-27 11:35:12 9

9 設計背景: 阻塞 (=)和非阻塞(=)一直是在我們FPGA中討論的問題,資深的學者都是討論的是賦值應該發生在上升下降沿還是在哪里,我們在仿真中看的可能是上升下降是準確的,但是在時間電路中這就

2018-05-31 11:40:14 7425

7425

本文檔的主要內容詳細介紹的是PHP中傳值賦值和引用賦值的詳細資料詳解。

2019-03-06 17:04:32 5

5 本文檔的主要內容詳細介紹的是FPGA的視頻教程之Verilog中阻塞與非阻塞的詳細資料說明。

2019-03-26 17:16:31 2

2 對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2020-01-30 17:41:00 22571

22571 1、阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。而且阻塞賦值可以看成是一步完成的,即:計算等號右邊的值并同時賦給左邊變量。

2020-04-25 08:00:00 0

0 阻塞賦值對應的電路往往與觸發沿沒有關系,只與輸入電平的變化有關系。非阻塞賦值對應的電路結構往往與觸發沿有關系,只有在觸發沿時才有可能發生賦值的情況。

2020-06-17 11:57:41 12065

12065

如何區分VerilogHDL語言連續賦值與過程賦值方式

2020-07-20 09:16:29 7047

7047

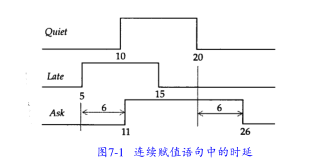

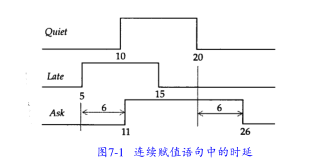

數據流模型化 本章講述Verilog HDL語言中連續賦值的特征。連續賦值用于數據流行為建模;相反,過程賦值用于(下章的主題)順序行為建模。組合邏輯電路的行為最好使用連續賦值語句建模。 7.1 連續

2021-03-05 15:38:21 4839

4839

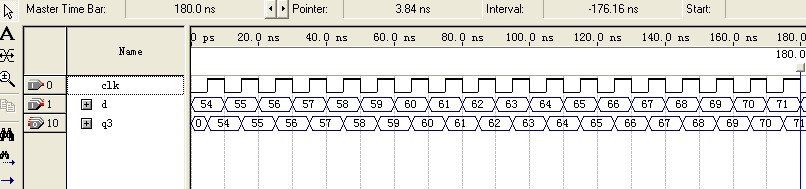

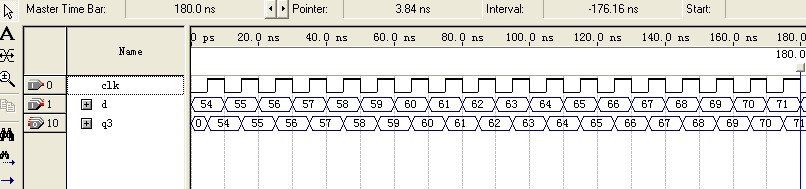

下面給出一個基于阻塞賦值和非阻塞賦值的多級觸發器級聯實例,要求將輸入數據延遲 3 個時鐘周期再輸出,并給出對應的 RTL 級結構圖和仿真結果。 (1)基于 D觸發器的阻塞賦值語句代碼如下

2021-05-08 14:47:05 2720

2720

阻塞賦值和非阻塞賦值的可綜合性 Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進程管理的術語。由于Verilog團隊是從C語言發展

2021-05-12 09:45:09 3264

3264

? 在Verilog中有兩種類型的賦值語句:阻塞賦值語句(“=”)和非阻塞賦值語句(“=”)。正確地使用這兩種賦值語句對于Verilog的設計和仿真非常重要。 Verilog語言中講的阻塞賦值與非

2021-12-02 18:24:36 7318

7318

由于賦值語句有阻塞賦值和非阻塞賦值兩類,建議讀者使用阻塞賦值語句“=”,原因將在“阻塞賦值和非阻塞賦值”中(現在還沒有寫)進行說明。

2022-03-15 10:40:20 2843

2843 “ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括塊語句、阻塞賦值和非阻塞賦值 以及結構說明語句(initial, always, task, function)。”

2022-03-15 12:19:31 2954

2954 Verilog HDL的賦值語句分為阻塞賦值和非阻塞賦值兩種。阻塞賦值是指在當前賦值完成前阻塞其他類型的賦值任務,阻塞賦值由=來完成;非阻塞賦值在賦值的同時,其他非阻塞賦值可以同時被執行,非阻塞賦值由《=來完成。

2022-03-15 13:53:08 3700

3700 如例6.1所述,在多個“Always” 進程中使用阻塞賦值。程序塊“Always”在時鐘的正邊緣觸發,綜合器推斷時序邏輯。如前所述,所有阻塞賦值都在活動隊列中進行計算和更新。讀者請參閱之前分享的分層事件隊列一文。

2022-09-06 09:44:02 4895

4895 阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。

2022-12-19 16:49:28 9356

9356 使用邏輯門和連續賦值對電路建模,是相對詳細的描述硬件的方法。使用過程塊可以從更高層次的角度描述一個系統,稱作行為級建模(behavirol modeling)。 1. 過程賦值 阻塞賦值和非阻塞賦值

2023-03-17 21:50:05 1282

1282 當元素的數據類型和數組界限(最低和最高的可能的數組索引)相匹配時,能夠將一個完整數組賦值給另一個數組。如果是這樣,在賦值符后指定數組的標識符。下面的賦值是有效的:

2023-04-10 11:46:59 1500

1500 對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2023-06-01 09:21:57 2709

2709 阻塞通信(Blocking Communication):當進行阻塞通信時,調用者在發起一個I/O操作后會被阻塞,直到該操作完成返回才能繼續執行后續代碼。

2023-06-15 17:32:21 7290

7290 關于阻塞函數和非阻塞函數在CAN和LIN相關的開發庫里,不可避免的會出現“收”和“發”的函數。如何快速有效的處理數據,是開發中重要的事項。

2022-07-05 14:38:43 2031

2031

今天給大家普及一下阻塞賦值和非阻塞賦值的相關知識

2023-07-07 14:15:12 3014

3014

前不久一位朋友發來一道驗證題,雖然題目不是很復雜,但是琢磨了下感覺其中需要掌握的內容還是很多的,正所謂麻雀雖小五臟俱全。下面將對此題涉及的一些內容進行挖掘和示例,與大家分享下。

2023-08-31 15:24:29 1832

1832

”=“阻塞賦值與”<=“非阻塞賦值是verilog語言中的兩種不同的賦值方式,下面將對兩種賦值方式進行比較。方便進行理解和使用。

2023-09-12 09:06:15 1790

1790

阻塞 IO 模型 在Linux ,默認情況下所有的 socket 都是阻塞的,一個典型的讀操作流程如圖所示。 阻塞和非阻塞的概念描述的是用戶線程調用內核 IO 操作的方式:阻塞是指 IO 操作需要

2023-10-08 17:16:51 1570

1570

阻塞就是外部有阻塞干擾信號的時候,設備還可以正常運行。一般分為帶內阻塞和帶外阻塞,由于直放站都是做寬帶設備,一般只提帶外阻塞。

2023-10-10 11:22:37 3968

3968 由于網絡編程涉及很多細節和技巧,一直想寫篇文章來總結下這方面的心得與經驗,希望對來者有一點幫助,那就善莫大焉了。 一、非阻塞的的connect()函數如何編寫 我們知道用connect()函數默認

2023-11-11 16:23:29 2725

2725

Verilog是一種硬件描述語言,用于設計和模擬數字電路。在Verilog中,同步和異步是用來描述數據傳輸和信號處理的兩種不同方式,而阻塞賦值和非阻塞賦值是兩種不同的賦值方式。本文將詳細解釋

2024-02-22 15:33:04 2897

2897 什么是阻塞和非阻塞?我們就用管道的讀寫來舉例子。

2024-03-25 10:04:13 1159

1159 在計算機編程中,socket 是一種通信端點,用于在網絡中進行數據傳輸。Socket 可以是阻塞的或非阻塞的,這兩種模式在處理數據傳輸時有不同的行為。 阻塞模式(Blocking Mode) 在阻塞

2024-08-16 11:13:43 1721

1721 在網絡編程中, socket 是一個非常重要的概念,它提供了一個抽象層,使得開發者可以不必關心底層的網絡通信細節。 socket 編程中的阻塞與非阻塞模式是兩種不同的操作方式,它們對程序的響應性

2024-11-01 16:13:15 1155

1155

電子發燒友App

電子發燒友App

評論