00

2026年4月2日,美國國會兩黨議員聯(lián)手拋出了一份名為《硬件技術(shù)多邊協(xié)調(diào)管制法案》的草案。這份法案直接砍向了荷蘭ASML公司的命脈——它要求全面禁止向中國出口所有深紫外浸沒式光刻機(jī),無論新舊型號,徹底堵死中國獲取成熟制程(14nm及以下)核心設(shè)備的通道。更絕的是,法案給了日本、荷蘭等盟友150天最后通牒,要求它們必須同步實(shí)施同等管制。

法案明確將中芯國際、長江存儲、長鑫存儲、華虹半導(dǎo)體、華為五家企業(yè)列為“受管制設(shè)施”,不僅禁止出口新設(shè)備,連現(xiàn)有設(shè)備的維修、校準(zhǔn)、軟件更新和技術(shù)支持都要一刀切斷。這意味著這些企業(yè)花數(shù)十億美元買來的生產(chǎn)線,一旦出現(xiàn)故障,可能就真的變成了一堆廢鐵。

另一個消息,菊廠ST950PR芯片,獲得世界級AI大廠批量采購的訂單,預(yù)計年出貨量75萬片。其中有一個重要原因是菊廠對標(biāo)CUDA,開發(fā)了CANN并升級到了CANN NEXT,且在去年完全開源,突破了CUDA框架兼容和算子適配的瓶頸。當(dāng)芯片的硬件實(shí)力能匹配客戶需求(單卡算力是英偉達(dá)H20的2.87倍,HBM容量112GB,比H20多16%,多模態(tài)生成速度提升60%),競爭力自然會體現(xiàn)出來(昨天咱大A整體大漲,特別是算力板卡表現(xiàn)優(yōu)異,也算是競爭力的一種體現(xiàn)吧)。

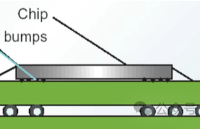

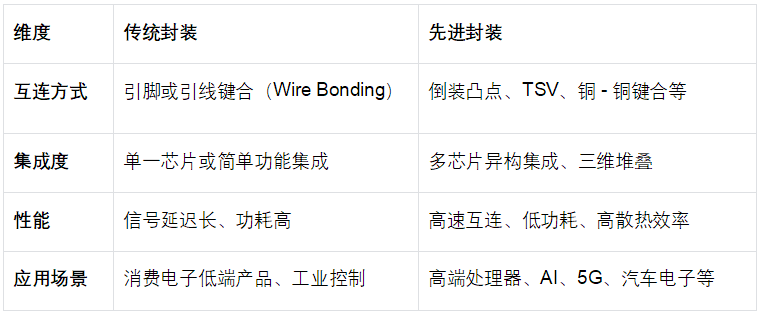

芯片設(shè)計完成后,還要經(jīng)過制造,封裝、部署,服務(wù)才能變成客戶需要的算力。因?yàn)橹瞥滔拗疲?50PR芯片采用的是芯片合封技術(shù),即把多顆芯片拼成一顆來用,但拼的過程非常復(fù)雜,芯片之間需要高速通信,中間要堆疊HBM內(nèi)存顆粒,整個封裝體的散熱,信號完整性,良率控制,要求比傳統(tǒng)封裝高出好幾個量級,技術(shù)難度極高。常規(guī)數(shù)據(jù)表明,950PR的芯片功耗600W,比H20高了50%,運(yùn)行中對散熱要求顯著提升。

01

僅僅提升液冷的熱交換能力始終存在散熱瓶頸(請參考文章:液冷技術(shù)與方案評價),要想提高整體系統(tǒng)的性能,首先要對芯片做科學(xué)的熱設(shè)計。傳統(tǒng)的芯片熱設(shè)計方法依賴熱電偶與紅外熱成像,在現(xiàn)代高性能芯片(GPU/CPU/HBM)與先進(jìn)封裝、功率器件中存在明顯局限性,而比如T3Ster,CX等SISO的瞬態(tài)熱測試設(shè)備,在2.5D/3D、HBM、Chiplet、TSV等先進(jìn)封裝中,其一維、單熱源、線性、冷板邊界的核心假設(shè)與復(fù)雜三維熱場嚴(yán)重不匹配(請參考文章:先進(jìn)封裝的瞬態(tài)熱測試,等效熱導(dǎo)率提取及模型校準(zhǔn)),即使把SISO瞬態(tài)熱測試設(shè)備和紅外,熱電偶等多個工具組合使用,也無法全部滿足應(yīng)用的要求(實(shí)際工程中,這可能是主要解決方案)。

先進(jìn)封裝(2.5D/3D、Chiplet、HBM集成)的熱設(shè)計之所以極度復(fù)雜,本質(zhì)是因?yàn)椋簾嵩磸膯我黄矫孀優(yōu)槊芗Ⅲw多熱源耦合,熱路徑被大幅拉長并由大量低熱導(dǎo)界面組成,同時伴隨超高功耗密度、嚴(yán)苛溫度敏感器件(HBM)、多物理場強(qiáng)耦合、瞬態(tài)動態(tài)負(fù)載等多重約束疊加。必須對結(jié)溫進(jìn)行精確表征,在微小空間內(nèi)實(shí)現(xiàn)高精度、多維度、全瞬態(tài)的熱管控,因此難度遠(yuǎn)超傳統(tǒng)封裝,熱設(shè)計已成為核心挑戰(zhàn)。

鑒于先進(jìn)封裝多熱源強(qiáng)耦合,功率密度高以及極端的瞬態(tài)特性等工況的復(fù)雜性,工程實(shí)踐中,需要基于MIMO高精度瞬態(tài)測試和仿真的深度融合(請參考文章:先進(jìn)封裝的瞬態(tài)熱測試,等效熱導(dǎo)率提取及模型校準(zhǔn)),構(gòu)建先進(jìn)封裝芯片瞬態(tài)工況的高精度仿真模型。從設(shè)計的初期就要開始做相應(yīng)的熱設(shè)計,并不斷的迭代,優(yōu)化,驗(yàn)證。

02

MIMO的瞬態(tài)熱測試是為了準(zhǔn)確提取散熱路徑的信息,其測試方法相對于SISO的瞬態(tài)熱測試設(shè)備,會稍微復(fù)雜一點(diǎn)。

以雙熱源的芯片為例,我們詳細(xì)展示一下其實(shí)際的操作過程,以及如何結(jié)合應(yīng)用繁星工具預(yù)測結(jié)溫。

SISO的瞬態(tài)熱測試執(zhí)行的是JESD 51-14的標(biāo)準(zhǔn)【請參考文章:熱測試(二)——瞬態(tài)熱測試與結(jié)構(gòu)函數(shù)】,而MIMO的瞬態(tài)熱測試,現(xiàn)行還沒有相應(yīng)標(biāo)準(zhǔn),我們先定義幾個參數(shù)。

Zth1,1:芯片1作為熱源,芯片1的瞬態(tài)熱阻抗曲線;

Zth2,1 :芯片1作為熱源,芯片2的瞬態(tài)熱阻抗曲線;

Zth1,2 :芯片2作為熱源,芯片1的瞬態(tài)熱阻抗曲線;

Zth2,2 :芯片2作為熱源,芯片2的瞬態(tài)熱阻抗曲線。

其中Zth1,1和Zth2,2是熱源自身的散熱路徑,這種測試方法和SISO的瞬態(tài)熱測試完全相同,而其中Zth2,1和Zth1,2是互熱阻瞬態(tài)響應(yīng)曲線,其定義是某測量點(diǎn)不發(fā)熱,但受到其他熱源的影響的散熱路徑的相關(guān)信息,下標(biāo)的前面一個表示的是溫度測量點(diǎn),后面一個表示的是熱源點(diǎn)。

具體測試方式如下:

1、通過預(yù)檢,選擇和確定每個熱源的測試用小電流I小1和I小2(不會引起被測器件發(fā)熱),測量每個熱源的K系數(shù);

2、根據(jù)工作時的大致功率參數(shù),分別確定加熱電流I大1和I大2(理論上散熱路徑是時不變系統(tǒng),和功率無關(guān),但實(shí)際上由于材料物性,接觸熱阻等,都可能因?yàn)楣β什煌煌虼嘶趯?shí)際工況時的功率去做瞬態(tài)熱測試,其數(shù)據(jù)應(yīng)用性更高);

3、對兩個熱源在電路上做物理隔離,用兩個完全隔離的測試通道,連接不同的熱源,形成兩個完全隔離的加熱回路和測試回路;

4、給熱源1施加I大1,電子被測器件開始發(fā)熱,溫度逐步升高,隨著溫度梯度(器件溫度減去環(huán)境溫度)增加,其散熱功率也不斷增加,直到加入功率等于散熱功率,系統(tǒng)處于第一次平衡狀態(tài);

5、將I大1關(guān)閉,同步分別快速切換至I小1和I小2,切換時間小于等于1us,在這里有一個技術(shù)難點(diǎn),既在I大1和I小2之間的切換時間也要小于等于1us,這便是SISO和MIMO設(shè)備之間的區(qū)別,SISO設(shè)備只能做到測試通道內(nèi)微秒級同步,而MIMO設(shè)備可以做到測試通道之間微秒級同步;

6、分別用1us的采樣速度,基于連續(xù)變頻采樣,對熱源1和熱源2做連續(xù)采樣,直到達(dá)到第二個熱平衡狀態(tài)(器件溫度等于環(huán)境溫度),使用第一步測出的K系數(shù)即可計算出各個熱源的瞬態(tài)溫度,從計算出Zth1,1和Zth2,1;

7、將熱源切換成熱源2和I大2,重復(fù)步驟4-6,即可計算出Zth1,2和Zth2,2。

MIMO的瞬態(tài)熱測試設(shè)備相對于SISO,有兩個重要的技術(shù)指標(biāo):

?各測量通道為互相獨(dú)立,完全隔離;

?測量通道之間可以做到微秒級同步。

如果通道不隔離,熱源之間由于熱串?dāng)_的問題,無法計算每個熱源的準(zhǔn)確功率,而準(zhǔn)確的功率是計算熱阻的前提。通道之間微秒級同步是為了保證瞬態(tài)溫度測量的有效性,從而得到精確的熱物性參數(shù)。基于MIMO瞬態(tài)熱測試設(shè)備的測試數(shù)據(jù),我們可以用繁星工具中的瞬態(tài)結(jié)溫計算工具,去計算芯片實(shí)時工況中,每個溫度測量點(diǎn)的結(jié)溫。(計算的理論基礎(chǔ),請參考文章:如何用卷積工具準(zhǔn)確預(yù)測結(jié)溫)

03

從2.1版本開始,以前的卷積工具更名為瞬態(tài)結(jié)溫計算工具,2.1版的繁星還沒有正式發(fā)布,主要是基于軟件GUI的改進(jìn)。

左邊是工具選擇區(qū)域,左邊是工具操作區(qū)域。可以設(shè)置工具使用的邊界條件,比如上圖,設(shè)定芯片的工作溫度為25度,計算的時間步長為0.1秒,點(diǎn)擊熱耦合矩陣,就會跳出對話框,輸入功耗,自Zth,或者互Zth,等信息,除了Zth,軟件也支持Forster模型和Cauer模型,在功耗區(qū)域,可以輸入P1,表示熱源1發(fā)熱,輸入P2,表示熱源2發(fā)熱,同時輸入兩個P1和P2,表示熱源共同發(fā)熱。

輸入功耗和Zth,點(diǎn)擊計算,數(shù)秒后,就能得到計算的結(jié)果,右圖就會顯示結(jié)溫的瞬態(tài)變化曲線,從圖表上看,當(dāng)熱源1工作時,芯片1最高結(jié)溫發(fā)生在75秒,ΔT為177.8°C(瞬態(tài)最高結(jié)溫為202.8),芯片2的最高結(jié)溫發(fā)生在75.2秒,ΔT為82.9°C(瞬態(tài)結(jié)溫為107.9)。

而雙熱源同時發(fā)熱時,芯片1最高結(jié)溫發(fā)生在74.97秒,瞬態(tài)最高結(jié)溫為262.7°C,芯片2的最高結(jié)溫發(fā)生在74.57秒,瞬態(tài)最高結(jié)溫為287.46°C。

如果在兩個熱源以外,還存在一個NTC/PTC或者熱電偶(Transfer Point),基于線性時不變系統(tǒng),我們可以用同樣的方法對瞬態(tài)結(jié)溫以及Transfer Point(需要先測量Transfer Point的Zth3,1和Zth3,2,功耗為零)的溫度做計算。我們或者可以嘗試以下應(yīng)用:

1、計算每個熱源對Transfer Point溫度增量的貢獻(xiàn)值;

2、溫度增量的總和,即是Transfer Point的實(shí)際的ΔT,而Transfer Point的溫度是可以實(shí)時讀取的,這可以驗(yàn)證模型的精度;

3、如果Transfer Point的溫度的計算值和實(shí)際值發(fā)生了比較大的差異(低出一定值),可能是水道的散熱能力或者其他重要散熱路徑發(fā)生了嚴(yán)重的故障;

4、穩(wěn)態(tài)工況下,當(dāng)每個熱源功率不變后,每個溫度增量的貢獻(xiàn)值也是確定的,即可得到各熱源貢獻(xiàn)值之間的比例關(guān)系,對比典型工況的功率分布和各自的溫度增量,從而可以通過Transfer Point的實(shí)時溫度,反推每個熱源的實(shí)時溫度。

5、這樣我們或許可以基于該種推算對相應(yīng)模塊做過溫保護(hù),或者設(shè)定相應(yīng)的控制策略,降額運(yùn)行,以保證系統(tǒng)的運(yùn)行安全;

6、可能還會產(chǎn)生其他新的有價值的應(yīng)用技術(shù),有待工程實(shí)踐進(jìn)一步探索。

關(guān)于Transfer Ponit的詳細(xì)典型應(yīng)用,請大家關(guān)注魯歐智造在4月16日下午線上的免費(fèi)技術(shù)專題《基于熱阻抗模型的高精度結(jié)溫計算方法研究》

歡迎業(yè)界專家蒞臨指導(dǎo)(掃碼即可報名,全免費(fèi))。

04

瞬態(tài)測試數(shù)據(jù)(瞬態(tài)熱阻抗曲線,結(jié)構(gòu)函數(shù))不僅僅只是用來計算結(jié)溫,通過校準(zhǔn)得到的高精度仿真模型,其溫度場的瞬態(tài)變化也可以和實(shí)物模型保持高度一致,這種專注于電子散熱的數(shù)字孿生技術(shù),可以很大程度上減低我們試錯的成本。

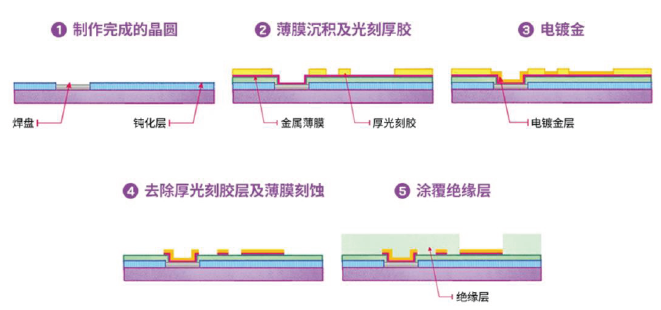

然而,在研發(fā)的初期階段,并無實(shí)際的樣品,熱設(shè)計的主要是架構(gòu)選型、Chiplet布局、中介層/ TSV /微凸點(diǎn)方案、散熱架構(gòu)初步定義等等,核心目標(biāo)是快速篩除不可行方案、量化熱瓶頸、建立全鏈路熱數(shù)字基線、提前鎖定可靠性邊界,避免后期流片/封裝由于熱問題無法解決而返工。

初期階段不追求極致精度,但必須解決4個不可妥協(xié)的熱問題,所有工具應(yīng)用都圍繞這4點(diǎn):

結(jié)溫可行性:設(shè)定結(jié)溫上限,比如GPU/CPU核心結(jié)溫≤105℃、HBM結(jié)溫≤95℃,無局部熱點(diǎn)超閾值;

熱耦合可控:GPU對HBM的熱串?dāng)_ΔT≤10℃,Chiplet間熱疊加不觸發(fā)降頻;

熱路徑無瓶頸:垂直/橫向布局合理,TSV /微凸點(diǎn)/中介層不成為致命熱點(diǎn);

可靠性初步設(shè)計:熱應(yīng)力、溫度循環(huán)、功率循環(huán)壽命滿足規(guī)格,無早期分層/凸點(diǎn)失效風(fēng)險。

在設(shè)計的初期階段,仿真結(jié)合繁星工具可以快速試錯,快速收斂,基于經(jīng)驗(yàn)或者高精度參數(shù)的熱仿真,可以對方案做初步驗(yàn)證,輸出:全封裝三維溫度云圖、各Die結(jié)溫分布、HBM通道溫度、熱點(diǎn)溫度、熱流密度分布等等,定位散熱瓶頸。

在研發(fā)的詳細(xì)設(shè)計階段,熱設(shè)計的核心目標(biāo)是定尺寸、定材料、定結(jié)構(gòu)、定工藝。必須解決:

結(jié)溫精準(zhǔn)可控:比如GPU/CPU熱點(diǎn)溫度≤105℃,HBM全程≤85–95℃,無局部過熱點(diǎn);

熱路徑完全打通:明確芯片→μbump→中介層→TSV→基板→冷板等各自材料對散熱的影響,消除熱瓶頸。

熱耦合與串?dāng)_量化:GPU對HBM的熱烘烤、Chiplet間互相加熱必須可控、可計算、可驗(yàn)證;

熱–力可靠性閉環(huán):微凸點(diǎn)、焊球、底部填充、中介層不出現(xiàn)應(yīng)力過載、疲勞失效;

熱數(shù)字孿生:建模等效參數(shù)泛化性良好,整體仿真誤差可控,實(shí)現(xiàn)虛擬空間探索,物理世界驗(yàn)證。

詳細(xì)設(shè)計階段,可以立足初步設(shè)計方案樣品(或者測試假片),用CXAI的瞬態(tài)熱測試和仿真結(jié)果做比對,進(jìn)行自動熱模型校準(zhǔn),從而提高仿真精度。用高精度的仿真模型,結(jié)合瞬態(tài)結(jié)溫計算工具,對芯片的設(shè)計方案做進(jìn)一步優(yōu)化,并通過壽命計算工具去預(yù)測產(chǎn)品的可靠性。總體流程如下圖所示:

設(shè)計方案完成后的樣品,通過CXAI可以精確的檢測芯片的每個熱源的散熱路徑。技術(shù)上可以輸出相應(yīng)的熱阻網(wǎng)絡(luò)模型(熱阻,雙熱阻等),BCI的熱模型(Delphi,Delphi-c,3D ROM),以及詳細(xì)熱模型。有了芯片的高精度參數(shù)和模型輸出,在板卡,整機(jī),數(shù)據(jù)中心等電子系統(tǒng)的整體熱設(shè)計中,下游企業(yè)可以大幅降低其研發(fā)的工作量,從而實(shí)現(xiàn)整個產(chǎn)業(yè)鏈的生態(tài)協(xié)同。

缺乏先進(jìn)制程,芯片的單體能力被限制,逼迫技術(shù)在其他提升算力的技術(shù)路徑尋求突破,從而建立了芯片拼接的能力——在微小的空間內(nèi),實(shí)現(xiàn)高速通信,實(shí)現(xiàn)信號、功率和熱設(shè)計的整體協(xié)同,多個芯片堆疊的算力并不差。更重要的是,我們獲得了基于新技術(shù)探索而沉淀出的方法論,因?yàn)橹瞥痰南拗瓶傆幸惶鞎黄疲碌闹瞥滔拢Y(jié)合芯片拼接技術(shù),反而可以建立在整體解決方案上的技術(shù)優(yōu)勢,未來的競爭,鹿死誰手,現(xiàn)在還沒有答案(其實(shí)我認(rèn)為答案很明顯了),讓我們拭目以待。

審核編輯 黃宇

-

芯片

+關(guān)注

關(guān)注

463文章

54337瀏覽量

468600 -

MIMO

+關(guān)注

關(guān)注

12文章

612瀏覽量

79731 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

559瀏覽量

1056

發(fā)布評論請先 登錄

臺積電美國芯片100%回臺封裝,先進(jìn)封裝成AI芯片瓶頸

半導(dǎo)體先進(jìn)封裝和傳統(tǒng)封裝的本質(zhì)區(qū)別

長電科技亮相先進(jìn)封裝開發(fā)者大會機(jī)器人與汽車芯片專場

先進(jìn)封裝的散熱材料有哪些?

先進(jìn)封裝時代,芯片測試面臨哪些新挑戰(zhàn)?

當(dāng)芯片變“系統(tǒng)”:先進(jìn)封裝如何重寫測試與燒錄規(guī)則

人工智能加速先進(jìn)封裝中的熱機(jī)械仿真

一文了解先進(jìn)封裝之倒裝芯片技術(shù)

突破!華為先進(jìn)封裝技術(shù)揭開神秘面紗

英特爾先進(jìn)封裝,新突破

Chiplet與先進(jìn)封裝設(shè)計中EDA工具面臨的挑戰(zhàn)

淺談先進(jìn)封裝芯片的熱設(shè)計

淺談先進(jìn)封裝芯片的熱設(shè)計

評論