SiC MOSFET芯片短路失效機理:基于 Sentaurus TCAD 的電-熱-力多物理場耦合仿真

1. 緒論:碳化硅功率器件在極端工況下的可靠性挑戰(zhàn)

在當今全球能源轉型的宏大背景下,第三代半導體材料碳化硅(SiC)憑借其卓越的物理特性,正迅速取代硅(Si)成為高壓、高頻及高溫應用領域的核心 。作為功率轉換系統(tǒng)的關鍵元件,SiC MOSFET 在電動汽車、智能電網、航空航天及可再生能源等領域的普及,對電力電子設備的功率密度和效率提出了近乎嚴苛的要求 。然而,隨著器件尺寸的持續(xù)縮小和電流強度的不斷提升,SiC MOSFET 在極端故障工況下的魯棒性問題——尤其是短路(Short-Circuit, SC)故障下的失效機理,已成為制約其系統(tǒng)集成和大規(guī)模可靠應用的“阿喀琉斯之踵” 。

短路故障是電力電子裝置中最具破壞性的事件之一,通常源于柵極驅動信號誤觸發(fā)、負載突發(fā)故障或控制策略失效 。對于 1200 V 等級的 SiC MOSFET 而言,其芯片面積通常僅為同規(guī)格 Si IGBT 的五分之一至十分之一,這意味著在短路發(fā)生的微秒量級時間內,極高的母線電壓直接施加在極小的有源區(qū),導致器件內部功耗瞬時激增至數百甚至數千瓦 。這種功率密度的爆發(fā)式增長不僅引發(fā)了劇烈的自加熱效應,導致結溫迅速突破材料的物理極限,還會在芯片多層結構之間產生巨大的熱應力,誘發(fā)物理結構的災難性斷裂 。

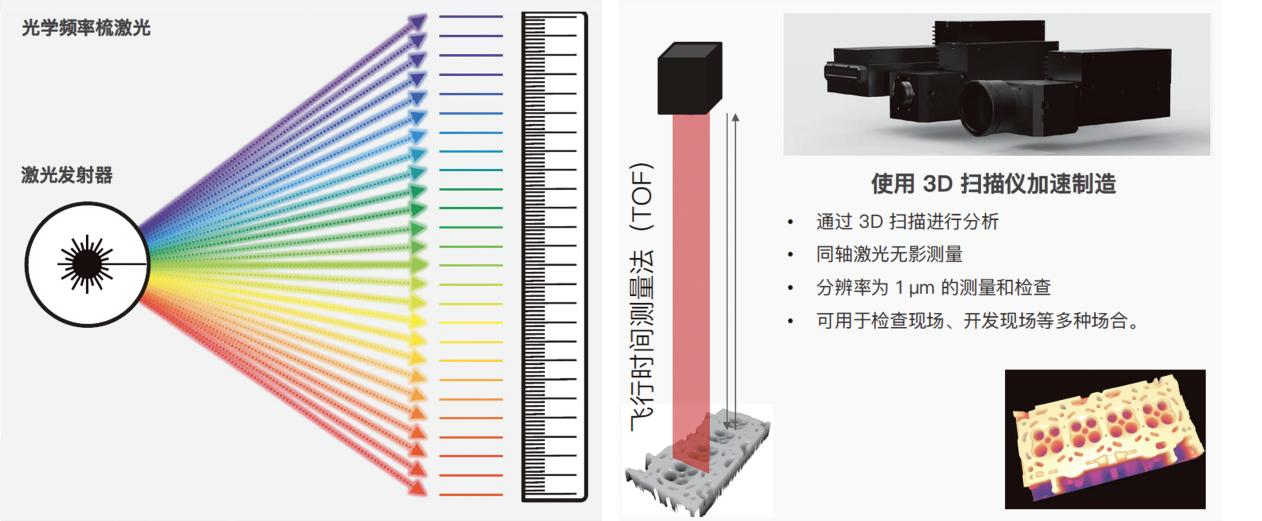

目前的工業(yè)標準通常要求功率器件具備至少 10 μs 的短路耐受時間(SCWT),以便保護電路有足夠的時間進行故障檢測并關斷器件 。然而,大量實驗表明,商用 SiC MOSFET 在標準母線電壓下的 SCWT 往往分布在 2 至 7 μs 之間,且表現出顯著的結構依賴性 。為了從微觀層面洞察短路過程中的物理場演化,單純依賴宏觀的電學表征(如 ID?、VDS? 波形)已不足以支撐高性能器件的開發(fā) 。基于 Sentaurus TCAD(Technology Computer-Aided Design)的電-熱-力多物理場耦合仿真,能夠以極高的時間和空間分辨率揭示芯片內部的載流子動力學、熱流分布以及應力集中點,從而為提升 SiC 芯片的短路魯棒性提供科學依據 。

2. 4H-SiC 材料的半導體物理基礎與建模參數

SiC 作為一種典型的寬禁帶半導體,其物理屬性與傳統(tǒng)硅材料有著本質區(qū)別。在 Sentaurus TCAD 仿真中,必須準確定義其各向異性的物理模型和隨溫度劇烈變化的輸運參數 。

2.1 晶體各向異性與電子輸運

SiC 器件中最常用的多型體為 4H-SiC。由于其六方晶系結構,4H-SiC 的遷移率、擊穿電場和熱導率在不同的晶向(如垂直于 c 軸和平行于 c 軸)表現出顯著差異 。傾佳電子力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

基本半導體代理商傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業(yè)自主可控和產業(yè)升級!

在 TCAD 仿真中,遷移率 μ 和電位 ? 的關系遵循各向異性張量方程。下表列出了 4H-SiC 在仿真中采用的核心物理常數:

| 物理量名稱 | 符號 | 典型值 (300 K) | 特性描述 | 參考來源 |

|---|---|---|---|---|

| 禁帶寬度 | Eg? | 3.26 eV | Si 的 3 倍,決定了低本征載流子濃度 | |

| 擊穿電場 | Ebr? | 2.5 - 3.0 MV/cm | Si 的 10 倍,支持更薄的外延層 | |

| 電子飽和漂移速度 | vsat? | 2.0×107 cm/s | 決定了短路飽和電流的上限 | |

| 熱導率 | κ | 3.0 - 4.5 W/(cm·K) | 優(yōu)于銅,但隨結溫升高而顯著下降 | |

| 介電常數 | εr? | 9.66 | 影響電場分布與電容特性 |

2.2 溫度相關性物理模型

短路瞬態(tài)仿真的準確性極大地依賴于物理參數對結溫的響應。隨著溫度從 300 K 升至 1000 K 以上,SiC 的物理行為會發(fā)生劇變 。

2.2.1 遷移率退化 (Mobility Degradation)

在短路期間,由于格點振動增強,聲子散射成為主導機制。Sentaurus TCAD 采用包含摻雜相關(DopingDep)、高場飽和(HighFieldSat)及格點溫度相關(TempDependence)的綜合遷移率模型 。實驗觀測到的短路電流在達到峰值后出現的緩慢下降現象,其物理本質便是結溫升高導致的載流子遷移率大幅退化 。

2.2.2 本征載流子濃度的指數級增長

雖然 SiC 的本征溫度極限高于 Si,但在短路引發(fā)的局部“熱點”區(qū)域,結溫若突破 1500 K,本征載流子濃度 ni? 將呈指數級上升,直至接近漂移區(qū)的摻雜濃度 。這將引發(fā)漏電流量級的躍遷,是熱失控失效的直接誘因。

2.2.3 比熱容與熱導率的非線性效應

SiC 的比熱容 Cv? 隨溫度升高而增加,這意味著在極高結溫下,吸收相同熱量所需的能量更多 。忽略這一非線性效應會導致仿真預測的峰值結溫產生約 25% 的偏差 。同時,熱導率 κ 隨溫度升高而降低,表現為 κ(T)∝T?1.5,進一步惡化了高溫區(qū)的散熱效率 。

2.3 摻雜劑的不完全電離 (Incomplete Ionization)

由于 SiC 的受體(如鋁 Al)和供體(如氮 N)能級較深,在室溫下并未完全電離 。短路過程中的劇烈溫升會顯著提高電離率,改變器件的有效摻雜剖面,進而影響 JFET 區(qū)的電阻和短路飽和電流的波形。TCAD 仿真中必須引入 Fermi 模型和能級退化參數來修正這一電離過程 。

3. 短路故障的分類與電學物理過程

根據短路發(fā)生的時刻及外圍電路狀態(tài),SiC MOSFET 的短路事件通常被劃分為三種基本類型 。

3.1 硬開關短路 (Hard Switching Fault, HSF)

HSF 發(fā)生在器件開啟之前,即漏源兩端已經承受了全母線電壓,此時柵極突然接收到開啟信號 。

- 物理過程:在柵極開啟的瞬間,器件直接從關斷狀態(tài)切入飽和區(qū)。漏極電流 ID? 迅速攀升至數百安培,同時漏源電壓 VDS? 維持在高位。

- 能量特征:HSF 產生的瞬態(tài)功率密度最高。由于 VDS? 始終為高值,器件內部的電場主要集中在柵氧化層邊緣和 PN 結處 。

- 失效傾向:極高的峰值結溫往往在關斷時刻達到最大,易引發(fā)延遲失效(Delayed Failure)。

3.2 負載下故障 (Fault Under Load, FUL)

FUL 指器件在正常導通(對負載供電)狀態(tài)下,負載端突然短路 。

- 物理過程:VDS? 在極短的時間內從幾伏特激增至母線電壓。根據 iC?=CGD??dv/dt,巨大的 VDS? 變化率通過米勒電容(Miller Capacitance)向柵極注入電荷,導致柵極電壓 VGS? 出現顯著過沖 。

- 電磁反饋:VGS? 的過沖進一步激發(fā)了更高的 ID? 峰值。因此,在相同母線電壓下,FUL 的短路電流峰值通常高于 HSF 。

- 防護難點:FUL 對驅動電路的箝位能力提出了更高要求。

3.3 第三象限短路 (Type III SC)

在橋式電路中,若處于續(xù)流狀態(tài)的 SiC MOSFET(體二極管導通或同步整流導通)遭遇另一側橋臂誤開啟,則發(fā)生第三象限短路 。此時器件需在極短時間內完成從反向導通到正向阻斷狀態(tài)的轉變,電流方向發(fā)生劇烈逆轉,涉及復雜的載流子抽取和復合過程。

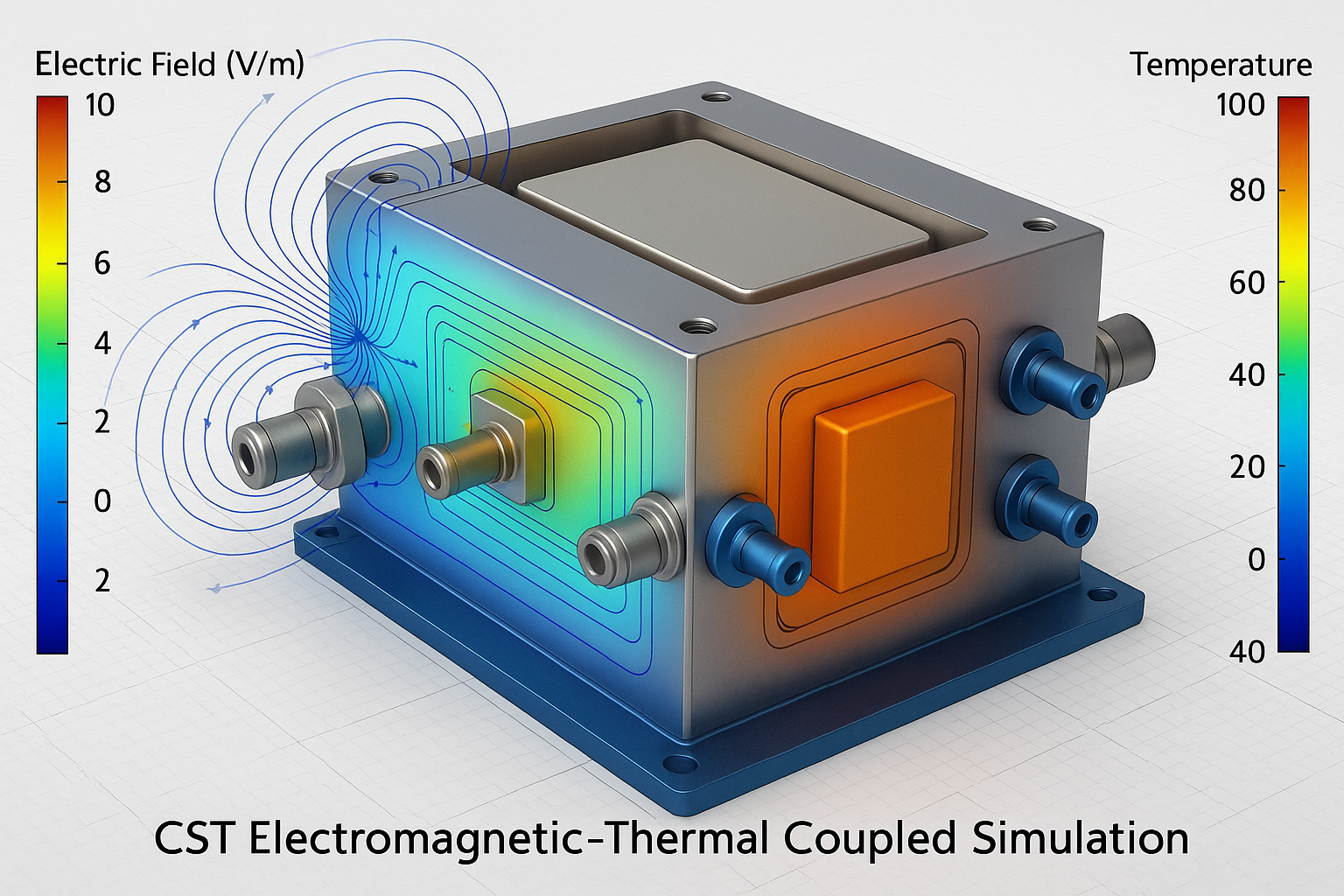

4. Sentaurus TCAD 的電-熱-力耦合建模方法

為了真實還原短路失效過程,TCAD 仿真必須打破單一物理場的限制,實現電學輸運、格點自加熱以及固體力學應變的實時同步求解 。

4.1 電-熱耦合:熱力學傳輸模型 (Thermodynamic Model)

Sentaurus Device 的核心在于求解泊松方程、電流連續(xù)性方程和格點能量平衡方程。在短路仿真的極高電流密度下,傳統(tǒng)的漂移-擴散模型已不足以描述熱梯度對載流子的貢獻 。

必須在 Physics 塊中聲明 Thermodynamic 選項,這引入了溫差電效應(Soret effect)。此時,電流密度方程修正為:

Jn?=?nqμn???n?+nμn?(?Pn??T)

其中,?T 代表溫度梯度,這一項在溝道和 JFET 區(qū)等熱產生極度集中的區(qū)域對電場重新分布起到了關鍵作用 。

4.2 結構化建模與混合模式仿真 (Mixed-Mode)

短路特性受外部寄生參數(如母線雜散電感 Lσ?、驅動電阻 RG?)影響巨大。使用 Sentaurus Device 的 Mixed-Mode 功能,可以將有限元定義的微觀結構嵌入到外部 SPICE 電路網絡中 。

下表展示了基于“基本半導體”典型器件參數建立的短路仿真電路基準配置:

| 電路元件名稱 | 符號 | 仿真設定值 | 物理意義 | 參考來源 |

|---|---|---|---|---|

| 母線電壓 | VDC? | 600 - 800 V | 實際應用的主流電壓等級 | |

| 柵極驅動電壓 | VGS(on/off)? | +18 V / -5 V | 確保可靠開啟與關斷 | |

| 外接柵極電阻 | RG(ext)? | 10 - 22 Ω | 控制 dv/dt 與短路響應速度 | |

| 雜散電感 | Lstray? | 30 - 40 nH | 模擬功率回路的寄生效應 |

4.3 固體力學耦合 (Solid Mechanics Model)

短路失效的最終形式往往是物理層面的炸裂。Sentaurus 提供了 SolidMechanics 模塊,通過計算各區(qū)域的熱膨脹應變和 von Mises 應力,預測材料的疲勞與開裂 。應力張量與溫度變化的關系遵循:

σ=C:(ε?αΔTI)

其中,C 為剛度張量,α 為材料的熱膨脹系數(CTE)。TCAD 仿真中需精細定義各材料層(SiC、金屬鋁、聚酰亞胺、鈍化層)的彈性模量和 CTE 隨溫度變化的函數 。

5. SiC MOSFET 短路失效的主要微觀機制

基于 TCAD 多物理場仿真與后失效分析(Post-Failure Analysis),SiC MOSFET 的短路失效可歸納為以下四種核心物理機制 。

5.1 熱失控與寄生 BJT 開啟 (BJT Latch-up)

這是最致命的失效模式。SiC MOSFET 內部集成了一個由 N+ 源區(qū)、P-well 和 N? 漂移區(qū)構成的寄生 NPN 雙極型晶體管 。

- 誘發(fā)因素:在短路過程中,高能空穴電流在流經 P-well 基區(qū)電阻時產生壓降。當該壓降達到 SiC 的結電壓(約 2.7 V)時,寄生 BJT 將強制開啟 。

- 正反饋過程:BJT 的開啟引入了額外的雙極電流,進一步增加了焦耳熱產出;結溫升高又導致 P-well 電阻增加,基極壓降更大,從而形成失控的自激循環(huán)。

- 仿真表現:TCAD 云圖中可以清晰地觀察到,當 ID? 電流突然脫離飽和區(qū)并呈垂直上升趨勢時,P-well 區(qū)域的電流矢量方向發(fā)生了根本性逆轉 。

5.2 柵極氧化層(SiO2?)介質失效

柵極氧化層的可靠性一直是 SiC 器件的薄弱環(huán)節(jié) 。

- 電-熱場協同破壞:短路時,柵極承受正向偏置,氧化層電場極高。高溫會激發(fā) Fowler-Nordheim(FN)隧穿效應,使大量熱電子注入氧化層陷阱中,導致閾值電壓 Vth? 發(fā)生不可逆漂移 。

- 物理擊穿:當局部結溫突破介質極限時,SiO2? 發(fā)生熱擊穿。在仿真波形中,這通常表現為 VGS? 瞬間跌落至 0 V,驅動電路完全失去對溝道的控制能力 。

5.3 鋁金屬熔化與級聯力學失效

這是典型的力學主導失效模式。頂層源極鋁(Al)的熔點僅為 660°C (933 K) 。

- 熱應力失配:由于鋁的 CTE(約 23×10?6/K)遠大于 SiC(約 4.0×10?6/K),在短路引起的劇烈溫升下,金屬層對下方的介質層產生巨大的擠壓應力 。

- 熔融滲透:短路 5-10 μs 后,頂層鋁層往往進入熔融狀態(tài)。光學成像證實,熔融鋁會在巨大的熱機械應力作用下,沿著受損層間介質(PMD)的微裂紋向下滲透,最終與柵極或 P-base 發(fā)生短路 。

5.4 延遲失效機制 (Delayed Failure)

延遲失效是指器件在短路脈沖結束后看似正常關斷,但在關斷后的數百微秒內突然燒毀 。

- 物理機制:關斷瞬間,內部結溫達到峰值。雖然溝道電流消失,但高溫引發(fā)的本征熱產生電流(Itail)在全母線電壓下依然會產生可觀的功耗。由于此時芯片正處于熱量向封裝外部傳導的瓶頸期,若熱量積聚速度超過耗散速度,局部“熱點”將繼續(xù)升溫,最終觸發(fā)熱失控或物理爆裂 。

6. 不同拓撲結構的短路魯棒性量化分析

器件的幾何結構對電場分布、電流路徑及散熱性能有著決定性影響。

6.1 平面型 (Planar) 與溝槽型 (Trench) 的對比

| 結構類型 | 核心優(yōu)勢 | 短路可靠性表現 | 主要失效模式 |

|---|---|---|---|

| 平面型 | 工藝成熟,Vth? 穩(wěn)定性好 | SCWT 較長,通常為 6-8 μs | 關斷后的熱失控、延遲失效 |

| 溝槽型 | 導通電阻極低,無 JFET 電阻 | SCWT 較短,通常為 2-5 μs | 溝槽拐角處的柵氧化層熱擊穿 |

數據參考:

溝槽型結構雖然在效率上具有代際優(yōu)勢,但其柵氧化層位于受力最集中的溝槽底部。TCAD 仿真顯示,溝槽底角的電場強度可達平面型的 1.5 倍,且此處的力學 von Mises 應力極易誘發(fā)介質層疲勞 。

6.2 溝槽型結構的演進:雙溝槽 (DT) 與非對稱溝槽 (AT)

研究表明,通過改變溝槽的對稱性,可以顯著改善短路時的熱分布 。

雙溝槽 (Double Trench, DT) :在柵極溝槽兩側設置源極溝槽。仿真顯示,這種結構能夠有效屏蔽柵底電場,但在短路時,熱量高度對稱地集中在窄小的臺面區(qū)域,導致中心點溫升過快 。

非對稱溝槽 (Asymmetric Trench, AT) :通過引入一側深 P-Shield 屏蔽區(qū),打破熱量分布的對稱性。

- 仿真洞察:AT 結構成功將短路時的熱量產生點推向芯片深處(遠離 SiC/SiO2? 界面),有效降低了柵極氧化層承受的熱壓力 。

- 性能提升:在 600 V 母線電壓下,AT 結構的 SCWT 可提升至 12 μs 以上,展現出卓越的工程應用潛力 。

7. 典型商用 SiC MOSFET 模塊電學特性基準

在進行 TCAD 模型校準時,應充分參考當前工業(yè)界領先產品的電學規(guī)格。以下是“基本半導體”系列模塊在仿真中的關鍵對標數據:

| 模塊型號 | 電壓 VDSS? | 額定電流 ID? | RDS(on)? (Typ.) | 封裝特性 | 仿真關鍵參考點 |

|---|---|---|---|---|---|

| BMF540R12KHA3 | 1200 V | 540 A | 2.2 mΩ | 62mm 工業(yè)級 | 超高短路電流密度下的散熱瓶頸 |

| BMF240R12KHB3 | 1200 V | 240 A | 5.3 mΩ | Si3?N4? 陶瓷襯底 | 陶瓷基板對應力的緩沖效應 |

| BMF160R12RA3 | 1200 V | 160 A | 7.5 mΩ | 34mm 標準封裝 | 母線電感對 VGS? 過沖的影響 |

| B3M010C075Z | 750 V | 240 A | 10.0 mΩ | 銀燒結單管 | 銀燒結界面對結溫降低的貢獻 |

仿真中應特別注意 RDS(on)? 隨溫度的變化率。例如,BMF540R12KHA3 的芯片級內阻從 25°C 的 2.2 mΩ 升至 175°C 的 3.9 mΩ 。這一接近兩倍的增長率直接決定了短路電流波形的斜率與峰值,是實現電-熱閉環(huán)精確仿真的核心參數。

8. 提升 SiC 芯片短路魯棒性的多維度優(yōu)化方案

基于電-熱-力耦合仿真的結論,可從設計、材料和系統(tǒng)三個層面提出優(yōu)化路徑 。

8.1 結構級設計優(yōu)化 (Cell-Level)

增加溝道長度 Lch? :

- 物理機制:雖然增加 Lch? 會略微提升導通電阻,但能顯著降低飽和電流峰值。TCAD 靈敏度分析表明,溝道長度增加 10%,短路耐受時間可平均延長 0.5-1.0 μs 。

優(yōu)化 JFET 區(qū)寬度與摻雜:

- 物理機制:通過減小 JFET 寬度實現“預耗盡”效應,在短路高壓下自動收縮電流通道,起到內生限流作用 。

柵介質層厚度權衡:

- 物理機制:適當加厚柵氧化層可大幅提升臨界擊穿電壓,但需平衡跨導下降和 Vth? 調整帶來的驅動損耗。

8.2 封裝與材料工藝優(yōu)化 (Package-Level)

銀燒結 (Silver Sintering) 技術:

- 優(yōu)勢:相比傳統(tǒng)錫膏焊料,銀燒結層具有更高的導熱系數(>200 W/m·K)和更低的 CTE 錯位 。仿真顯示,采用銀燒結工藝可使短路瞬態(tài)結溫峰值降低 20?30°C,有效延緩熱失控。

源極金屬層(Metallization)改進:

- 方案:增加鋁層厚度或引入鎳/銅(Ni/Cu)復合金屬層 。鎳層的熔點(1453 °C)遠高于鋁,可作為一道強有力的物理屏障,阻擋熔融金屬向敏感的有源區(qū)滲透 。

高韌性層間介質 (PMD) :

- 方案:開發(fā)并應用具有更高斷裂韌性和 CTE 匹配性的絕緣材料,防止在極端熱應力下產生結構裂紋 。

8.3 系統(tǒng)級主動保護策略 (System-Level)

超快退飽和檢測 (Desat Protection) :

- 針對 SiC MOSFET 極短的 SCWT,傳統(tǒng)的 Desat 響應時間(通常 > 2 μs)已顯不足。仿真支持開發(fā)響應時間小于 500 ns 的智能驅動電路 。

雙階段關斷策略 (Two-Stage Turn-off) :

- 在檢測到短路后,先將柵壓降低至中等水平(如 10 V)以限制電流增長,隨后再徹底關斷。這能有效降低關斷瞬間的 di/dt 和電壓尖峰,防止二次失效 。

9. 結論:通往高可靠性碳化硅應用之路

通過基于 Sentaurus TCAD 的電-熱-力多物理場耦合仿真,我們得以剝離宏觀電學波形的掩蓋,深入觸及 SiC MOSFET 短路失效的物理本質。研究清晰地表明,短路失效并非由單一因素驅動,而是電荷輸運異常、格點極端升溫以及機械應力斷裂交織作用的結果。

核心發(fā)現總結如下:

- 熱-力耦合是失效的終極誘因:大多數短路失效最終表現為熔融鋁沿力學裂紋滲入柵極,而非單純的半導體本征擊穿。

- 結構拓撲決定熱穩(wěn)定性:非對稱溝槽等先進結構通過空間上的熱源偏移,為介質層提供了寶貴的生存裕度,是未來高魯棒性器件的主流演進方向。

- 封裝工藝是隱形的防線:銀燒結工藝和金屬化層結構的改進在瞬態(tài)散熱和應力緩沖中扮演了不可替代的角色。

展望未來,隨著 SiC 器件向 3.3 kV 乃至 10 kV 更高電壓等級邁進,其短路失效機理將涉及更復雜的動態(tài)雪崩和雙極電荷調控 。依托不斷完善的多物理場仿真模型,結合實時在線監(jiān)控技術,我們不僅能預判器件的生命周期極限,更能通過精準的“基因工程式”芯片設計,徹底解決碳化硅芯片的短路可靠性難題。這將為全球電力電子系統(tǒng)的持續(xù)綠色轉型,提供堅實且長久的底層硬件支撐

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54320瀏覽量

468512 -

SiC MOSFET

+關注

關注

1文章

170瀏覽量

6812 -

sentaurus

+關注

關注

2文章

4瀏覽量

1728

發(fā)布評論請先 登錄

IGBT與SiC MOSFET功率模塊的失效機理、診斷方法與防護策略

Altair Radioss:瞬態(tài)動力學仿真專家?

SiC功率模塊的短路保護(Desat)響應速度優(yōu)化:亞微秒級無誤觸發(fā)的實現

芯片失效故障定位技術中的EMMI和OBIRCH是什么?

哪些應用環(huán)境最容易導致 ESD 管短路失效?——從失效機理到工程對策

碳化硅(SiC)MOSFET功率模塊在礦用卡車電控系統(tǒng)中的延壽機理研究:基于平均溫升降低的分析報告

ASP3605同步降壓芯片多場景失效機理與防護策略研究

淺談SiC MOSFET器件的短路耐受能力

一文探究SiC MOSFET的短路魯棒性

Simcenter STAR-CCM+多物理場解決方案:支持在設計早期對實際性能進行預測

SiC MOSFET芯片短路失效機理:基于 Sentaurus TCAD 的電-熱-力多物理場耦合仿真

SiC MOSFET芯片短路失效機理:基于 Sentaurus TCAD 的電-熱-力多物理場耦合仿真

評論