到目前為止,本文關于 AMD VersalAIE 驗證和 AMD Vitis新的驗證功能的研究,所有內容都基于仿真完成。

例如我們已經研究了如何使用 MATLAB 或 Python 進行 Vitis 功能仿真,研究了如何使用 XSIM 模擬 AIE 設計。

在這個項目中,我們將研究如何使用 AMD Vitis 硬件在環(HIL)功能在實際硬件上運行 Vitis 子系統設計。

AMD Vitis 硬件在環概述

要使用 Vitis HIL 功能,首先必須將 Vitis 設計封裝為 Vitis 子系統 (VSS)。在通過 Vitis 功能仿真以及 AMD Vivado 中的 XSim 仿真 確認 VSS 的功能符合預期之后,我們就可以進入硬件測試階段。通過對硬件進行測試,可以在將該子系統集成到更大規模設計之前,驗證 VSS 是否能在硬件上按預期運行。

從 VSS 開始,HIL 流程會基于 VSS 創建一個支持 HIL 的設計。設計完成后,將創建 HIL 服務器,并將其與設計一起打包到 SD 卡上。目標板卡通電并通過 SD 卡啟動后,主機系統即可通過以太網與目標板卡進行交互。主機系統可以使用 Python 或 Matlab 通過以太網與設計進行通信。開發人員能夠向目標板卡發送測試向量,在硬件上執行計算,并通過以太網將結果返回主機,從而夠驗證硬件上的行為。

目前,VCK190 評估套件支持此功能,設計可以包含 AI 引擎、HLS 或 HDL 模塊或它們的任意組合,只需它們位于 Vitis 子系統內即可。

創建 VSS

在 AMD Vitis 中,通過使用 v++ 鏈接器將可重用的 PL 內核和/或 AI 引擎圖打包成一個與平臺無關的組件而創建的 VSS(Vitis 子系統)。該流程首先將 PL 內核編譯成 .xo 文件(來自 HLS 或 RTL),并在需要時將 AI 引擎圖構建成 libadf。

隨后,這些組件在 VSS 配置文件中進行描述,該文件定義了內核實例、子系統元數據以及各組件之間的互連。

VSIS 的生成方式是:針對特定目標器件型號,以 VSS 模式運行鏈接器,生成一個 .vss 歸檔文件。只要使用相同的器件,該文件就可以被重復使用、仿真或以層次化方式集成到更高級別的 Vitis 設計中。

例如,可以通過使用配置文件創建一個僅包含 PL 的 VSS,該文件實例化一個內核并定義子系統。然后,可以使用以下命令進行構建,這將生成一個可重用的 `my_vss.vss` 子系統,可以將其導入到另一個 Vitis 項目中。

v++ --link --mode vss --part xcvc1902-vsva2197-2MP-e-S --config vss.cfg my_kernel.xo

創建 Vitis 子系統的另一種方法是使用 Vitis Model Composer 提供的導出為 VSS(Export to VSS) 功能。

在本項目中,我們將使用 AMD 提供的 VSS,它是 Vitis HIL 演示的一部分。這些 VSS 已以壓縮包形式附在項目中供使用。

準備工作

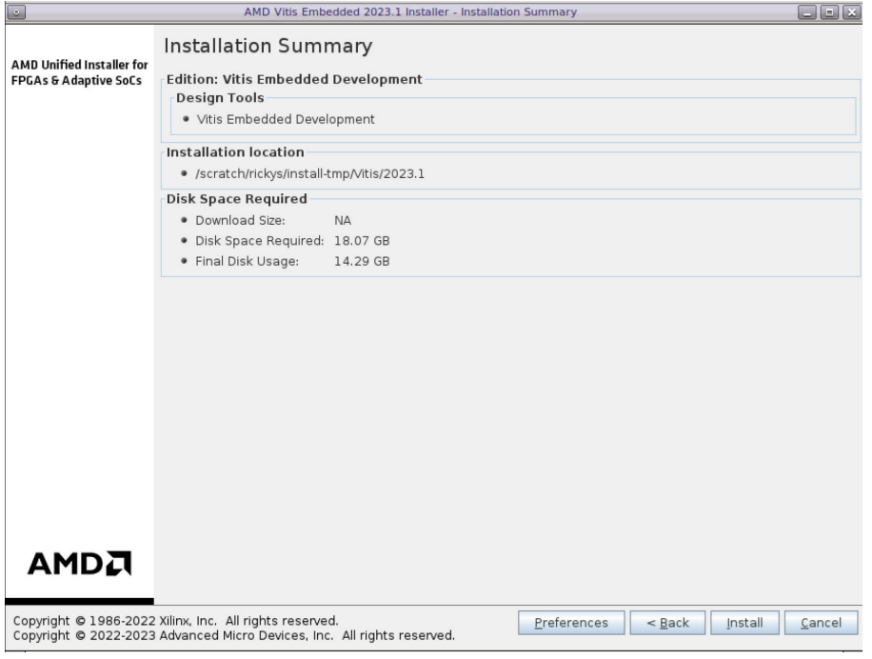

首先,我們需要確保開發機器上已安裝 Vitis 2025.2。如果尚未安裝,您可以從這里下載:

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vitis.htlm

安裝完 Vitis 之后,接下來我們需要準備 SDK 和 RootFS,我們也可以從 AMD 網站下載獲取。

下載完成后,第一步是創建 SDK。可以通過解壓 Versal 通用鏡像并運行腳本 sdk.sh 來完成。

為了能夠運行構建,我們需要設置幾個變量,第一個 SDK_LOCAL 指向剛剛創建的 SDK 的目錄。

第二個 SYSROOT_VERSAL 指向內核鏡像的位置,RootFS 也是作為通用鏡像下載的一部分提供的。

現在我們準備創建目標 VSS 的 SD 卡鏡像。為此,我們將以通道化器示例為例。

創建 HIL 服務器 SD 卡鏡像

這將是一個命令行構建過程,因此我們首先需要從上面使用的終端啟動 Vitis 2025.2 環境。

完成后,我們將運行該命令。

啟動構建流程:

構建過程啟動后,你會看到創建了一個名為 HIL_DUT 的文件夾,它是構建的工作目錄。

不久之后,構建過程即可完成。

在構建的工作目錄下,您可以看到輸出的 SD 卡信息和 SD 卡鏡像。

SD 卡鏡像和主機應用程序代碼引用的 hil_interface_spec.json 文件通過唯一的哈希碼關聯,從而確保使用正確的文件對,防止與之前的版本混淆。

SD 卡的內容:

下一步是將此內容復制到 SD 卡中,將其插入 VK190 并啟動開發板。

硬件在環 (HIL)

使用 HIL,第一步是將 SD 卡插入 VCK190 并啟動開發板。

通過串口,使用用戶名 petalinux 登錄到 VCK190 上運行的嵌入式Linux。

如果開發板已連接到網絡,則 DHCP 服務器應已為其分配 IP 地址,因此可以跳過此步驟。

但如果開發板的以太網線連接到 PC,則需要執行一些步驟才能使開發板可訪問網絡。

在信道化器示例中,Python 文件夾下有兩個 Python 文件。打開 Hosts 文件并編輯 VCK190 的 IP 地址。

在 VCK190 上,運行以下命令:

要啟動服務器,請運行以下命令:

這將啟動硬件在環服務器,等待客戶端連接到主機。

在主機上運行 hil_host.py 文件,這將啟動 HIL 示例。您將看到 HIL 按預期處理數據。

在 VCK190 目標上,您將看到客戶端連接,并且應用程序開始在客戶端的控制下運行。

腳本詳解

本應用使用了兩個腳本,讓我們來分析它們的關鍵要素。 wb_src 文件提供了激勵引擎,真正實現了硬件在環 (HIL) 設置。該模塊生成一個可重復且完全可控的寬帶復雜波形,其外觀和行為都與真實信號環境非常相似。它允許啟用或禁用多達 16 個獨立的子通道,選擇性地應用升余弦脈沖整形的 QAM 調制,甚至可以注入恒定(類似直流)通道以進行快速的基本功能檢查。對于 HIL 至關重要的是,FIR 濾波器的狀態在調用之間得以保留,因此信號在各個處理模塊之間保持連續——這與硬件在實際數據流系統中看到的情況完全一致。

HIL_HOST.py 控制著硬件測試,它將設計作為可調用的硬件加速器部署在網絡上。在 Python 主機上,我們使用接口規范 JSON 實例化 HIL 客戶端,并將其指向開發板的 IP 地址和端口。

在主處理循環中,HIL 流程與流式系統非常相似,使用 wb_src 生成復數樣本,并將其量化為定點 varray,然后通過 hil_chnlzr.run() 將其傳遞給 FPGA。

一個重要的實際問題是,硬件返回的數據量并非總是均勻分布在所有輸出或不同調用之間。為了解決這個問題,我們在主機上顯式地將每個輸出流緩沖到 FIFO 中,并且僅在所有通道都有數據可用時才釋放幀。

總結

本項目完成了三部曲的演示,展示了如何使用硬件在環驗證通用的 AIE、HLS 和 RTL 內核子系統。這是驗證的最后一個環節,驗證過程從功能仿真開始,逐步過渡到在 Vivado 中進行 RTL 仿真(使用更廣泛的設計),最終完成硬件在環驗證。

-

amd

+關注

關注

25文章

5698瀏覽量

140246 -

matlab

+關注

關注

189文章

3028瀏覽量

239000 -

仿真

+關注

關注

55文章

4512瀏覽量

138541 -

Vitis

+關注

關注

0文章

158瀏覽量

8420

原文標題:AMD Vitis? 硬件在環 - 如何使用 Vitis 在硬件在環(HIL)上運行 Vitis 子系統

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用AMD Vitis Unified IDE創建HLS組件

如何在AMD Vitis Unified IDE中使用系統設備樹

閑談Vitis AI|DPU在UltraScale平臺下的軟硬件流程(1)

Vitis2023.2使用之—— classic Vitis IDE

Vitis2023.2使用之—— updata to Vitis Unified IDE

使用Vitis HLS創建屬于自己的IP相關資料分享

AMD全新Vitis HLS資源現已推出

Vitis Unified IDE 和通用命令行參考手冊

AMD Vitis? Embedded嵌入式軟件開發套件的功能和特性概述

在Windows 10上創建并運行AMD Vitis?視覺庫示例

如何使用AMD Vitis硬件在環功能運行Vitis子系統設計

如何使用AMD Vitis硬件在環功能運行Vitis子系統設計

評論