高性能時鐘管理利器:HMC7044B深度解析

在電子設計領域,時鐘管理對于保證系統的穩定運行和高性能表現至關重要。HMC7044B作為一款高性能的14輸出抖動衰減器,為我們帶來了出色的時鐘解決方案。今天,我們就來深入了解一下這款器件。

文件下載:HMC7044B.pdf

一、HMC7044B概述

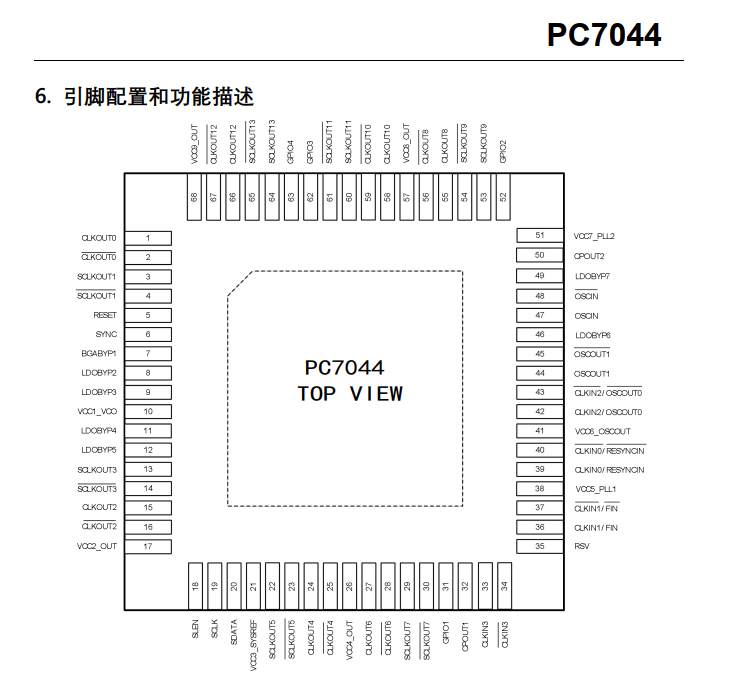

HMC7044B是HMC7044的升級版,是一款高性能、雙環、整數N抖動衰減器。它能夠為高速數據轉換器提供參考選擇和超低相位噪聲頻率的生成,支持并行或串行(JESD204B和JESD204C類型)接口。該器件采用68引腳、10 mm × 10 mm LFCSP封裝,內部集成了諸多先進功能,可滿足GSM和LTE基站設計等多種應用需求。

二、卓越特性

(一)超低抖動與噪聲性能

- 超低rms抖動:在2457.6 MHz時,典型rms抖動僅為44 fs(12 kHz至20 MHz)。如此低的抖動能夠有效減少信號失真,提高數據傳輸的準確性,對于對時鐘精度要求極高的高速數據轉換器等設備來說至關重要。

- 低噪聲:噪聲地板低至?156 dBc/Hz(2457.6 MHz),在800 kHz、983.04 MHz輸出時,相位噪聲為?141.7 dBc/Hz。低噪聲特性使得HMC7044B在復雜的電磁環境中也能提供穩定、純凈的時鐘信號。

(二)豐富的輸出與接口支持

- 多類型輸出:PLL2最多可提供14個LVDS、LVPECL或CML類型的設備時鐘(DCLKs),最大CLKOUTx/CLKOUTx和SCLKOUTx/SCLKOUTx頻率可達3200 MHz,能夠滿足不同設備對時鐘信號的需求。

- JESD204B和JESD204C兼容性:支持JESD204B和JESD204C兼容的系統參考(SYSREF)脈沖,為高速數據傳輸提供了可靠的時鐘同步機制。

(三)靈活的相位控制與延遲調節

- 獨立可編程延遲:在14個時鐘輸出通道上,可獨立編程25 ps模擬和? VCO周期數字延遲,能夠精確調整時鐘信號的相位,以適應不同的系統需求。

- SPI可編程相位噪聲與功耗:通過SPI可以靈活配置相位噪聲與功耗的關系,在不同的應用場景下實現性能與功耗的平衡。

(四)可靠的參考管理與同步

- 頻率保持模式:具備頻率保持模式,能夠在參考信號丟失時維持輸出頻率,保證系統的持續穩定運行。

- 信號丟失檢測與無縫切換:支持信號丟失(LOS)檢測和無中斷參考切換,確保系統在參考信號出現問題時能夠快速、無縫地切換到備用參考源。

- SYSREF有效中斷:SYSREF有效中斷功能可簡化JESD204B和JESD204C的同步過程,減少FPGA等設備中的等待時間延遲。

(五)其他特性

- 窄帶雙核心VCO:采用窄帶、雙核心VCO,提供了更寬的頻率覆蓋范圍和更好的相位噪聲性能。

- 多輸入時鐘支持:支持多達4個LVDS、LVPECL、CMOS和CML模式的輸入時鐘,增加了系統設計的靈活性。

- 出色的電源抑制比:片上穩壓器提供了出色的電源抑制比(PSRR),能夠有效減少電源噪聲對時鐘信號的影響。

三、工作原理

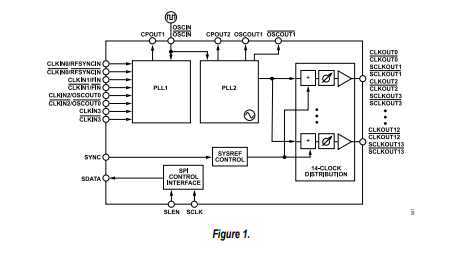

HMC7044B采用雙環架構,由兩個整數模式PLL串聯組成抖動衰減時鐘乘法單元。

(一)PLL1——抖動衰減與參考管理

PLL1主要用于將干凈的本地VCXO鎖定到相對嘈雜的參考信號上,采用非常窄的環路帶寬(通常為20 Hz至500 Hz),以濾除參考信號中的抖動和雜散信號。同時,PLL1還負責監控參考信號的狀態,在參考信號失效時進行切換或進入保持模式。

(二)PLL2——頻率乘法與高性能輸出

PLL2將低噪聲的VCXO信號乘以到VCO頻率(2 GHz至3 GHz范圍),并提供超低的附加噪聲。PLL2內部具有鎖檢測、頻率倍增器、部分集成環路濾波器、VCO選擇、外部VCO使用等功能,能夠實現歸一化的帶內噪聲地板FOM為?232 dBc和閃爍FOM為?266 dBc,典型的12 kHz至20 MHz集成抖動為44.0 fs。

(三)時鐘輸出網絡

HMC7044B的時鐘輸出網絡具有非常好的相位噪聲地板、大量的DCLK和SYSREF通道、確定的相位對齊、精細的相位控制、頻率覆蓋范圍廣、低串擾和雜散性能等特點。每個輸出通道都包含獨立的分頻器、相位調整和模擬延遲電路,可提供最終的靈活性,以適應不同的系統需求。

四、典型應用

(一)JESD204B和JESD204C時鐘生成

HMC7044B的JESD204B和JESD204C兼容性使其成為高速數據轉換器時鐘生成的理想選擇,能夠為數據轉換器提供精確、穩定的時鐘信號,確保數據的準確傳輸。

(二)蜂窩基礎設施

在蜂窩基礎設施中,如多載波GSM、LTE、W - CDMA等系統,HMC7044B的高性能時鐘管理功能能夠滿足基站對時鐘精度和穩定性的要求,提高通信系統的性能。

(三)數據轉換器時鐘

為數據轉換器提供低抖動、低噪聲的時鐘信號,提高數據轉換器的采樣精度和動態范圍。

(四)微波基帶卡

在微波基帶卡中,HMC7044B可用于時鐘分配和同步,確保基帶信號處理的準確性和穩定性。

(五)相控陣參考分配

為相控陣系統提供精確的參考時鐘,保證天線陣列的相位一致性,提高相控陣系統的性能。

五、編程與配置

HMC7044B通過3線串行端口接口(SPI)進行編程,上電時具有默認配置,無論參考時鐘是否存在,都能在VCO調諧范圍內生成有效輸出頻率。編程過程包括連接額定電源、釋放硬件復位、加載配置更新、配置PLL1和PLL2、配置SYSREF定時器、配置輸出通道等步驟。

六、布局與使用注意事項

(一)布局考慮

在電路板設計中,應采用RF電路設計技術,確保信號線具有50 Ω阻抗。將封裝的接地引腳和暴露焊盤直接連接到接地平面,并使用足夠數量的過孔連接頂部和底部接地平面,以減少電磁干擾。

(二)電源供應

要特別注意VCC1_VCO電源的噪聲特性,建議在100 kHz至10 MHz頻率范圍內,該電源的輸入噪聲低于50 nV/Hz,以確保器件的性能。

HMC7044B以其卓越的性能和豐富的功能,為電子工程師在時鐘管理設計中提供了一個強大的工具。在實際應用中,我們需要根據具體的系統需求,合理配置和使用該器件,以充分發揮其優勢。大家在使用過程中遇到過哪些問題或者有什么獨特的應用經驗呢?歡迎在評論區分享交流。

-

時鐘管理

+關注

關注

0文章

19瀏覽量

8548

發布評論請先 登錄

HMC7043:高性能時鐘分配器的技術解析與應用指南

高速利器——HMC724LC3 1:2扇出緩沖器深度解析

高速時鐘分配新利器——LMK1D1208P LVDS緩沖器深度解析

高性能電源利器:LTC7050 - 1深度解析

PC7044高性能時鐘抖動消除器中文手冊

PC7044高性能時鐘抖動消除器支持JESD204B 時鐘生成

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技術手冊

高性能時鐘管理利器:HMC7044B深度解析

高性能時鐘管理利器:HMC7044B深度解析

評論