高速時鐘分配新利器——LMK1D1208P LVDS緩沖器深度解析

在電子系統設計中,時鐘信號的精確分配至關重要,它直接影響著系統的性能和穩定性。特別是在高速通信、醫療成像等領域,對時鐘信號的質量和分配精度要求極高。TI推出的LMK1D1208P Pin - Controlled OE Low Additive Jitter LVDS Buffer,為這些應用場景提供了出色的解決方案。下面我們就來深入了解這款產品。

文件下載:lmk1d1208p.pdf

產品特性亮點

高性能時鐘分配能力

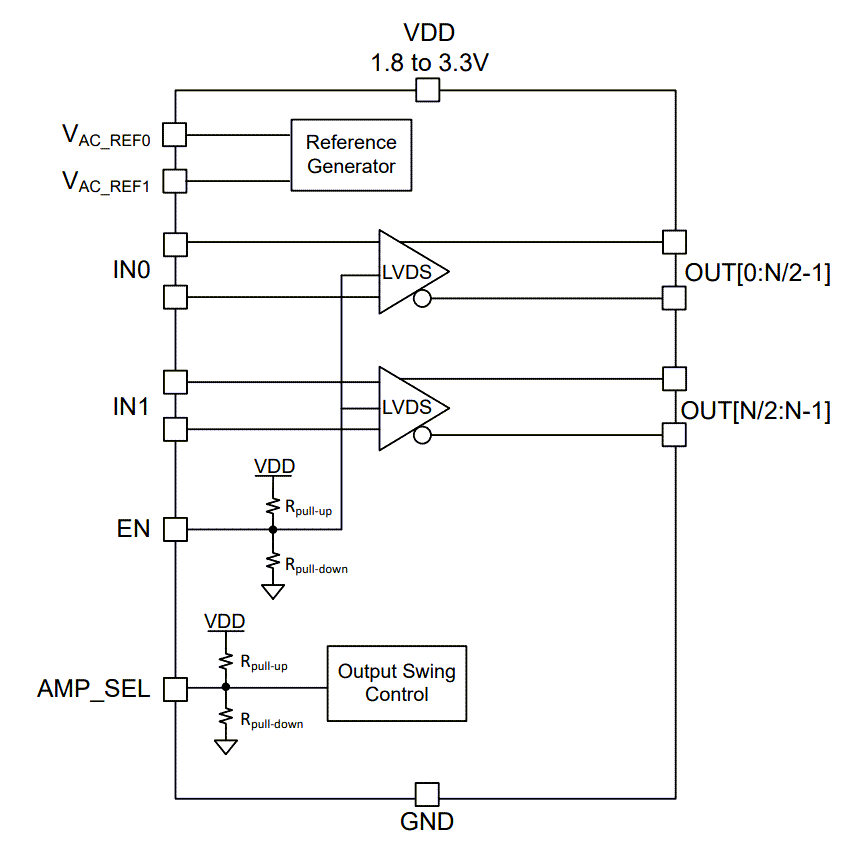

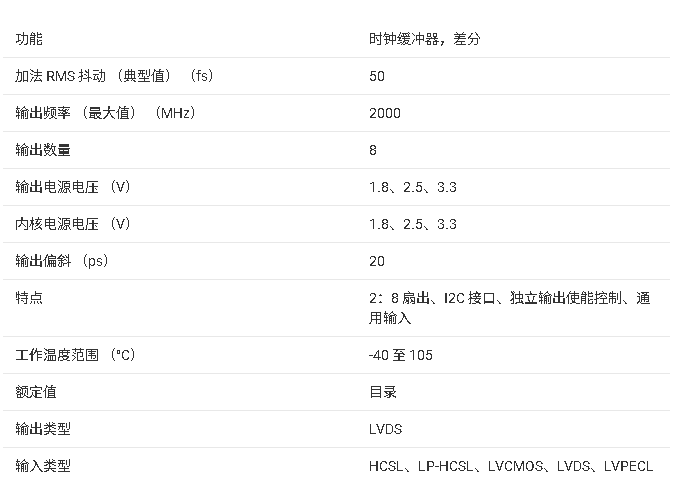

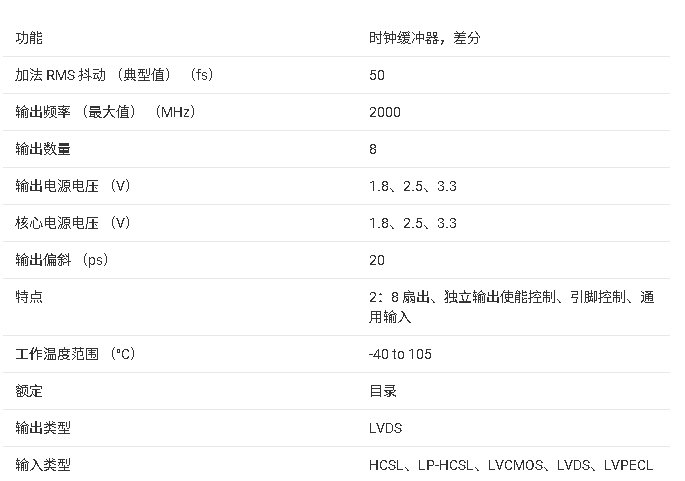

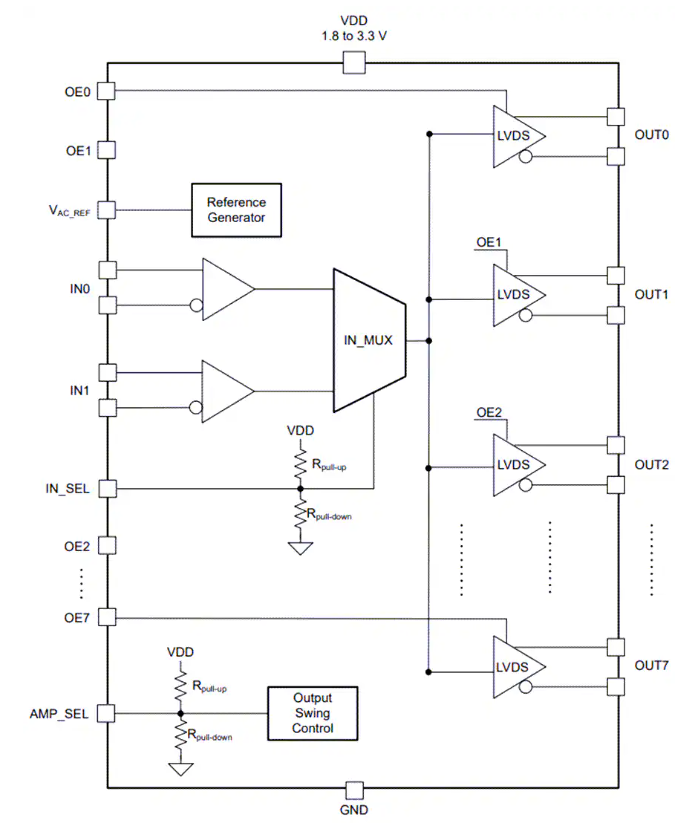

LMK1D1208P屬于高性能LVDS時鐘緩沖器家族,具備2個輸入和8個輸出(2:8)的配置,能夠將兩個可選的時鐘輸入信號(IN0和IN1)分配到8對差分LVDS時鐘輸出(OUT0 - OUT7),為系統提供了靈活的時鐘源選擇和多路同步時鐘輸出。其輸出頻率最高可達2 GHz,能滿足大多數高速應用的需求。

超低抖動與噪聲性能

低抖動是衡量時鐘信號質量的關鍵指標之一。LMK1D1208P在156.25 MHz頻率下,12 kHz至20 MHz積分范圍內的最大加性抖動小于60 fs rms,能夠有效減少時鐘信號的相位誤差,從而提高系統的穩定性和可靠性。同時,它還具有極低的相位噪聲底,典型值為 - 164 dBc/Hz,這使得在高速數據傳輸過程中,時鐘信號能夠保持干凈、穩定,減少噪聲干擾。

引腳靈活控制

該器件提供了豐富的硬件引腳,可對單個輸出進行獨立的使能或禁用操作。通過設置對應的OEx引腳為邏輯高電平1,可使LVDS差分輸出正常工作;而設置為邏輯低電平0時,輸出將處于高阻(Hi - Z)狀態,從而降低功耗。此外,IN_SEL引腳用于選擇將哪個輸入信號路由到輸出,方便用戶根據實際需求切換時鐘源。

寬電源電壓范圍與溫度適應性

LMK1D1208P支持1.8 V、2.5 V和3.3 V ± 5%的電源電壓,適用于多種不同的電源環境。其工作溫度范圍為 - 40°C至105°C,能夠在工業級溫度環境下穩定工作,滿足了各種惡劣工業應用場景的需求。

通用輸入兼容性

它的輸入具有很強的通用性,能夠接收LVDS、LVPECL、LVCMOS、HCSL和CML等多種類型的信號,方便與不同類型的時鐘源或驅動電路進行接口連接。同時,還提供了LVDS參考電壓VAC_REF,可用于電容耦合輸入。

產品規格細節

絕對最大額定值

了解器件的絕對最大額定值是確保其安全可靠工作的基礎。LMK1D1208P的電源電壓(VDD)最大為3.6 V,輸入電壓(VIN)和輸出電壓(VO)也有相應的限制范圍,輸入電流(IIN)和連續輸出電流(IO)同樣有具體的最大值要求。此外,結溫(TJ)最大為135°C,存儲溫度范圍為 - 65°C至150°C。超出這些額定值可能會導致器件永久性損壞,因此在設計時必須嚴格遵守。

ESD(靜電放電)額定值

在實際應用中,靜電放電是一個不容忽視的問題,它可能會對器件造成損害。LMK1D1208P在人體模型(HBM)下,所有引腳的ESD額定值為 ±3000 V,在帶電設備模型(CDM)下為 ±1000 V。在生產和使用過程中,必須采取適當的靜電防護措施,以確保器件的可靠性。

推薦工作條件

為了使器件能夠正常、穩定地工作,需要遵循推薦的工作條件。如核心電源電壓在不同供電模式下有相應的取值范圍,3.3 - V供電時為3.135 - 3.465 V,2.5 - V供電時為2.375 - 2.625 V,1.8 - V供電時為1.71 - 1.89 V。同時,電源電壓的上升斜率也有要求,需在0.1 - 20 ms內實現單調上升。工作自由空氣溫度范圍為 - 40°C至105°C,結溫范圍為 - 40°C至135°C。

電氣特性

器件的電氣特性決定了其在不同條件下的性能表現。例如,在所有輸出啟用且未端接、頻率為0 Hz時,靜態核心電源電流(IDD STAT)典型值為75 mA;當所有輸出啟用、負載電阻RL = 100 Ω、頻率為100 MHz時,核心電源電流(IDD 100M)最大為110 mA。輸入和輸出的電壓、電流、電容等參數也都有詳細的規定,這些參數對于電路設計和性能評估非常重要。

典型特性曲線

通過典型特性曲線,我們可以直觀地了解器件在不同工作條件下的性能變化。如LMK1D1208P的電流消耗與輸入頻率和電源電壓的關系曲線,以及差分輸出電壓(VOD)隨頻率的變化曲線。這些曲線為用戶在選擇合適的工作頻率和電源電壓時提供了重要參考。

應用與設計要點

典型應用場景

LMK1D1208P適用于多個領域,包括電信和網絡、醫療成像、測試與測量、無線基礎設施以及專業音頻、視頻和 signage等。在這些應用中,它能夠為系統提供高精度、低抖動的時鐘信號分配,確保各個子系統的同步運行。

設計要求與步驟

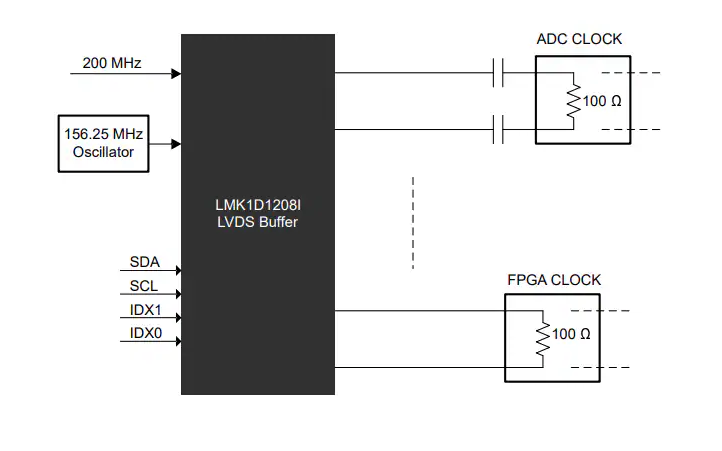

以典型的線卡應用為例,需要選擇合適的輸入信號,如156.25 - MHz的LVDS時鐘或LVCMOS時鐘。對于LVDS時鐘,采用AC耦合并使用集成的參考電壓發生器進行偏置;對于LVCMOS時鐘,使用電阻分壓器正確設置閾值電壓。輸入信號選擇后,可將其扇出到所需的設備,如PHY、ASIC、FPGA和CPU等。不同的設備可能需要不同的耦合方式和終端匹配,如PHY和ASIC具有內部終端匹配,無需額外組件;FPGA和CPU需要外部AC耦合電容。

在設計過程中,要注意輸入和輸出的終端匹配,確保信號完整性。對于未使用的輸出,應使用相應的OEx引腳將其禁用,以降低功耗并消除終端電阻的需求。同時,電源供應的濾波和去耦也非常關鍵,可使用濾波電容消除低頻噪聲,旁路電容提供高頻噪聲的低阻抗路徑。建議在電源引腳附近添加多個高頻旁路電容,并在板級電源和芯片電源之間插入鐵氧體磁珠,以隔離高頻開關噪聲。

PCB布局要點

良好的PCB布局對于器件的性能和可靠性至關重要。為了確保芯片的溫度在安全范圍內,需將芯片的裸片溫度限制在最大135°C以內。該器件的封裝有一個外露焊盤,它是主要的散熱路徑,需要在PCB封裝的焊盤內設計一個包含多個過孔到接地層的散熱焊盤圖案,并將散熱焊盤焊接到PCB上,以確保良好的散熱性能。同時,要注意布線的長度、間距和阻抗匹配,減少信號干擾和反射。

與其他同類產品對比

文檔中還給出了LMK1D1208P與其他同類產品的對比表格。不同的產品在輸出通道數量、輸出擺幅控制方式、封裝尺寸等方面存在差異。例如,LMK1D1208P通過引腳控制單個輸出使能,而部分產品采用全局輸出使能控制。在選擇產品時,需要根據具體的應用需求,綜合考慮這些因素,選擇最適合的器件。

總結

LMK1D1208P以其高性能、低抖動、靈活的引腳控制和廣泛的兼容性,為電子系統的時鐘分配提供了優秀的解決方案。在實際應用中,電子工程師需要深入理解其特性、規格和設計要點,合理進行電路設計和PCB布局,以充分發揮該器件的優勢,提高系統的性能和可靠性。你在使用這款器件或者類似的時鐘緩沖器時,遇到過哪些問題呢?歡迎在評論區分享。

-

時鐘分配

+關注

關注

0文章

19瀏覽量

8237 -

LVDS緩沖器

+關注

關注

0文章

27瀏覽量

1033

發布評論請先 登錄

LMK1D1208P引腳控制型OE低附加抖動LVDS緩沖器數據表

LMK1D1208低附加抖動、八路LVDS輸出時鐘緩沖器評估板

LMK1D2106/LMK1D2108 LVDS時鐘緩沖器技術解析與應用指南

高速時鐘分配新利器——LMK1D1208P LVDS緩沖器深度解析

高速時鐘分配新利器——LMK1D1208P LVDS緩沖器深度解析

評論