HMC7043:高性能時鐘分配器的技術(shù)解析與應(yīng)用指南

在電子設(shè)計領(lǐng)域,時鐘分配器對于確保系統(tǒng)的穩(wěn)定運行和高性能表現(xiàn)起著至關(guān)重要的作用。今天,我們將深入探討一款高性能的時鐘分配器——HMC7043,詳細解析其特性、工作原理、應(yīng)用場景以及編程配置等方面的內(nèi)容。

文件下載:HMC7043.pdf

一、HMC7043概述

HMC7043是一款專為高速數(shù)據(jù)轉(zhuǎn)換器設(shè)計的高性能時鐘緩沖器,支持并行或串行(JESD204B/C類型)接口。它能夠為系統(tǒng)提供超低相位噪聲的參考時鐘,適用于多種應(yīng)用場景,如基站設(shè)計、數(shù)據(jù)轉(zhuǎn)換時鐘等。

(一)主要特性

- JESD204B/C支持:該芯片支持JEDEC JESD204B和JESD204C標準,為高速數(shù)據(jù)傳輸提供了可靠的時鐘支持。

- 低抖動和低噪聲:具有極低的附加抖動,在2457.6 MHz時小于15 fs rms(12 kHz至20 MHz),噪聲底極低,如在983.04 MHz時為 -155.2 dBc/Hz。

- 多輸出配置:提供多達14個LVDS、LVPECL或CML類型的設(shè)備時鐘(DCLKs),最大CLKOUTx/CLKOUTx和SCLKOUTx/SCLKOUTx頻率可達3200 MHz。

- 獨立相位控制:每個輸出通道都具有獨立的相位控制功能,可通過模擬和數(shù)字延遲進行靈活調(diào)整。

- 同步功能:支持多個HMC7043設(shè)備的確定性同步,可通過RFSYNCIN引腳或SPI控制的SYNC觸發(fā)實現(xiàn)輸出同步。

- 可編程特性:通過SPI可編程調(diào)節(jié)噪聲底與功耗之間的平衡,還具有SYSREF有效中斷功能,簡化JESD204B同步。

(二)應(yīng)用場景

- JESD204B/C時鐘生成:為符合JESD204B/C標準的系統(tǒng)提供精確的時鐘信號。

- 蜂窩基礎(chǔ)設(shè)施:適用于多載波GSM、LTE、W - CDMA等蜂窩網(wǎng)絡(luò)基站設(shè)計。

- 數(shù)據(jù)轉(zhuǎn)換器時鐘:為數(shù)據(jù)轉(zhuǎn)換器提供穩(wěn)定的時鐘源,確保數(shù)據(jù)轉(zhuǎn)換的準確性。

- 相控陣參考分配:在相控陣系統(tǒng)中分配參考時鐘,保證各陣元的同步。

- 微波基帶卡:為微波基帶卡提供時鐘支持,提高系統(tǒng)性能。

二、工作原理

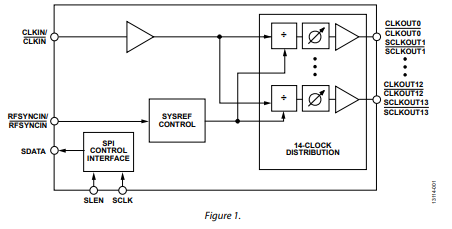

(一)整體架構(gòu)

HMC7043的設(shè)計旨在滿足多載波GSM和LTE基站的需求,提供了廣泛的時鐘管理和分配功能,簡化了基帶和無線電卡時鐘樹的設(shè)計。它通過內(nèi)部的時鐘分配路徑和輸出網(wǎng)絡(luò),將輸入的時鐘信號進行處理和分配,輸出到各個通道。

(二)時鐘輸入網(wǎng)絡(luò)

時鐘輸入網(wǎng)絡(luò)包括兩個時鐘和RFSYNC輸入緩沖器,它們共享相似的架構(gòu)和控制特性。輸入終止網(wǎng)絡(luò)可配置為100 Ω、200 Ω和2 kΩ差分,通常在板上采用AC耦合,并使用片上電阻分壓器將內(nèi)部共模電壓(V_{CM})設(shè)置為2.1 V。在正常使用時,建議使用100 Ω差分終止電阻來控制反射,并采用外部AC耦合輸入信號。

(三)時鐘輸出網(wǎng)絡(luò)

輸出網(wǎng)絡(luò)是HMC7043的核心部分,它需要滿足多個要求,如大量的設(shè)備時鐘(DCLK)和同步(SYSREF)通道、良好的相位噪聲底、各輸出通道之間的確定性相位對齊等。每個輸出通道都包含獨立的分頻器、相位調(diào)整和模擬延遲電路,可實現(xiàn)靈活的相位控制和頻率調(diào)整。

(四)同步機制

HMC7043通過RF SYNC輸入確保輸出信號與外部同步信號具有確定性的相位對齊。內(nèi)部的SYSREF定時器不斷運行,輸出通道分頻器的同步相對于該定時器進行確定性操作。用戶可以通過GPI或SPI對SYSREF定時器進行重新相位設(shè)置,以實現(xiàn)多個設(shè)備的同步。

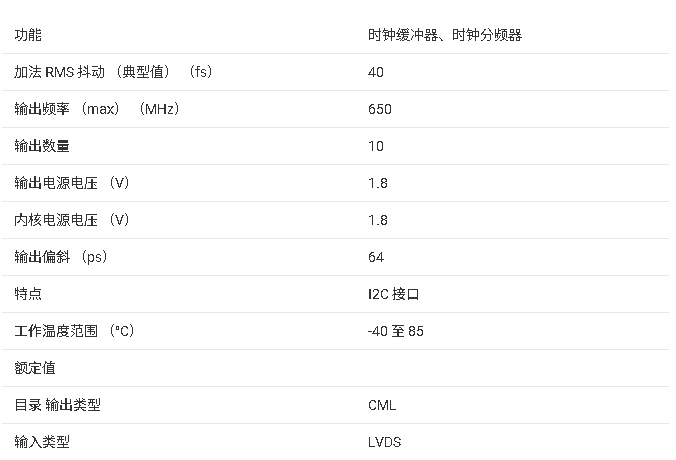

三、技術(shù)參數(shù)

(一)電源電壓

HMC7043的各個部分有不同的電源電壓要求,如VCC1_CLKDIST、VCC2_OUT等,均為3.3 V ± 5%。在設(shè)計電源電路時,需要確保各個電源引腳的電壓穩(wěn)定,以保證芯片的正常工作。

(二)電流消耗

不同電源引腳的電流消耗不同,如VCC1_CLKDIST典型電流為87 mA,最大為125 mA。在實際應(yīng)用中,需要根據(jù)具體的工作模式和配置來評估芯片的總電流消耗,以確保電源能夠提供足夠的功率。

(三)數(shù)字輸入/輸出電氣規(guī)格

包括數(shù)字輸入信號的邏輯高、低電平,SPI總線頻率,數(shù)字雙向信號的安全輸入電壓范圍、輸入電容等參數(shù)。這些參數(shù)對于與其他設(shè)備的接口設(shè)計非常重要,需要根據(jù)實際情況進行合理配置。

(四)時鐘輸出特性

- 時鐘輸出偏斜:CLKOUTx/CLKOUTx與SCLKOUTx/SCLKOUTx之間的偏斜在同一時鐘輸出對中最大為15 ps,任意CLKOUTx/CLKOUTx與任意SCLKOUTx/SCLKOUTx之間的偏斜最大為30 ps。

- 傳播延遲:CLKIN到CLKOUTx和SCLKOUTx的傳播延遲在770 - 870 ps之間(fCLKIN = 983.04 MHz,所有VCC設(shè)置為3.3 V)。

- 分頻器特性:12位分頻器范圍為1 - 4094,支持1、3、5和所有偶數(shù)分頻比,且奇數(shù)分頻比具有50.0%的占空比。

- 模擬和粗延遲:模擬精細延遲調(diào)整范圍為135 - 670 ps,分辨率為25 ps;粗延遲調(diào)整范圍根據(jù)不同的實現(xiàn)方式有所不同。

(五)輸出驅(qū)動特性

HMC7043支持多種輸出模式,如CML、LVPECL、LVDS和CMOS模式。不同模式下的-3 dB帶寬、輸出上升時間、下降時間、占空比、差分輸出電壓幅度等參數(shù)不同。在選擇輸出模式時,需要根據(jù)具體的應(yīng)用需求和負載特性進行考慮。

四、編程配置

(一)SPI控制

HMC7043通過3線串行端口接口(SPI)進行編程控制。SPI使用24位寄存器,包括1位讀寫命令、2位多字節(jié)字段、13位地址字段和8位數(shù)據(jù)字段。通過SPI可以實現(xiàn)對芯片的各種功能配置,如輸出通道的分頻比、相位調(diào)整、模式選擇等。

(二)控制寄存器

芯片的各種功能通過控制寄存器進行配置,包括全局控制、輸入緩沖控制、GPIO/SDATA控制、SYSREF/SYNC控制等多個寄存器組。每個寄存器組包含多個位,用于設(shè)置不同的功能參數(shù)。在進行編程時,需要根據(jù)具體的需求對相應(yīng)的寄存器位進行設(shè)置。

(三)典型編程序列

初始化HMC7043的典型編程序列包括連接額定電源、釋放硬件復(fù)位、加載配置更新、編程SYSREF定時器、編程輸出通道、提供時鐘輸入信號、進行軟件重啟、發(fā)送同步請求等步驟。在實際應(yīng)用中,需要按照這個序列進行操作,以確保芯片正常工作。

五、PCB設(shè)計和應(yīng)用注意事項

(一)PCB設(shè)計

在設(shè)計PCB時,需要采用RF電路設(shè)計技術(shù),確保信號線路具有50 Ω的阻抗。將封裝接地引腳和外露焊盤直接連接到接地平面,并使用足夠數(shù)量的過孔連接頂部和底部接地平面,以減少電磁干擾和信號損耗。

(二)ESD防護

HMC7043是靜電放電(ESD)敏感設(shè)備,盡管芯片具有專利或?qū)S?a href="http://www.3532n.com/tags/保護電路/" target="_blank">保護電路,但在操作過程中仍需要采取適當(dāng)?shù)腅SD防護措施,以避免性能下降或功能喪失。

(三)電源噪聲

輸出緩沖器對電源噪聲有一定的敏感性,需要注意電源的穩(wěn)定性和濾波。在設(shè)計電源電路時,可以采用適當(dāng)?shù)臑V波電容和電感,以減少電源噪聲對輸出信號的影響。

六、總結(jié)

HMC7043作為一款高性能的時鐘分配器,具有豐富的功能和優(yōu)異的性能。它在JESD204B/C系統(tǒng)、蜂窩基礎(chǔ)設(shè)施、數(shù)據(jù)轉(zhuǎn)換等領(lǐng)域有著廣泛的應(yīng)用前景。電子工程師在使用HMC7043時,需要深入了解其特性、工作原理和編程配置,合理設(shè)計PCB和電源電路,采取有效的防護措施,以充分發(fā)揮芯片的性能優(yōu)勢,實現(xiàn)系統(tǒng)的穩(wěn)定運行和高性能表現(xiàn)。

你在使用HMC7043的過程中遇到過哪些問題?對于它的性能和應(yīng)用還有哪些疑問?歡迎在評論區(qū)留言討論。

發(fā)布評論請先 登錄

高性能時鐘分配利器:LTC6953深度解析

深入剖析 LTC6954:高性能時鐘分配器的卓越之選

HMC7043B:高性能時鐘分配器的深度解析

核芯互聯(lián)正式發(fā)布國產(chǎn)高性能時鐘緩沖器芯片CLB7043

解析CDCL1810:高性能時鐘分配器的技術(shù)剖析與應(yīng)用指南

深入剖析LMK01000:高性能時鐘緩沖、分頻與分配器

CDCE62005:高性能時鐘發(fā)生器與分配器的深度剖析

深入解析CDCL1810A:高性能時鐘分配器的卓越之選

SN74AHCT138-EP 3線到8線解碼器/多路分配器:設(shè)計與應(yīng)用全解析

探索 SN74LVC138A:高性能 3 - 8 線譯碼器/分配器

探索DS90LV110AT:高性能LVDS數(shù)據(jù)/時鐘分配器的技術(shù)剖析

?CDCL1810高性能時鐘分配器技術(shù)文檔總結(jié)

?CDCL1810A 高性能時鐘分配器技術(shù)文檔總結(jié)

五路有源功率分配器 skyworksinc

HMC7043高性能、3.2 GHz、14輸出扇出緩沖器技術(shù)手冊

HMC7043:高性能時鐘分配器的技術(shù)解析與應(yīng)用指南

HMC7043:高性能時鐘分配器的技術(shù)解析與應(yīng)用指南

評論