ADSP-21560/21561/21564/21568:高性能SHARC+單核心DSP的深度剖析

在電子設(shè)計(jì)領(lǐng)域,高性能數(shù)字信號處理器(DSP)一直是實(shí)現(xiàn)復(fù)雜信號處理任務(wù)的核心組件。ADSP-21560/21561/21564/21568作為Analog Devices推出的SHARC+單核心高性能DSP,憑借其卓越的性能和豐富的功能,在汽車、消費(fèi)電子等多個(gè)領(lǐng)域展現(xiàn)出強(qiáng)大的應(yīng)用潛力。

文件下載:ADSP-21560.pdf

一、處理器概述

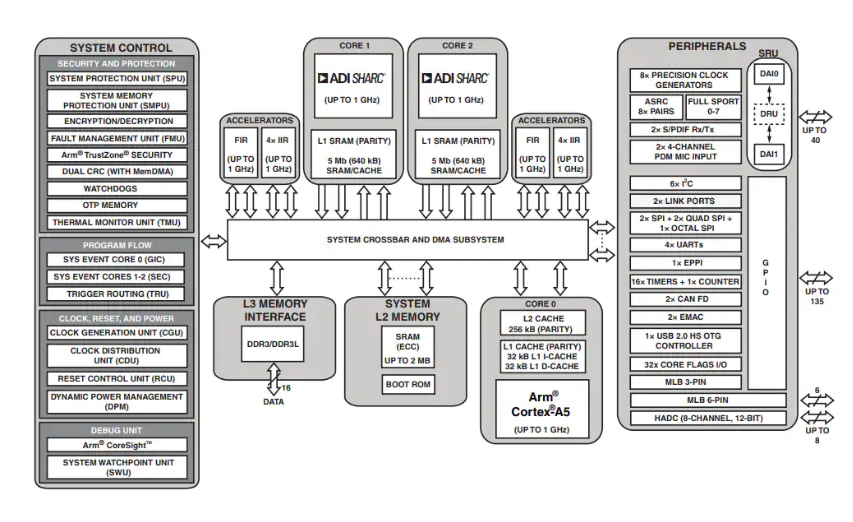

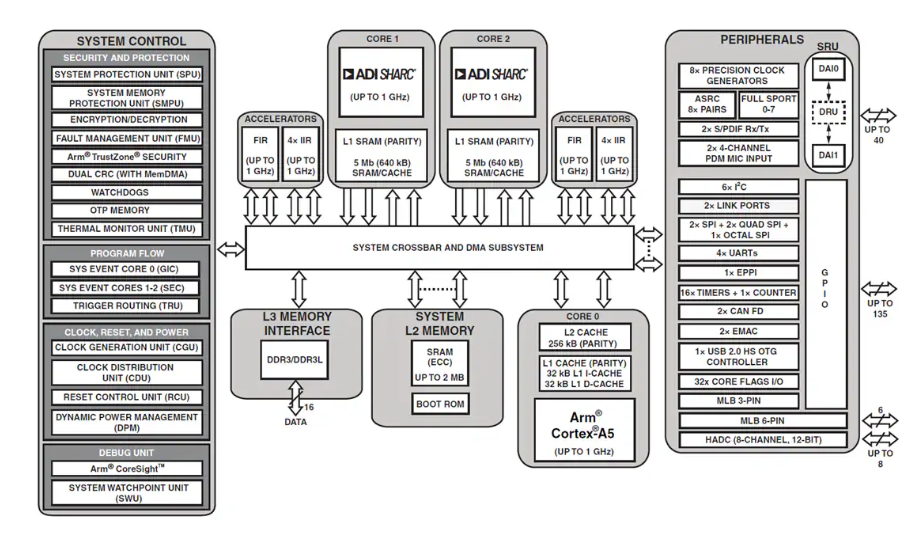

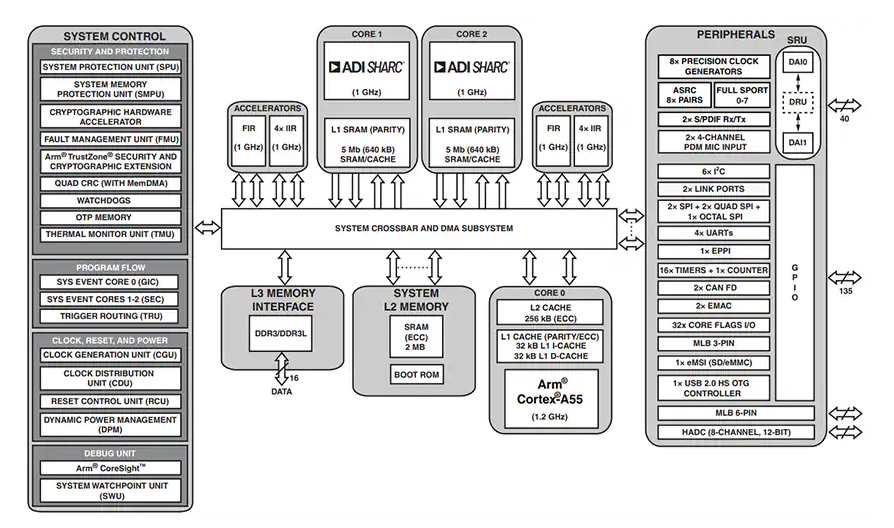

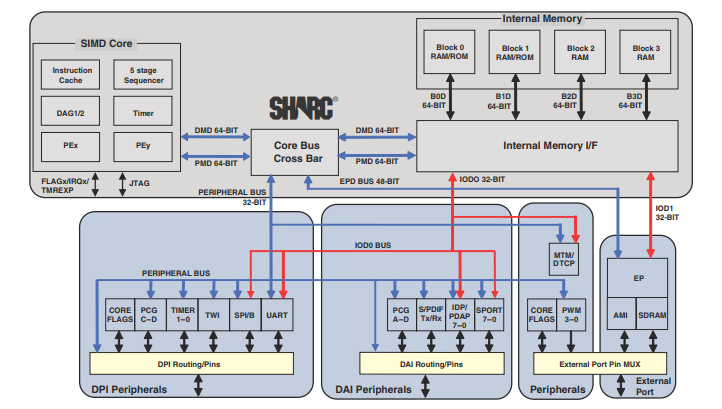

ADSP-21560/21561/21564/21568屬于SHARC?產(chǎn)品家族,基于SHARC+?單核心架構(gòu),具備高達(dá)1 GHz的處理速度。這些32位/40位/64位浮點(diǎn)處理器針對高性能音頻和浮點(diǎn)應(yīng)用進(jìn)行了優(yōu)化,擁有大容量片上靜態(tài)隨機(jī)存取存儲器(SRAM)、多條內(nèi)部總線以消除輸入/輸出(I/O)瓶頸,以及創(chuàng)新的數(shù)字音頻接口(DAI)。

1. 核心性能參數(shù)

不同型號的處理器在SHARC+核心的最大頻率、L1 SRAM和系統(tǒng)內(nèi)存L2 SRAM等方面存在差異。例如,ADSP-21568的SHARC+核心最大頻率可達(dá)1000 MHz,L1 SRAM為640 kB,系統(tǒng)內(nèi)存L2 SRAM為2048 kB。

2. 封裝選項(xiàng)

提供120 - 引腳LQFP_EP和400 - 球CSP_BGA兩種封裝選項(xiàng),以滿足不同應(yīng)用場景的需求。其中,400 - 球CSP_BGA封裝適用于ADSP - 21568,而其他型號則采用120 - 引腳LQFP_EP封裝。

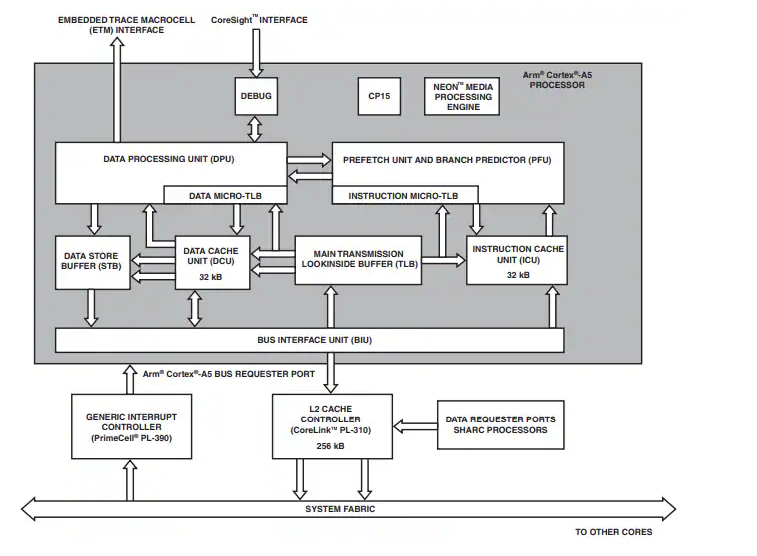

二、SHARC處理器架構(gòu)

1. 內(nèi)存架構(gòu)

SHARC處理器采用改進(jìn)的哈佛架構(gòu)和分層內(nèi)存結(jié)構(gòu)。L1內(nèi)存通常以全處理器速度運(yùn)行,延遲極小。SHARC+核心擁有緊密耦合的5 Mb L1 SRAM,可在單周期內(nèi)訪問代碼和數(shù)據(jù)。內(nèi)存可配置為不同的代碼和數(shù)據(jù)存儲組合,支持多種字長的訪問,包括8位、16位、32位、48位和64位。

2. 指令和數(shù)據(jù)緩存

處理器包含傳統(tǒng)的指令緩存(I - cache)和兩個(gè)數(shù)據(jù)緩存(D - cache),支持每CCLK周期進(jìn)行一次指令訪問和兩次數(shù)據(jù)訪問。緩存控制器自動管理配置的L1內(nèi)存,可獨(dú)立配置緩存大小,確保數(shù)據(jù)一致性,并提供用戶可控的功能,如全鎖定和部分鎖定、范圍邊界無效化和刷新。

3. 核心架構(gòu)

ADSP-21560/21561/21564/21568處理器與所有先前采用SHARC或SHARC+核心的SHARC處理器在匯編代碼上兼容。其SIMD架構(gòu)包含兩個(gè)計(jì)算處理單元(PEx和PEy),可作為單指令多數(shù)據(jù)(SIMD)引擎運(yùn)行,提高數(shù)學(xué)密集型DSP算法的執(zhí)行效率。

4. 其他特性

還具備額外的定時(shí)器、數(shù)據(jù)寄存器文件、上下文切換、通用寄存器、數(shù)據(jù)地址生成器(DAG)、靈活的指令集架構(gòu)(ISA)和可變指令集架構(gòu)(VISA)等特性,進(jìn)一步提升了處理器的性能和靈活性。

三、系統(tǒng)基礎(chǔ)設(shè)施

1. 系統(tǒng)L2內(nèi)存

提供高達(dá)16 Mb(2 MB)的系統(tǒng)L2 SRAM,可用于加速器和外設(shè)的源和目標(biāo)內(nèi)存、DMA描述符存儲、額外數(shù)據(jù)存儲以及數(shù)據(jù)系數(shù)表緩存,以避免外部內(nèi)存延遲和減少外部內(nèi)存帶寬。

2. 一次性可編程內(nèi)存(OTP)

具備7 kb的一次性可編程內(nèi)存,可用于存儲自定義密鑰,支持安全啟動和安全操作。

3. I/O內(nèi)存空間

映射的I/O包括SPI2或xSPI0內(nèi)存地址空間,為系統(tǒng)的外部通信提供了豐富的接口。

4. 系統(tǒng)交叉開關(guān)(SCBs)

作為片上系統(tǒng)總線互連的基本構(gòu)建塊,SCBs提供高效的流水線總線傳輸協(xié)議、全雙工總線操作、并發(fā)總線傳輸支持和選擇性總線互連保護(hù)。

5. 直接內(nèi)存訪問(DMA)

支持多種DMA操作,包括描述符基和寄存器基的DMA傳輸,可在內(nèi)存空間之間或內(nèi)存空間與外設(shè)之間高效傳輸數(shù)據(jù)。

6. 循環(huán)冗余校驗(yàn)(CRC)保護(hù)

CRC保護(hù)模塊可計(jì)算內(nèi)存中代碼、數(shù)據(jù)或兩者的簽名,并與預(yù)計(jì)算值進(jìn)行比較,觸發(fā)相應(yīng)的故障事件,提高系統(tǒng)的可靠性。

7. 事件處理

支持嵌套和優(yōu)先級的事件處理,可處理仿真事件、復(fù)位事件、異常事件和中斷事件,確保系統(tǒng)的穩(wěn)定運(yùn)行。

8. 系統(tǒng)事件控制器(SEC)

負(fù)責(zé)全面的系統(tǒng)事件源管理,包括中斷使能、故障使能、優(yōu)先級和源分組,提供確定性的事件傳播和唯一的事件源標(biāo)識。

9. 觸發(fā)路由單元(TRU)

提供系統(tǒng)級序列控制,可自動觸發(fā)DMA序列、軟件觸發(fā)和同步并發(fā)活動,提高系統(tǒng)的自動化程度。

四、安全特性

1. 加密硬件加速器

支持基于標(biāo)準(zhǔn)的硬件加速加密、解密、認(rèn)證和真隨機(jī)數(shù)生成,包括AES、DES、3DES、ARC4等加密算法和SHA - 1、SHA - 2、HMAC、MD5等哈希函數(shù)。

2. 系統(tǒng)保護(hù)單元(SPU)

提供寫保護(hù)機(jī)制,防止對MMR空間的意外或不必要訪問,并定義系統(tǒng)中的安全和非安全資源,阻止非安全請求者訪問安全資源。

3. 系統(tǒng)內(nèi)存保護(hù)單元(SMPU)

對定義的內(nèi)存區(qū)域提供讀寫保護(hù),確保系統(tǒng)內(nèi)存的安全性。

五、安全特性

1. 多奇偶校驗(yàn)位保護(hù)

SHARC+核心L1內(nèi)存、L2內(nèi)存和外設(shè)內(nèi)存均采用奇偶校驗(yàn)保護(hù),可檢測單事件翻轉(zhuǎn)和奇數(shù)個(gè)錯(cuò)誤位。

2. 循環(huán)冗余校驗(yàn)(CRC)保護(hù)

兩個(gè)CRC引擎嵌入在內(nèi)存到內(nèi)存DMA控制器中,可保護(hù)L1和L2內(nèi)存的系統(tǒng)錯(cuò)誤和靜態(tài)內(nèi)容,確保數(shù)據(jù)的完整性。

3. 信號看門狗

10個(gè)通用定時(shí)器可用于監(jiān)控外部信號的周期和脈沖寬度,檢測系統(tǒng)級信號的異常。

4. 系統(tǒng)事件控制器(SEC)

支持故障管理,包括故障動作配置、超時(shí)、內(nèi)部指示和系統(tǒng)復(fù)位,確保系統(tǒng)在出現(xiàn)故障時(shí)能夠及時(shí)響應(yīng)。

5. 內(nèi)存錯(cuò)誤控制器(MEC)

管理內(nèi)存奇偶校驗(yàn)/ECC錯(cuò)誤和警告,發(fā)送中斷和觸發(fā)信號,保障系統(tǒng)的穩(wěn)定性。

六、處理器外設(shè)

1. 數(shù)字音頻接口(DAI)

支持兩個(gè)DAI單元,可通過信號路由單元(SRU)連接各種外設(shè),提供靈活的音頻接口配置。

2. 串行端口(SPORT)

具備八個(gè)同步串行端口,可與多種數(shù)字和混合信號外設(shè)設(shè)備接口,支持多種串行通信模式。

3. 異步采樣率轉(zhuǎn)換器(ASRC)

包含八個(gè)ASRC塊,可提供高達(dá)140 dB的信噪比,實(shí)現(xiàn)同步或異步采樣率轉(zhuǎn)換,確保音頻數(shù)據(jù)的高質(zhì)量處理。

4. S/PDIF - 兼容數(shù)字音頻接收器/發(fā)射器

支持標(biāo)準(zhǔn)的音頻數(shù)據(jù)傳輸格式,可實(shí)現(xiàn)數(shù)字音頻信號的傳輸,支持多種采樣率和專業(yè)抖動標(biāo)準(zhǔn)。

5. 精密時(shí)鐘發(fā)生器(PCG)

由四個(gè)單元組成,可生成時(shí)鐘和幀同步信號,為系統(tǒng)提供精確的時(shí)鐘源。

6. 通用異步接收器/發(fā)射器(UART)端口

提供全雙工UART端口,支持多種數(shù)據(jù)位和奇偶校驗(yàn),可實(shí)現(xiàn)異步串行數(shù)據(jù)傳輸。

7. 串行外設(shè)接口(SPI)端口

具備三個(gè)SPI - 兼容端口,支持多種操作模式和配置選項(xiàng),可與多個(gè)SPI - 兼容設(shè)備通信。

8. xSPI與八進(jìn)制和HyperBus支持

xSPI0端口提供更高的外部內(nèi)存數(shù)據(jù)總線寬度和雙數(shù)據(jù)速率(DDR)操作模式,提高系統(tǒng)的整體數(shù)據(jù)吞吐量和性能。

9. 定時(shí)器

包括通用定時(shí)器、看門狗定時(shí)器和通用計(jì)數(shù)器,可用于定時(shí)、監(jiān)控和計(jì)數(shù)等功能。

10. 媒體本地總線(MediaLB)

汽車型號具備MediaLB設(shè)備接口,支持3 - 引腳媒體本地總線協(xié)議,可實(shí)現(xiàn)高速數(shù)據(jù)傳輸。

11. 2 - 線控制器接口(TWI)

提供簡單的控制數(shù)據(jù)交換方法,兼容I2C總線標(biāo)準(zhǔn),支持7 - 位尋址和多媒體數(shù)據(jù)仲裁。

12. 通用I/O(GPIO)

每個(gè)GPIO引腳可單獨(dú)控制,支持輸入/輸出方向設(shè)置、中斷功能和電平/邊緣敏感設(shè)置。

七、系統(tǒng)加速

1. 有限脈沖響應(yīng)(FIR)加速器

由1024字系數(shù)內(nèi)存、1024字深度延遲線和四個(gè)乘法累加器(MAC)單元組成,可在核心時(shí)鐘頻率下運(yùn)行,與IIR加速器并發(fā)工作。

2. 無限脈沖響應(yīng)(IIR)加速器

包含1440字系數(shù)內(nèi)存和一個(gè)MAC單元,同樣可在核心時(shí)鐘頻率下運(yùn)行,與其他加速器并發(fā)工作。

八、系統(tǒng)設(shè)計(jì)

1. 時(shí)鐘管理

提供三種操作模式,通過控制處理器外設(shè)的時(shí)鐘來降低功耗。

2. 復(fù)位控制單元(RCU)

控制所有功能單元的復(fù)位和退出復(fù)位過程,確保系統(tǒng)在復(fù)位時(shí)處于定義狀態(tài)。

3. 時(shí)鐘生成單元(CGU)

支持一個(gè)PLL,可根據(jù)外部時(shí)鐘源靈活確定內(nèi)部時(shí)鐘頻率。

4. 系統(tǒng)晶體振蕩器

可由外部晶體、正弦波輸入或緩沖時(shí)鐘驅(qū)動,確保系統(tǒng)時(shí)鐘的穩(wěn)定性。

5. 時(shí)鐘分配單元(CDU)

將時(shí)鐘輸出分配到各個(gè)目標(biāo),確保時(shí)鐘信號的準(zhǔn)確傳輸。

6. 時(shí)鐘輸出/外部時(shí)鐘

SYS_CLKOUT輸出引腳可輸出分頻后的片上時(shí)鐘,提供靈活的時(shí)鐘配置選項(xiàng)。

7. 啟動

支持多種啟動模式,包括閃存啟動和外部主機(jī)啟動,可實(shí)現(xiàn)自動加載內(nèi)部和外部內(nèi)存。

8. 電源供應(yīng)

具備獨(dú)立的內(nèi)部、外部I/O和PLL/OTP高電壓電源供應(yīng),確保系統(tǒng)的穩(wěn)定運(yùn)行。

9. 電源管理

支持三種不同的電源域,可根據(jù)系統(tǒng)需求靈活調(diào)整功耗。

10. 目標(biāo)板JTAG仿真器連接器

通過IEEE 1149.1 JTAG測試訪問端口,可實(shí)現(xiàn)對目標(biāo)板處理器的監(jiān)控和控制。

九、系統(tǒng)調(diào)試

處理器提供調(diào)試訪問端口(DAP),支持IEEE 1149.1 JTAG接口,方便進(jìn)行系統(tǒng)調(diào)試。

十、開發(fā)工具

Analog Devices為該處理器提供了完整的軟件和硬件開發(fā)工具,包括集成開發(fā)環(huán)境(IDE)、評估產(chǎn)品、仿真器和各種軟件插件,幫助工程師快速開發(fā)和調(diào)試應(yīng)用程序。

十一、總結(jié)

ADSP-21560/21561/21564/21568處理器以其高性能、豐富的功能和強(qiáng)大的安全特性,為電子工程師在汽車、消費(fèi)電子等領(lǐng)域的設(shè)計(jì)提供了理想的解決方案。通過深入了解其架構(gòu)和特性,工程師可以充分發(fā)揮處理器的優(yōu)勢,實(shí)現(xiàn)更加復(fù)雜和高效的信號處理應(yīng)用。在實(shí)際設(shè)計(jì)中,我們需要根據(jù)具體的應(yīng)用需求,合理選擇處理器型號和配置,優(yōu)化系統(tǒng)設(shè)計(jì),以確保系統(tǒng)的性能和可靠性。同時(shí),借助Analog Devices提供的開發(fā)工具,我們可以更加高效地進(jìn)行開發(fā)和調(diào)試,縮短產(chǎn)品的開發(fā)周期。大家在使用這款處理器的過程中,有沒有遇到什么特別的問題或者有什么獨(dú)特的應(yīng)用經(jīng)驗(yàn)?zāi)兀繗g迎在評論區(qū)分享交流。

-

信號處理

+關(guān)注

關(guān)注

49文章

1147瀏覽量

105155

發(fā)布評論請先 登錄

深入剖析ADSP-21990:高性能混合信號DSP控制器的卓越之選

ADSP - 21992:高性能混合信號 DSP 控制器的深度剖析

ADSP-21593/21594/ADSP-SC592/SC594處理器:高性能與多功能的完美融合

高性能音頻處理利器:ADSP - 21477/ADSP - 21478/ADSP - 21479處理器深度解析

ADSP - 21467/ADSP - 21469 SHARC處理器:高性能音頻處理的理想之選

探索ADSP - 21371/ADSP - 21375 SHARC處理器:高性能音頻處理的利器

ADSP - 21369 SHARC處理器:高性能音頻處理的理想之選

深入剖析ADSP - 2136x SHARC處理器:高性能音頻處理的理想之選

深度解析ADSP-2126x:高性能音頻處理的理想之選

ADSP1802 SHARC處理器:高性能音頻處理的理想之選

Analog Devices Inc. ADSP-21591/ADSP-21593 SHARC+ 雙核DSP數(shù)據(jù)手冊

Analog Devices Inc. ADSP-21594/ADSP-SC594 SHARC+雙核DSP數(shù)據(jù)手冊

Analog Devices Inc. ADSP-SC598雙SHARC+?數(shù)字信號處理器數(shù)據(jù)手冊

Analog Devices Inc. ADSP-SC592 SHARC+?雙核DSP數(shù)據(jù)手冊

ADSP-21371/ADSP-21375面向汽車音頻的32位高性能浮點(diǎn)SHARC處理器技術(shù)手冊

ADSP-21560/21561/21564/21568:高性能SHARC+單核心DSP的深度剖析

ADSP-21560/21561/21564/21568:高性能SHARC+單核心DSP的深度剖析

評論