概述

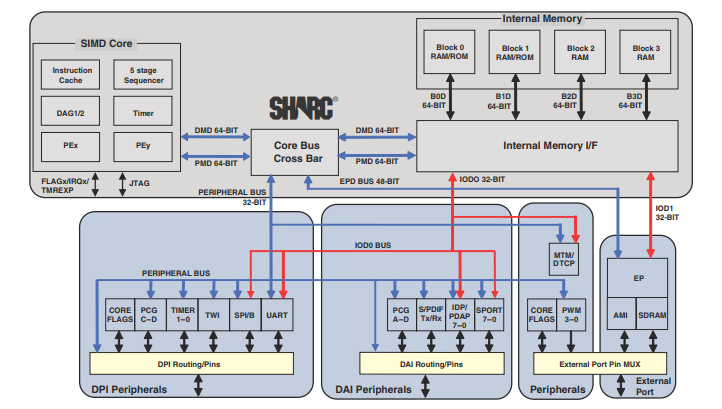

第三代SHARC?處理器,其中包括ADSP-21375和ADSP-21371,提供了更高的性能、以音頻和應用為重點的外設和存儲器配置,能夠支持環(huán)繞聲解碼器算法。所有的器件與其它SHARC處理器如ADSP-21367和ADSP-21369在引腳和代碼方面完全兼容。這些SHARC處理器基于一個單指令多數(shù)據(jù)(SIMD)內(nèi)核,支持32位定點和32/40位浮點運算格式,使它們特別適合于高性能音頻應用。

在第三代SHARC處理器系列中,ADSP-21371能以極低的成本提供266 MHz/1596 MFLOP的高性能。這樣的性能水平使ADSP - 21371特別適合于解決日益增長的專業(yè)和車載音響市場需求,同時保持了低成本。除了更高的內(nèi)核性能,ADSP-21371包含了更多的增值外設如S/PDIF發(fā)射器/接收器。ADSP-21371還提供一個運行于133 MHz的32位接口,可直接與同步SDRAM接口。

第三代SHARC處理器還集成了專用的外設,旨在簡化硬件設計,較大限度地減少設計風險,并最終縮短上市時間。這些功能模塊組合起來,加上廣為人知的數(shù)字音頻接口(DAI),通過軟件可編程的信號路由單元(SRU)可以彼此連接或連接至外部引腳。SRU是一個創(chuàng)新的架構特性,可以在DAI模塊之間實現(xiàn)完整而靈活的路由。通過SRU連接的外設包括但不限于:串行接口、SPI端口和S/PDIF Tx/Rx。

數(shù)據(jù)表:*附件:ADSP-21371 ADSP-21375面向汽車音頻的32位高性能浮點SHARC處理器技術手冊.pdf

特性

- 266 MHz SIMD SHARC內(nèi)核,峰值性能可達到1596 MFLOPS

- 1Mb SRAM、內(nèi)嵌行業(yè)標準音頻解碼和后處理系數(shù)的4 Mb ROM

- 32位DMA以外設時鐘速度傳送,與全速處理器執(zhí)行并行

- 32位寬外部端口提供與同步(SDRAM)和異步存儲器的無膠合接口

- 數(shù)字音頻接口(DAI)可實現(xiàn)對于外設的用戶可定義訪問,包括S/PDIF Tx/Rx

- 從主存儲器直接執(zhí)行

- 延遲線DMA引擎通過抽頭/偏移的讀取來維護外部存儲器的循環(huán)緩沖區(qū)

- 8個支持I2S、左對齊采樣對和TDM模式的串行端口

- 兩個支持主和從模式的SPI端口

- 16個PWM通道

- 3個全特性定時器

- 208引腳LQFP EP封裝:商業(yè)和工業(yè)溫度范圍

框圖

SHARC系列核心架構

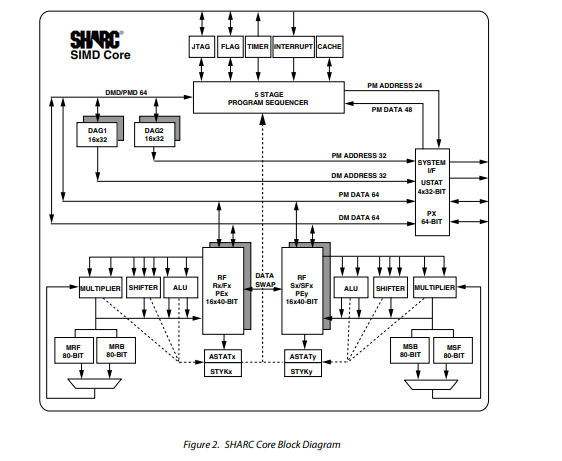

ADSP - 21371/ADSP - 21375處理器在匯編層面上與ADSP - 2136x、ADSP - 2126x、ADSP - 21160以及第一代ADSP - 216x SHARC處理器代碼兼容。ADSP - 21371/ADSP - 21375處理器與ADSP - 2136x、ADSP - 2126x和ADSP - 2116x SIMD SHARC處理器共享架構特性, 如圖2所示,并在以下部分詳細介紹。

SIMD計算引擎

這些處理器包含兩個計算處理單元,它們作為單指令多數(shù)據(jù)(SIMD)引擎運行。處理單元被稱為PEX和PEY,每個單元都包含一個算術邏輯單元(ALU)、一個乘法器、一個移位器以及寄存器文件。PEX始終處于活動狀態(tài),并且可以通過設置PEYEN位在MODE1寄存器中啟用PEY。啟用此模式后,相同的指令會在兩個處理單元上執(zhí)行,但每個處理單元對不同的數(shù)據(jù)進行操作。這種架構在執(zhí)行數(shù)學密集型數(shù)字信號處理(DSP)算法時效率很高。

進入SIMD模式也會影響數(shù)據(jù)在內(nèi)存和處理單元之間的傳輸方式。在SIMD模式下,傳輸數(shù)據(jù)需要雙倍的帶寬,以便在處理單元中進行計算操作。由于這種需求,內(nèi)存SIMD模式還會使內(nèi)存與處理單元之間的帶寬翻倍。當使用DAGs在SIMD模式下傳輸數(shù)據(jù)時,會傳輸兩個數(shù)據(jù)值,以匹配每個操作模式的雙倍速率。

獨立的并行計算單元

每個處理單元都包含一組計算單元。這些計算單元由一個算術邏輯單元(ALU)、一個乘法器和一個移位器組成。這些單元在單個周期內(nèi)執(zhí)行所有操作。這三個單元在每個處理單元內(nèi)并行排列,最大限度地提高了整體計算吞吐量。單指令多操作(SIMO)執(zhí)行并行的ALU和乘法器操作。在SIMD模式下,并行的ALU和乘法器操作會在兩個處理單元上同時執(zhí)行。這些計算單元支持IEEE 32位單精度浮點、40位擴展精度浮點和32位定點數(shù)據(jù)格式。

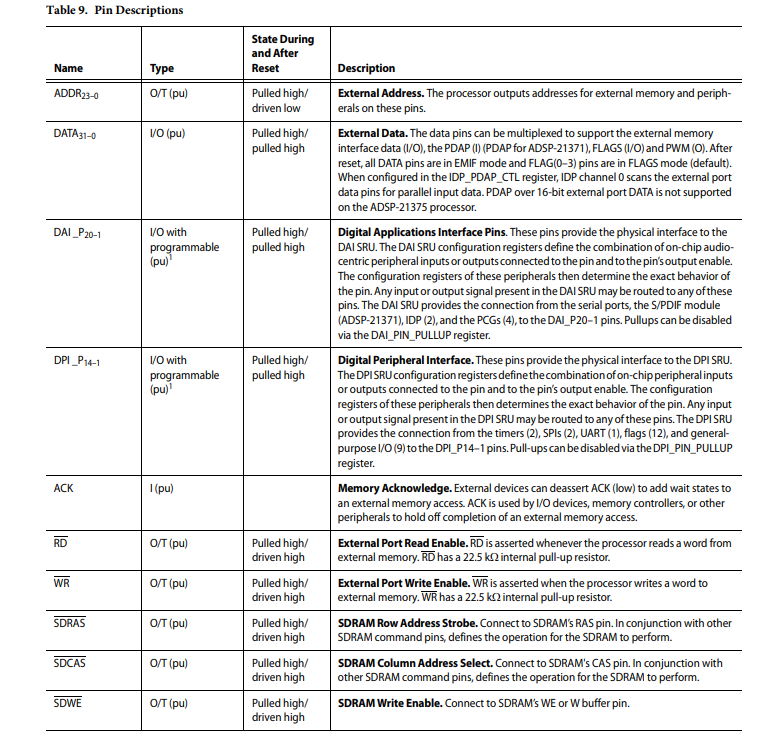

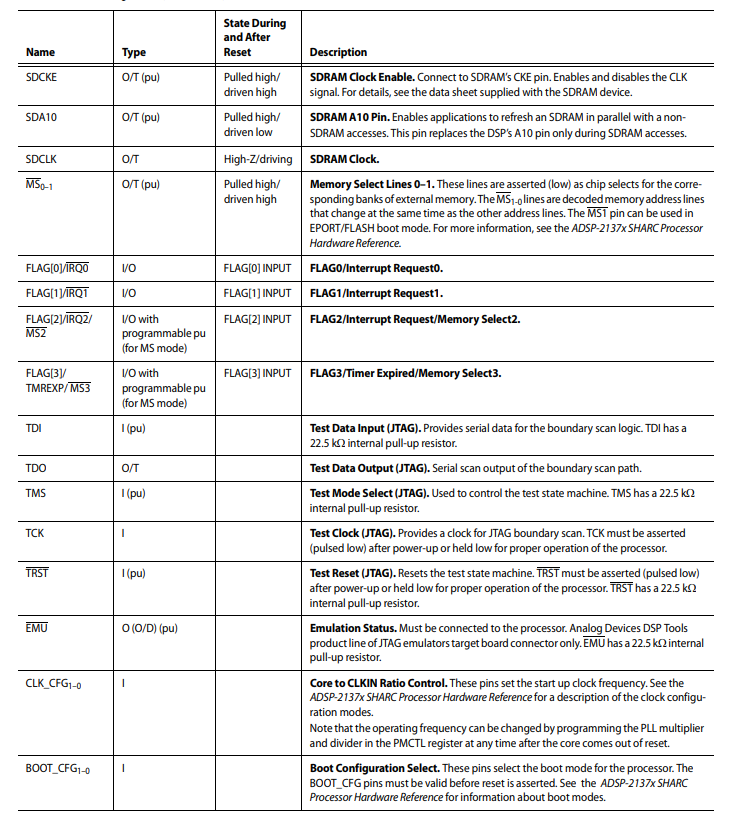

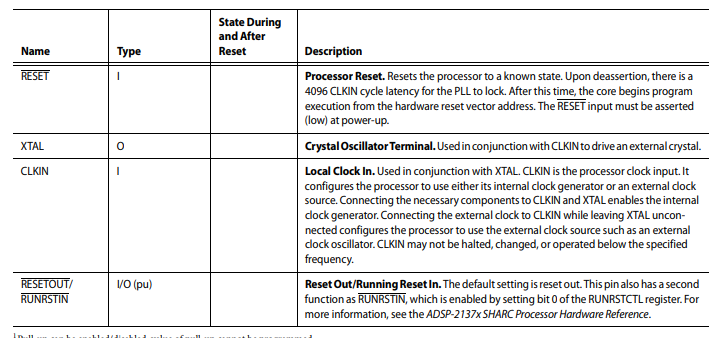

引腳功能描述

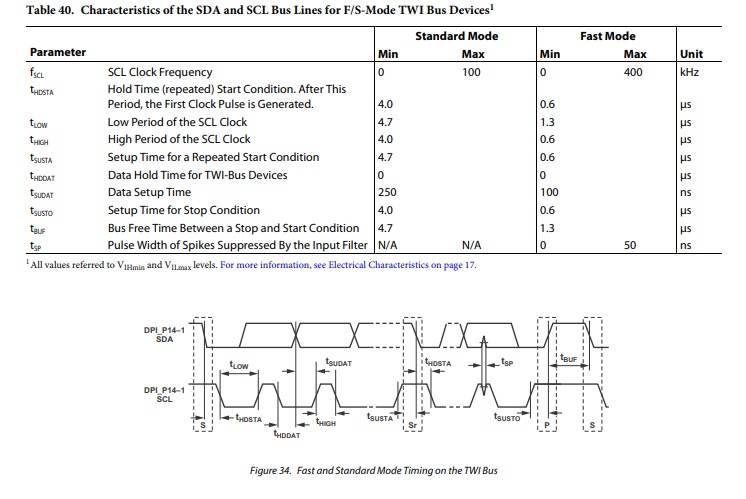

TWI控制器時序

表40和圖34提供了TWI接口的時序信息。輸入信號(SCL、SDA)被路由到DP - P14 - 1引腳上,其時序規(guī)范在本數(shù)據(jù)手冊的其他地方給出。

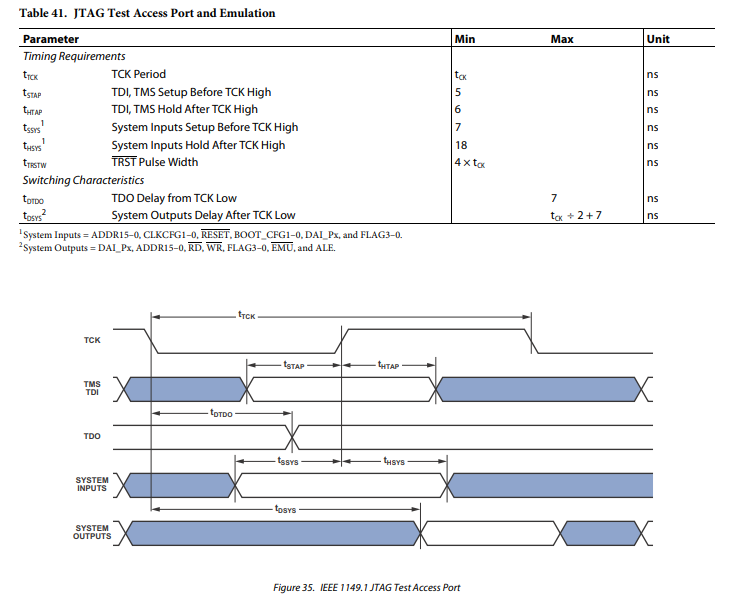

JTAG測試接入端口和仿真

-

處理器

+關注

關注

68文章

20286瀏覽量

253261 -

音頻

+關注

關注

31文章

3206瀏覽量

85834 -

SHARC處理器

+關注

關注

0文章

57瀏覽量

7871

發(fā)布評論請先 登錄

ADSP-21371 面向汽車音頻的32位高性能浮點SHARC處理器

ADSP-21375 32位高性能浮點SHARC處理器

ADSP-21371/ADSP-21375 SHARC處理器數(shù)據(jù)表

EE-266:在ADSP-2136x和ADSP-21371 SHARC?處理器上編程S/PDIF

ADSP-21375 EZ-KIT精簡版,用于ADSP-2137x SHARC處理器產(chǎn)品亮點

21375-EZ ADSP-21375 EZ-Kit Lite評估硬件為評估ADSP-21371和ADSP-21375 SHARC處理器系列提供低成本硬件解決方案。

EE-319:估算ADSP-21375 SHARC處理器的功耗

EE-266:在ADSP-2136x和ADSP-21371 SHARC處理器上對S/PDIF進行編程

EE-285: 從ADSP-21065L轉向使用ADSP-21375 SHARC處理器

EE-318:估算ADSP-21371 SHARC處理器的功耗

ADSP-21371/ADSP-21375面向汽車音頻的32位高性能浮點SHARC處理器技術手冊

ADSP-21371/ADSP-21375面向汽車音頻的32位高性能浮點SHARC處理器技術手冊

評論