ADSP - 21369 SHARC處理器:高性能音頻處理的理想之選

在電子工程領域,高性能處理器對于實現復雜的音頻處理等任務至關重要。ADSP - 21369 SHARC處理器就是這樣一款具有卓越性能的產品,下面我們就來詳細了解一下它的特點、架構以及應用。

文件下載:ADSP-21369.pdf

一、產品概述

ADSP - 21369是一款高性能的32位/40位浮點處理器,專為高性能音頻處理進行了優化。它采用單指令多數據(SIMD)計算架構,擁有2M位的片上SRAM和6M位的片上掩膜可編程ROM,并且與SHARC系列的其他成員代碼兼容。其核心指令速率可達400 MHz,還配備了如數字應用接口、S/PDIF收發器、串口、8通道異步采樣率轉換器、精密時鐘發生器等獨特的以音頻為中心的外設。

產品特性

| 特性 | ADSP - 21369 |

|---|---|

| 頻率 | 400 MHz |

| RAM | 2M位 |

| ROM | 6M位 |

| 脈沖寬度調制 | 支持 |

| S/PDIF | 支持 |

| SDRAM內存總線寬度 | 32位/16位 |

| 串口 | 8個 |

| IDP | 支持 |

| DAI | 支持 |

| UART | 2個 |

| DPI | 支持 |

| S/PDIF收發器 | 1個 |

| AMI接口總線寬度 | 32位/16位/8位 |

| SPI | 2個 |

| TWI | 支持 |

| SRC性能 | 128 dB |

| 共享內存支持 | 僅256球BGA |

| 封裝 | 256球BGA、208引腳LQFP_EP |

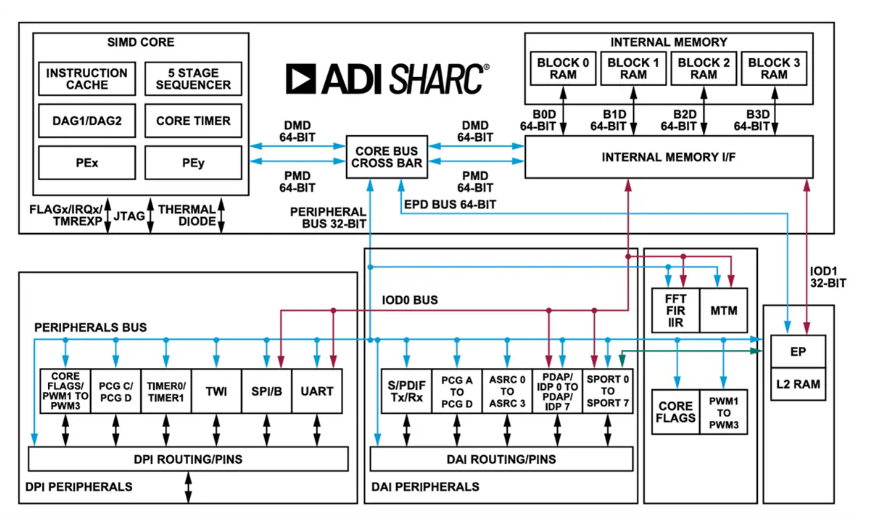

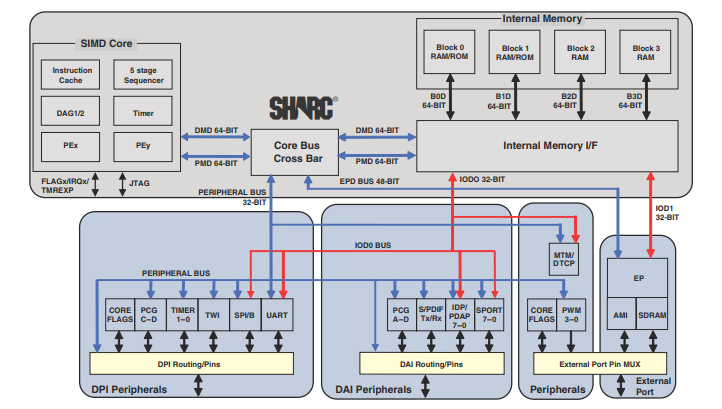

二、核心架構

SIMD計算引擎

該處理器包含兩個計算處理單元,作為單指令多數據(SIMD)引擎運行。處理單元PEX和PEY各自包含一個ALU、乘法器、移位器和寄存器文件。PEX始終處于活動狀態,PEY可通過設置MODE1寄存器中的PEYEN模式位來啟用。進入SIMD模式后,兩個處理單元執行相同的指令,但處理不同的數據,這對于執行數學密集型的DSP算法非常高效。同時,進入SIMD模式會使內存與處理單元之間的數據帶寬翻倍。

獨立并行計算單元

每個處理單元內都有一組計算單元,包括算術邏輯單元(ALU)、乘法器和移位器。這些單元在單個周期內執行所有操作,并且三個單元并行排列,最大限度地提高了計算吞吐量。在SIMD模式下,并行的ALU和乘法器操作會在兩個處理單元中同時發生,并且支持IEEE 32位單精度浮點、40位擴展精度浮點和32位定點數據格式。

數據寄存器文件

每個處理單元都包含一個通用數據寄存器文件,用于在計算單元和數據總線之間傳輸數據,并存儲中間結果。這些10端口、32寄存器(16個主寄存器,16個輔助寄存器)的寄存器文件,結合ADSP - 21369處理器的增強哈佛架構,允許計算單元和內部內存之間無約束的數據流。

上下文切換

處理器的許多寄存器都有輔助寄存器,可在中斷服務期間激活以實現快速上下文切換。數據寄存器、DAG寄存器和乘法器結果寄存器都有輔助寄存器,主寄存器在復位時激活,輔助寄存器由模式控制寄存器中的控制位激活。

通用寄存器

USTAT(4)寄存器允許對核心的所有系統寄存器(控制/狀態)進行簡單的位操作(設置、清除、切換、測試、異或)。數據總線交換寄存器(PX)允許在64位PM數據總線和64位DM數據總線之間,或在40位寄存器文件和PM數據總線之間傳遞數據。

定時器

核心定時器可以生成周期性軟件中斷,并可配置為使用FLAG3作為定時器過期信號。

單周期取指令和四個操作數

處理器采用增強哈佛架構,數據內存(DM)總線傳輸數據,程序內存(PM)總線傳輸指令和數據。通過獨立的程序和數據內存總線以及片上指令緩存,處理器可以在單個周期內同時獲取四個操作數(每個數據總線兩個)和一條指令(從緩存中)。

指令緩存

片上指令緩存支持三總線操作,用于獲取一條指令和四個數據值。緩存僅對與PM總線數據訪問沖突的指令進行緩存,允許核心循環操作(如數字濾波器乘法累加和FFT蝶形處理)全速執行。

數據地址生成器

處理器有兩個數據地址生成器(DAGs),用于間接尋址和在硬件中實現循環數據緩沖區。循環緩沖區允許高效編程數字信號處理中所需的延遲線和其他數據結構,常用于數字濾波器和傅里葉變換。兩個DAGs包含足夠的寄存器,可創建多達32個循環緩沖區(16個主寄存器集,16個輔助寄存器集),并自動處理地址指針回繞,減少開銷,提高性能,簡化實現。

靈活的指令集

48位指令字可容納各種并行操作,實現簡潔編程。例如,ADSP - 21369處理器可以在兩個處理單元中有條件地執行乘法、加法和減法,同時分支并從內存中獲取多達四個32位值,所有這些都在一條指令中完成。

三、片上內存

處理器包含2M位的內部RAM和6M位的內部掩膜可編程ROM,每個塊都可以配置為不同的代碼和數據存儲組合。每個內存塊支持核心處理器和I/O處理器的單周期獨立訪問,內存架構結合獨立的片上總線,允許在單個周期內從核心進行兩次數據傳輸,從I/O處理器進行一次數據傳輸。

內存帶寬

內部內存架構允許程序同時對四個塊中的任何一個進行四次訪問(假設沒有塊沖突)。總帶寬通過DMD和PMD總線(2 × 64位,核心CLK)和IOD0/1總線(2 × 32位,PCLK)實現。

ROM安全特性

處理器具有ROM安全特性,通過防止在啟用時從內部代碼進行未經授權的讀取來為用戶軟件代碼提供硬件支持。使用此功能時,處理器不會加載任何外部代碼,僅從內部ROM執行。此外,處理器不能通過JTAG端口自由訪問,每個客戶將分配一個唯一的64位密鑰,必須通過JTAG或測試訪問端口掃描輸入,設備將忽略錯誤的密鑰,只有在掃描正確的密鑰后,仿真功能和外部引導模式才可用。

四、外設架構

外部端口

外部端口接口支持通過核心和DMA訪問外部內存,外部內存地址空間分為四個銀行。任何銀行都可以編程為異步或同步內存。外部端口由異步內存接口(AMI)、SDRAM控制器、仲裁邏輯和共享內存接口組成。

SDRAM控制器

SDRAM控制器提供與多達四個獨立的行業標準SDRAM設備或DIMM的接口,速度可達 (f_{SCLK }) 。每個銀行有自己的內存選擇線(MS0 - MS3),可以配置為包含16M字節到128M字節的內存。

外部內存

外部端口提供與各種行業標準內存設備的高性能、無膠合接口。32位寬的總線可通過其獨立的內部內存控制器連接到同步和/或異步內存設備。

共享外部內存

ADSP - 21369處理器支持與其他ADSP - 21369處理器連接到公共共享外部內存,以創建共享外部總線處理器系統。支持分布式、片上仲裁、固定和旋轉優先級總線仲裁、總線超時邏輯和總線鎖定。

脈沖寬度調制(PWM)

PWM模塊是一個靈活的、可編程的PWM波形發生器,可編程為生成各種與電機和發動機控制或音頻功率控制相關的應用所需的開關模式。整個PWM模塊有四組,每組四個PWM輸出,共生成16個PWM輸出。PWM發生器可以生成中心對齊或邊緣對齊的PWM波形,并在生成中心對齊的PWM波形時可以在單更新模式或雙更新模式下運行。

數字應用接口(DAI)

DAI提供了將各種外設連接到DSP的DAI引腳的能力。通過信號路由單元(SRU),程序可以在軟件控制下互連DAI提供的外設。DAI包括八個串口、一個S/PDIF收發器、四個精密時鐘發生器(PCG)、八個通道的同步采樣率轉換器和一個輸入數據端口(IDP)。

串口

處理器具有八個同步串口(SPORTs),提供與各種數字和混合信號外設設備的低成本接口。串口由兩條數據線、一個時鐘和幀同步組成,數據線可以編程為發送或接收,每個數據線都有一個專用的DMA通道。串口可以在標準DSP串行模式、多通道(TDM)模式、I2S模式、打包I2S模式和左對齊樣本對模式下運行。

S/PDIF兼容數字音頻收發器

S/PDIF收發器沒有單獨的DMA通道,它接收串行格式的音頻數據并將其轉換為雙相編碼信號。串行數據輸入可以格式化為左對齊、I2S或右對齊,字寬為16、18、20或24位。

同步/異步采樣率轉換器(SRC)

SRC包含四個SRC塊,與AD1896 192 kHz立體聲異步采樣率轉換器使用相同的核心,提供高達128 dB的SNR。SRC塊可用于在獨立立體聲通道上執行同步或異步采樣率轉換,而無需使用內部處理器資源。

輸入數據端口(IDP)

IDP提供多達八個串行輸入通道,每個通道都有自己的時鐘、幀同步和數據輸入。八個通道自動復用為一個32位、深度為8的FIFO。數據始終格式化為64位幀,并分為兩個32位字。

精密時鐘發生器(PCG)

PCG由四個單元組成,每個單元從時鐘輸入信號生成一對信號(時鐘和幀同步)。這些單元功能相同且相互獨立,生成的兩個信號通常用作串行位時鐘/幀同步對。

數字外設接口(DPI)

DPI提供與兩個串行外設接口端口(SPI)、兩個通用異步接收器 - 發送器(UARTs)、一個2線接口(TWI)、12個標志和三個通用定時器的連接。

五、I/O處理器特性

DMA控制器

處理器的片上DMA控制器允許在無需處理器干預的情況下進行數據傳輸。DMA控制器獨立于處理器核心運行,允許在核心同時執行程序指令時進行DMA操作。ADSP - 2136x處理器有34個DMA通道,可用于處理器內部內存與串口、SPI兼容端口、IDP、并行數據采集端口(PDAP)或UART之間的數據傳輸。

延遲線DMA

處理器提供延遲線DMA功能,允許處理器以有限的核心交互讀寫外部延遲線緩沖區(在外部內存、SRAM或SDRAM中)。

六、系統設計

程序引導

處理器的內部內存可以在系統上電時從8位EPROM通過外部端口、SPI主設備或從設備或內部引導啟動。引導模式由引導配置(BOOT_CFG1 - 0)引腳確定。

電源供應

處理器有獨立的內部( (V{DDOST }) )、外部( (V{DDEXT }) )和模擬( (A{VDD} / A{Vss}) )電源供應連接。內部和模擬電源必須滿足400 MHz設備的1.3 V要求,333 MHz和266 MHz設備的1.2 V要求,外部電源必須滿足3.3 V要求。

七、開發工具

Analog Devices為其處理器提供了完整的軟件和硬件開發工具,包括集成開發環境(如CrossCore? Embedded Studio和VisualDSP++?)、評估產品、仿真器和各種軟件插件。

集成開發環境(IDEs)

CrossCore Embedded Studio基于EclipseTM框架,支持大多數Analog Devices處理器系列,是未來處理器(包括多核設備)的首選IDE。VisualDSP++支持在CrossCore Embedded Studio發布之前推出的處理器系列。

EZ - KIT Lite評估板

Analog Devices提供各種EZ - KIT Lite評估板,包括處理器和關鍵外設,支持片上仿真功能和其他評估和開發功能。

軟件插件

Analog Devices提供與CrossCore Embedded Studio無縫集成的軟件插件,包括評估硬件的板支持包、各種中間件包和算法模塊。

八、引腳功能描述

文檔詳細描述了ADSP - 21369處理器的引腳功能,包括外部地址、數據、內存選擇、寫使能、標志、中斷、JTAG等引腳的功能和狀態。

九、規格參數

工作條件

文檔提供了不同頻率下的電源電壓、輸入輸出電壓、結溫等工作條件參數。

電氣特性

包括高電平輸出電壓、低電平輸出電壓、高電平輸入電流、低電平輸入電流等電氣特性參數。

最大功耗

可參考“Estimating Power Dissipation for ADSP - 21368 SHARC Processors”(EE - 299)獲取詳細的熱和功率信息。

絕對最大額定值

包括內部(核心)電源電壓、模擬(PLL)電源電壓、外部(I/O)電源電壓、輸入電壓、輸出電壓擺幅、負載電容、存儲溫度范圍和偏置下的結溫等絕對最大額定值。

時序規格

詳細描述了核心時鐘要求、電源上電時序、時鐘輸入、復位、中斷、定時器、SDRAM接口、內存讀寫等的時序規格。

輸出驅動電流

文檔提供了輸出驅動的典型I - V特性曲線。

測試條件

AC信號規格(時序參數)基于特定的電壓參考電平,輸出延遲和保持基于標準電容負載。

電容負載

輸出延遲和保持與負載電容的關系通過圖形展示。

熱特性

提供了256球BGA_ED和208引腳LQFP_EP封裝的熱特性參數,可用于確定設備的結溫。

引腳排列

詳細列出了256球BGA_ED和208引腳LQFP_EP封裝的引腳名稱和默認功能。

封裝尺寸

給出了256球BGA_ED和208引腳LQFP_EP封裝的尺寸信息。

表面貼裝設計

提供了BGA_ED數據,用于表面貼裝設計參考。

訂購指南

列出了不同型號的ADSP - 21369處理器的溫度范圍、指令速率、片上SRAM、ROM、封裝描述和封裝選項等信息。

ADSP - 21369 SHARC處理器憑借其強大的性能、豐富的外設和完善的開發工具,為電子工程師在音頻處理等領域的設計提供了一個優秀的選擇。在實際應用中,我們需要根據具體需求合理配置和使用該處理器,以充分發揮其優勢。大家在使用過程中有沒有遇到什么特別的問題或者有什么獨特的應用經驗呢?歡迎在評論區分享交流。

-

SHARC處理器

+關注

關注

0文章

57瀏覽量

7862 -

音頻處理

+關注

關注

0文章

177瀏覽量

18315

發布評論請先 登錄

剖析ADSP - BF512/BF514/BF516/BF518:高性能嵌入式處理器的卓越之選

ADSP-21593/21594/ADSP-SC592/SC594處理器:高性能與多功能的完美融合

ADSP-SC57x/ADSP-2157x處理器:高性能數字信號處理的理想之選

高性能音頻處理利器:ADSP - 21477/ADSP - 21478/ADSP - 21479處理器深度解析

ADSP - 21467/ADSP - 21469 SHARC處理器:高性能音頻處理的理想之選

探索ADSP - 21371/ADSP - 21375 SHARC處理器:高性能音頻處理的利器

深度解析ADSP-2126x:高性能音頻處理的理想之選

Analog Devices Inc. ADSP1802 SHARC?處理器數據手冊

ADSP-21371/ADSP-21375面向汽車音頻的32位高性能浮點SHARC處理器技術手冊

ADSP - 21369 SHARC處理器:高性能音頻處理的理想之選

ADSP - 21369 SHARC處理器:高性能音頻處理的理想之選

評論