ADSP - 21467/ADSP - 21469 SHARC處理器:高性能音頻處理的理想之選

引言

在當今的電子領域,高性能音頻處理需求日益增長。ADSP - 21467/ADSP - 21469 SHARC處理器憑借其卓越的性能和豐富的功能,成為了眾多工程師在音頻處理項目中的首選。本文將深入介紹這款處理器的特點、架構、性能以及相關設計要點,希望能為電子工程師們在實際應用中提供有價值的參考。

文件下載:ADSP-21469.pdf

處理器概述

ADSP - 21467/ADSP - 21469是SIMD SHARC系列DSP的成員,采用了ADI的超級哈佛架構。它與ADSP - 2126x、ADSP - 2136x等多種DSP在源代碼上兼容,并且在SISD模式下與第一代ADSP - 2106x SHARC處理器也具有兼容性。這款32位/40位浮點處理器專為高性能音頻應用而優化,擁有5 Mbits的片上SRAM、多個內部總線以消除I/O瓶頸,以及創新的數字應用/外設接口(DAI/DPI)。

性能基準

| 表1展示了處理器在不同算法下的性能表現: | Benchmark Algorithm | Speed (at 450 MHz) |

|---|---|---|

| 1024 Point Complex FFT (Radix 4, with Reversal) | 20.44 μs | |

| FIR Filter (Per Tap) | 1.11 ns | |

| IIR Filter (Per Biquad) | 4.43 ns | |

| Matrix Multiply (Pipelined) [3 × 3] × [3 × 1] | 10.0 ns | |

| Matrix Multiply (Pipelined) [4 × 4] × [4 × 1] | 17.78 ns | |

| Divide (y/x) | 6.67 ns | |

| Inverse Square Root | 10.0 ns |

從這些數據可以看出,該處理器在音頻處理相關的算法中表現出色,能夠滿足高性能音頻處理的需求。

產品特性

| 表2詳細列出了ADSP - 21467和ADSP - 21469的特性: | Feature | ADSP - 21467 | ADSP - 21469 |

|---|---|---|---|

| Maximum Frequency | 450 MHz | ||

| RAM | 5 Mbits | ||

| ROM | 4 Mbits | N/A | |

| Audio Decoders in ROM | Yes | No | |

| DTCP Hardware Accelerator | No | ||

| Pulse - Width Modulation | Yes | ||

| S/PDIF | Yes | ||

| DDR2 Memory Interface | Yes | ||

| DDR2 Memory Bus Width | 16 Bits | ||

| Shared DDR2 External Memory | Yes | ||

| Direct DMA from SPORTs to External Memory | Yes | ||

| FIR, IIR, FFT Accelerator | Yes | ||

| MLB Interface | Automotive Models Only | ||

| IDP | Yes | ||

| Serial Ports | 8 | ||

| DAI (SRU)/DPI (SRU2) | 20/14 pins | ||

| UART | 1 | ||

| Link Ports | 2 | ||

| AMI Interface with 8 - Bit Support | Yes |

這些特性使得處理器在音頻處理、醫療成像、通信等多個領域都有廣泛的應用前景。

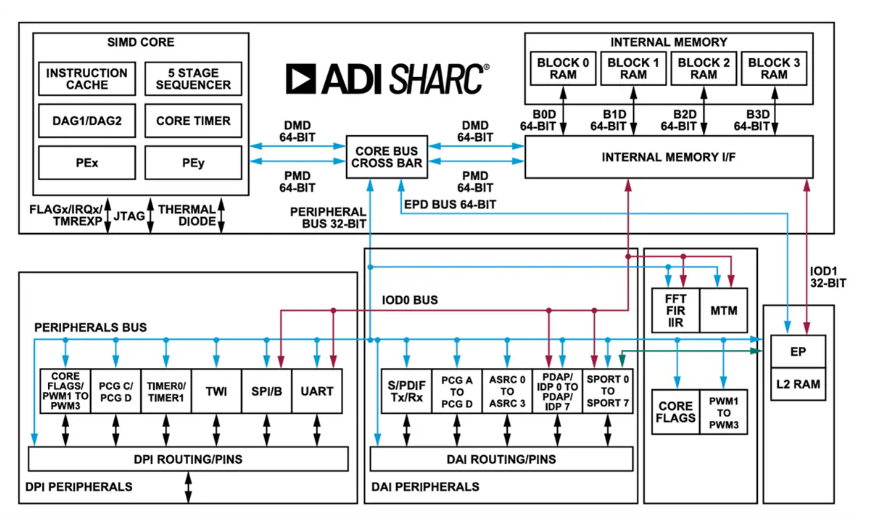

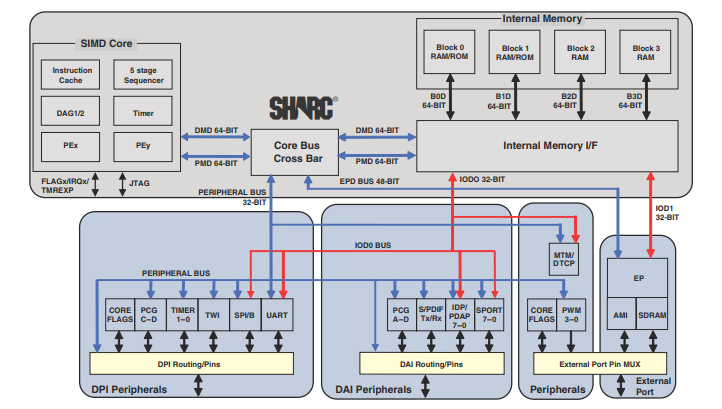

核心架構

SIMD計算引擎

處理器包含兩個計算處理單元,作為單指令多數據(SIMD)引擎運行。PEX始終處于活動狀態,PEY可通過設置MODE1寄存器中的PEYEN模式位來啟用。在SIMD模式下,兩個處理單元執行相同的指令,但處理不同的數據,這種架構在執行數學密集型DSP算法時非常高效。同時,進入SIMD模式會使內存與處理單元之間的數據帶寬翻倍,以滿足計算需求。

獨立并行計算單元

每個處理單元內都有一組計算單元,包括算術邏輯單元(ALU)、乘法器和移位器。這些單元在單個周期內完成所有操作,并且三個單元并行排列,最大限度地提高了計算吞吐量。在SIMD模式下,并行的ALU和乘法器操作會在兩個處理單元中同時發生。這些計算單元支持IEEE 32位單精度浮點、40位擴展精度浮點和32位定點數據格式。

定時器

核心定時器可以生成周期性軟件中斷,并且可以配置為使用FLAG3作為定時器過期信號。

數據寄存器文件

每個處理單元都包含一個通用數據寄存器文件,用于在計算單元和數據總線之間傳輸數據,并存儲中間結果。這些10端口、32寄存器(16個主寄存器,16個輔助寄存器)的寄存器文件與處理器的增強哈佛架構相結合,允許計算單元和內部內存之間無限制的數據流動。

上下文切換

處理器的許多寄存器都有輔助寄存器,可在中斷服務期間激活,以實現快速上下文切換。數據寄存器、DAG寄存器和乘法器結果寄存器都有輔助寄存器。主寄存器在復位時處于活動狀態,輔助寄存器通過模式控制寄存器中的控制位激活。

通用寄存器

通用寄存器可用于通用任務。USTAT(4)寄存器允許對核心的所有系統寄存器(控制/狀態)進行簡單的位操作(設置、清除、切換、測試、異或)。數據總線交換寄存器(PX)允許在64位PM數據總線和64位DM數據總線之間,或在40位寄存器文件和PM/DM數據總線之間傳遞數據。

單周期取指令和四個操作數

處理器采用增強的哈佛架構,數據內存(DM)總線傳輸數據,程序內存(PM)總線傳輸指令和數據。通過獨立的程序和數據內存總線以及片上指令緩存,處理器可以在單個周期內同時獲取四個操作數(每個數據總線兩個)和一條指令(從緩存中)。

指令緩存

片上指令緩存支持三總線操作,用于獲取一條指令和四個數據值。緩存僅對與PM總線數據訪問沖突的指令進行緩存,這允許核心循環操作(如數字濾波器乘法累加和FFT蝶形處理)以全速執行。

數據地址生成器

兩個數據地址生成器(DAGs)用于間接尋址和在硬件中實現循環數據緩沖區。循環緩沖區允許高效編程延遲線和數字信號處理中所需的其他數據結構,常用于數字濾波器和傅里葉變換。處理器的兩個DAGs包含足夠的寄存器,可創建多達32個循環緩沖區(16個主寄存器集,16個輔助寄存器集)。DAGs自動處理地址指針回繞,減少開銷,提高性能,并簡化實現。

靈活的指令集

48位指令字可容納各種并行操作,便于簡潔編程。例如,處理器可以在兩個處理單元中有條件地執行乘法、加法和減法,同時進行分支并從內存中獲取多達四個32位值,所有這些都在一條指令中完成。

可變指令集架構(VISA)

除了支持以前SHARC處理器的標準48位指令外,處理器還支持16位和32位的新指令。這種可變指令集架構(VISA)通過去除48位指令中的冗余/未使用位,創建更高效和緊湊的代碼。程序序列器支持從內部和外部DDR2內存中獲取這些16位和32位指令。

片上內存

處理器包含5 Mbits的內部RAM,每個塊可以配置為不同的代碼和數據存儲組合。內存架構與獨立的片上總線相結合,允許在單個周期內從核心進行兩次數據傳輸和從I/O處理器進行一次數據傳輸。內存可以配置為32位數據的最大160k字、16位數據的320k字、48位指令(或40位數據)的106.7k字,或不同字大小的組合,最多5 Mbits。

外設架構

外部端口

外部端口接口支持通過核心和DMA訪問外部內存。外部內存地址空間分為四個銀行,任何銀行都可以編程為異步或同步內存。外部端口由異步內存接口、DDR2 DRAM控制器和仲裁邏輯組成。異步內存接口支持與SRAM、Flash等設備通信,DDR2 DRAM控制器支持高達2 Gbits的外部內存設備。

外部內存

處理器的外部端口提供了與各種行業標準內存設備的高性能、無膠水接口。通過獨立的內部DDR2內存控制器,可連接同步和/或異步內存設備。16位DDR2 DRAM控制器連接到行業標準同步DRAM設備,8位異步內存控制器用于連接各種內存設備。四個內存選擇引腳允許最多四個獨立設備共存,支持同步和異步設備類型的任意組合。

SIMD訪問外部內存

DDR2控制器支持在64位EPD(外部端口數據總線)上進行SIMD訪問,這允許在正常字空間(NW)中訪問PEy單元上的互補寄存器,提高了性能。

VISA和ISA訪問外部內存

DDR2控制器還支持VISA代碼操作,減少了內存負載,因為VISA指令被壓縮。此外,總線獲取減少,在最佳情況下,一次48位獲取包含三條有效指令。傳統ISA操作的代碼執行也得到支持。

共享外部內存

處理器支持與其他ADSP - 2146x處理器連接到公共共享外部DDR2內存,以創建共享外部總線處理器系統。這包括分布式片上仲裁、固定和旋轉優先級總線仲裁、總線超時邏輯和總線鎖定。

DDR2支持

處理器支持16位DDR2接口,最大頻率為核心時鐘的一半。支持從外部內存執行,支持高達2 Gbits的外部內存設備。

異步內存控制器

異步內存控制器為多達四個獨立的內存或I/O設備銀行提供可配置接口。每個銀行可以獨立編程不同的定時參數,允許連接到各種內存設備,包括SRAM、Flash和EPROM,以及與標準內存控制線接口的I/O設備。

外部端口吞吐量

基于400 MHz時鐘,外部端口的吞吐量為AMI 66M字節/秒,DDR2 800M字節/秒。

鏈接端口

兩個8位寬的鏈接端口可以連接到其他DSP或外設的鏈接端口。鏈接端口是雙向端口,具有八條數據線、一條確認線和一條時鐘線,最大頻率為166 MHz。

媒體本地總線(MediaLB)

汽車模型具有MLB接口,允許處理器作為媒體本地總線設備運行。它支持3引腳和5引腳媒體本地總線協議,支持高達1024 FS(49.25M位/秒,FS = 48.1 kHz)的速度和多達31個邏輯通道,每個媒體本地總線幀最多124字節的數據。

脈沖寬度調制(PWM)

PWM模塊是一個靈活的、可編程的PWM波形發生器,可用于生成各種與電機和發動機控制或音頻功率控制相關的應用所需的開關模式。PWM發生器可以生成中心對齊或邊緣對齊的PWM波形,并且可以在配對模式下生成兩個輸出的互補信號,或在非配對模式下生成獨立信號。

數字應用接口(DAI)

數字應用接口(DAI)允許將各種外設連接到任何DAI引腳(DAI_P20 - 1)。程序使用信號路由單元(SRU)進行這些連接,SRU是一個矩陣路由單元(或多路復用器組),允許在軟件控制下互連DAI提供的外設。DAI包括串行端口、S/PDIF兼容數字音頻接收器/發射器、異步采樣率轉換器、輸入數據端口和精密時鐘發生器等外設。

數字外設接口(DPI)

數字外設接口提供與兩個串行外設接口(SPI)端口、一個通用異步接收器 - 發射器(UART)、12個標志、一個2線接口(TWI)和兩個通用定時器的連接。

I/O處理器特性

汽車版本的I/O處理器提供67個DMA通道,標準版本提供36個DMA通道,以及一系列廣泛的外設,包括DMA控制器、IIR加速器、FFT加速器和FIR加速器等。

系統設計

程序引導

內部內存在系統上電時通過外部端口、鏈接端口、SPI主設備或SPI從設備從8位EPROM引導。引導模式由BOOTCFG2 - 0引腳確定。

電源供應

處理器有獨立的內部((V{DD_INT}))、外部((V{DD_EXT}))和模擬((V{DD_A}))電源供應連接。內部和模擬電源必須滿足(V{DD_INT})規格,外部電源必須滿足(V{DD_EXT})規格。建議在PCB設計中為(V{DD_A})引腳使用外部濾波電路,以產生穩定的時鐘。

目標板JTAG仿真器連接器

ADI的JTAG仿真器使用處理器的IEEE 1149.1 JTAG測試訪問端口來監控和控制目標板處理器。仿真器可以在全處理器速度下進行仿真,允許檢查和修改內存、寄存器和處理器堆棧。

開發工具

ADI為其處理器提供了完整的軟件和硬件開發工具,包括集成開發環境(CrossCore? Embedded Studio和VisualDSP++?)、評估產品、仿真器和各種軟件插件。

集成開發環境(IDEs)

CrossCore Embedded Studio基于EclipseTM框架,支持大多數ADI處理器系列,是未來處理器(包括多核設備)的首選IDE。VisualDSP++支持在CrossCore Embedded Studio發布之前推出的處理器系列,包括ADI VDK實時操作系統和開源TCP/IP堆棧。

EZ - KIT Lite評估板

ADI提供各種EZ - KIT Lite評估板,包括處理器和關鍵外設,支持片上仿真功能和其他評估和開發功能。還有各種EZ - Extenders子卡,提供額外的專業功能,包括音頻和視頻處理。

軟件插件

ADI提供與CrossCore Embedded Studio無縫集成的軟件插件,以擴展其功能并減少開發時間。插件包括評估硬件的板支持包、各種中間件包和算法模塊。

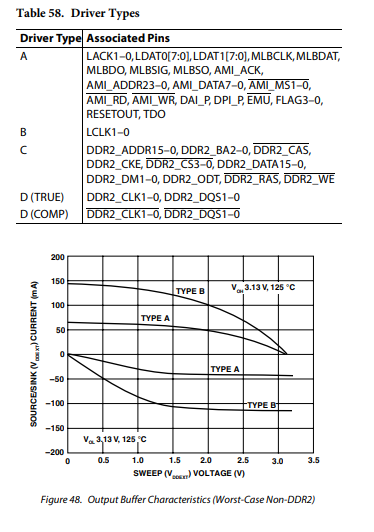

引腳功能描述

文檔詳細介紹了處理器的引腳功能和未使用引腳的端接規則。不同引腳在復位期間和之后有不同的狀態和功能,例如AMI_ADDR、AMI_DATA、FLAG等引腳在不同模式下有不同的用途。

規格參數

工作條件

處理器在不同頻率下有不同的電源電壓要求,如內部(核心)電源電壓(V{DD_INT})、外部(I/O)電源電壓(V{DD_EXT})、模擬電源電壓(V_{DD_A})等。同時,對不同引腳的輸入輸出電壓、結溫等也有相應的規格要求。

電氣特性

包括高電平輸出電壓、低電平輸出電壓、輸入電流、三態泄漏電流等參數,這些參數對于電路設計和性能評估非常重要。

總功耗

總功耗由內部功耗和外部功耗組成。內部功耗包括靜態電流和動態電流,靜態電流與結溫和核心電壓有關,動態電流與處理器的活動水平有關,通過活動縮放因子(ASF)來反映。

時序規格

文檔詳細給出了處理器的各種時序規格,包括核心時鐘要求、電源上電時序、時鐘輸入、中斷、定時器PWM_OUT周期時序、引腳到引腳直接路由、精密時鐘發生器、標志、DDR2 SDRAM讀寫周期時序、AMI讀寫、共享內存總線請求、鏈接端口、串行端口、并行數據采集端口、采樣率轉換器、S/PDIF發射器和接收器、SPI接口、媒體本地總線、UART端口和TWI等方面的時序要求。這些時序規格對于確保處理器與其他設備的兼容性和正常工作至關重要。

總結

ADSP - 21467/ADSP - 21469 SHARC處理器以其高性能的計算能力、豐富的外設接口和靈活的架構,為電子工程師在音頻處理、醫療成像、通信等多個領域的設計提供了強大的支持。在實際應用中,工程師需要根據具體需求合理選擇處理器型號,同時注意電源供應、時序要求等設計要點,以充分發揮處理器的性能。希望本文能幫助工程師更好地了解和應用這款處理器,為項目的成功實施提供助力。

你在使用這款處理器的過程中遇到過哪些挑戰呢?又有哪些獨特的應用經驗可以分享?歡迎在評論區留言討論。

-

SHARC處理器

+關注

關注

0文章

57瀏覽量

7862 -

音頻處理

+關注

關注

0文章

177瀏覽量

18315

發布評論請先 登錄

ADSP-BF60x 系列處理器:高性能與多功能的完美融合

ADSP-21593/21594/ADSP-SC592/SC594處理器:高性能與多功能的完美融合

ADSP-SC57x/ADSP-2157x處理器:高性能數字信號處理的理想之選

高性能音頻處理利器:ADSP - 21477/ADSP - 21478/ADSP - 21479處理器深度解析

ADSP-21560/21561/21564/21568:高性能SHARC+單核心DSP的深度剖析

探索ADSP - 21371/ADSP - 21375 SHARC處理器:高性能音頻處理的利器

深度解析ADSP-2126x:高性能音頻處理的理想之選

Analog Devices Inc. ADSP1802 SHARC?處理器數據手冊

ADSP-21371/ADSP-21375面向汽車音頻的32位高性能浮點SHARC處理器技術手冊

ADSP - 21467/ADSP - 21469 SHARC處理器:高性能音頻處理的理想之選

ADSP - 21467/ADSP - 21469 SHARC處理器:高性能音頻處理的理想之選

評論