ADN2855:多速率突發模式時鐘與數據恢復IC的技術剖析

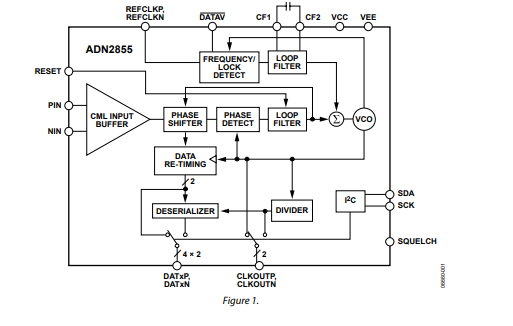

在光通信領域,GPON/BPON/GEPON光線路終端(OLT)接收器對時鐘和數據恢復有著嚴格要求。ADN2855作為一款專門為該應用設計的突發模式時鐘和數據恢復IC,展現出了卓越的性能和豐富的功能。下面,我們將深入剖析ADN2855的各項特性。

文件下載:ADN2855.pdf

一、核心特性

1. 數據速率與接口

ADN2855支持155.52 Mbps、622.08 Mbps、1244.16 Mbps和1250.00 Mbps四種串行數據輸入速率,可通過I2C接口進行靈活選擇。其具備12位的采集時間,擁有4位并行LVDS輸出接口,能高效地處理和傳輸數據。

2. 獨特架構與功能

- 雙環時鐘恢復架構:專利的雙環時鐘恢復架構確保了時鐘恢復的穩定性和準確性,能有效應對不同速率的數據。

- 集成PRBS發生器:集成的PRBS發生器為測試和驗證提供了便利,有助于工程師快速檢測系統性能。

- 字節速率參考時鐘:字節速率參考時鐘為系統提供了穩定的時鐘基準,保證數據處理的同步性。

- 失鎖指示器:失鎖指示器能及時反饋時鐘恢復狀態,方便工程師進行故障排查。

3. 兼容性與接口

- 支持DDR - FPGA:支持雙數據速率(DDR)兼容的FPGA,可與多種數字電路無縫對接。

- I2C接口:通過I2C接口,工程師可以方便地訪問設備的可選功能,實現對設備的靈活配置。

4. 電源與封裝

- 單電源供電:采用3.3 V單電源供電,簡化了電源設計,降低了系統成本。

- 低功耗:在串行輸出模式下典型功耗為670 mW,在解串器模式下典型功耗為825 mW,具有良好的節能性能。

- 緊湊封裝:采用5 mm × 5 mm、32引腳的LFCSP封裝,節省了電路板空間,適合小型化設計。

二、工作原理

1. 頻率鎖定

ADN2855需要一個與輸入數據頻率鎖定的參考時鐘。其FLL(頻率鎖定環)會相對于該參考時鐘進行頻率鎖定,將VCO(壓控振蕩器)的頻率誤差拉向0 ppm。由于假定OLT的上游突發數據由光網絡終端(ONT)CDR恢復的時鐘進行時鐘同步,因此能保證與OLT系統時鐘的頻率鎖定。

2. 相位鎖定

芯片內部的前導碼檢測器會在前導碼中尋找最大轉換密度模式(如1010…)。一旦檢測到該模式,片上延遲/鎖相環(D/PLL)會在12 UI(單位間隔)內快速對輸入突發數據進行相位鎖定,并補償FLL未完全消除的頻率誤差。

3. 數據處理

輸入數據由恢復的時鐘進行重定時,然后以串行或4位并行輸出半字節的形式輸出。同時,在突發數據之間,需要一個RESET信號將設備設置為快速相位采集模式。RESET信號必須在之前突發數據結束后的8 UI內有效,并在最大轉換密度前導碼部分開始之前無效,且寬度至少為16 UI。

三、功能描述

1. 頻率采集

ADN2855工作在突發數據恢復模式,需要使用OLT系統參考時鐘作為采集輔助。通過設置(CTRL A[0]=1)將其置于鎖定參考時鐘模式,然后向CTRLB[5]寫入1到0的轉換來啟動頻率采集。該頻率采集在正常工作模式下只需進行一次,初始頻率采集大約需要10 ms。

2. DATAV操作

ADN2855的數據有效指示器(DATAV)在獲取前導碼最大轉換密度部分的相位時有效,從1010…模式開始需要12 UI。DATAV輸出在當前突發數據結束后RESET信號有效時無效,其輸出為低電平有效,且與LVTTL兼容。

3. 靜噪模式

當靜噪輸入(引腳30)驅動為TTL高電平時,時鐘和數據輸出都被設置為零狀態,以抑制下游處理。若不需要靜噪功能,引腳30應連接到VEE。若希望在輸出數據無效時對DATxP/DATxN和CLKOUTP/CLKOUTN輸出進行靜噪,則可將DATAV引腳直接硬連接到靜噪輸入。

4. I2C接口

ADN2855支持2線、I2C兼容的串行總線,可驅動多個外設。它有四個可能的7位從地址,用于讀寫操作。通過I2C接口,主設備可以與ADN2855進行數據傳輸,包括寫入控制寄存器和讀取狀態信息。

5. 參考時鐘

參考時鐘對于ADN2855的突發模式時鐘和數據恢復至關重要,必須與輸入突發數據頻率鎖定。參考時鐘可以是差分驅動或單端驅動,輸入緩沖器可接受峰 - 峰差分幅度大于100 mV的差分信號或標準單端低電壓TTL輸入。通過設置I2C控制寄存器CTRLA的第0位為1,可啟用鎖定參考時鐘模式,并通過向CTRLB[5]寫入1到0的轉換來啟動頻率采集。

6. 輸出模式

- 并行或串行輸出模式:輸出可以配置為4位并行輸出半字節模式或串行輸出模式。默認情況下,接收數據被解串并以4位半字節形式輸出,通過設置CTRLC[5] = 1可反轉DATxP/DATxN總線順序;設置CTRLD[7] = 1則進入串行輸出模式。

- 雙數據速率模式:默認輸出模式為4位解串輸出和全速率輸出時鐘。在并行輸出模式下,設置(CTRLC[4]=1)可將時鐘輸出進行二分頻,以支持上升和下降沿數據時鐘的FPGA;在串行輸出模式下,設置CTRLD[0] = 1可將串行時鐘輸出設置為全速率模式。

- RxCLK相位調整:ADN2855提供了調整輸出時鐘相對于并行輸出數據相位的選項,通過CTRLC[3:2]可選擇+2 UI、+0.5 UI和 - 1.5 UI三種額外的相位調整選項。

7. 禁用輸出緩沖器

為了節省功耗,可通過設置(CTRLD[5]=1)禁用時鐘輸出緩沖器,設置(CTRLD[6]=1)禁用數據輸出緩沖器。

四、應用信息

1. PCB設計指南

- 電源和接地:建議使用一個低阻抗接地平面,VEE引腳應直接焊接到接地平面以減少串聯電感。在3.3 V電源進入PCB的位置,建議使用10 μF電解電容進行濾波,并在IC電源VCC和VEE之間靠近ADN2855 VCC引腳處放置0.1 μF和1 nF陶瓷芯片電容。

- 傳輸線:所有高頻輸入和輸出信號都應使用50 Ω傳輸線,以最小化反射。PIN/NIN輸入跡線和CLKOUTP/CLKOUTN、DATxP/DATxN輸出跡線應進行長度匹配,以避免差分跡線之間的偏移。所有高速LVDS輸出都需要在被驅動設備的差分輸入處進行100 Ω差分端接。

- 焊接指南:32引腳LFCSP的焊盤應為矩形,PCB焊盤應比封裝焊盤長0.1 mm、寬0.05 mm,并確保焊盤居中。芯片底部的中央暴露焊盤應至少與PCB上的焊盤一樣大,并使用塞孔連接到VEE(GND),以防止回流焊時焊料泄漏。

2. 外形尺寸與訂購信息

ADN2855采用5 mm × 5 mm、32引腳的LFCSP封裝,提供了特定的外形尺寸規格。訂購時,可根據溫度范圍和封裝選項選擇不同的型號,如ADN2855ACPZ和ADN2855ACPZ - R7適用于 - 40°C至 + 85°C溫度范圍,ADN2855 - EVALZ為評估板。

ADN2855憑借其豐富的功能和出色的性能,為GPON/BPON/GEPON OLT接收器應用提供了可靠的解決方案。在實際設計中,工程師需要根據具體需求合理配置設備參數,并遵循PCB設計指南,以確保系統的穩定運行。你在使用ADN2855或其他類似IC時,遇到過哪些挑戰呢?歡迎在評論區分享你的經驗。

-

光通信

+關注

關注

20文章

1015瀏覽量

35416

發布評論請先 登錄

探索ADN2816:高性能時鐘和數據恢復IC的深度剖析

622 Mbps時鐘和數據恢復IC——ADN2806的技術解析與應用指南

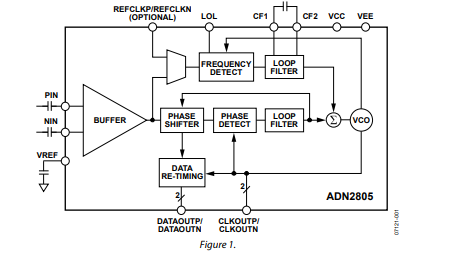

1.25 Gbps時鐘和數據恢復IC ADN2805:特性、原理與應用全解析

解析ADN2804:622 Mbps時鐘和數據恢復IC的卓越性能與應用指南

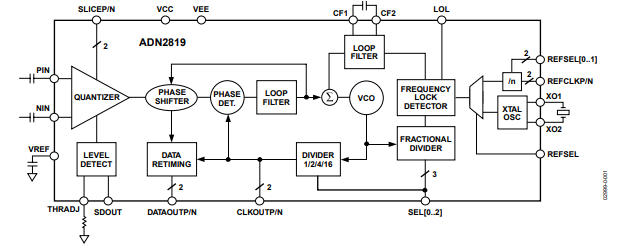

ADN2819多速率限幅放大器與時鐘和數據恢復IC技術手冊

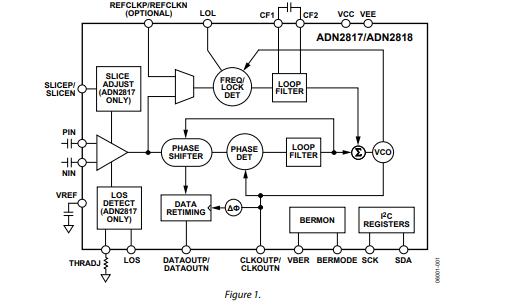

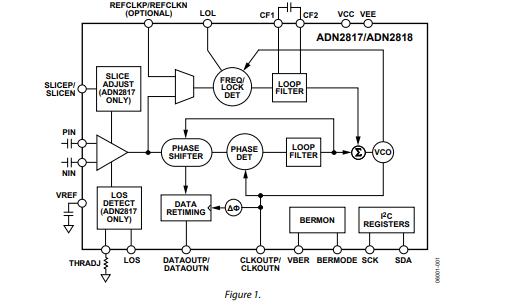

ADN2818連續速率10 Mbps至2.7 Gbps時鐘和數據恢復IC技術手冊

ADN2817連續速率10 Mbps至2.7 Gbps時鐘和數據恢復IC技術手冊

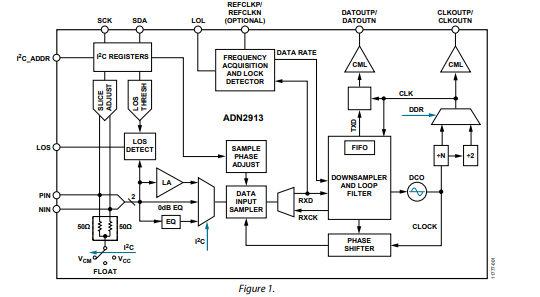

ADN2913連續速率6.5 Mbps至8.5 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器技術手冊

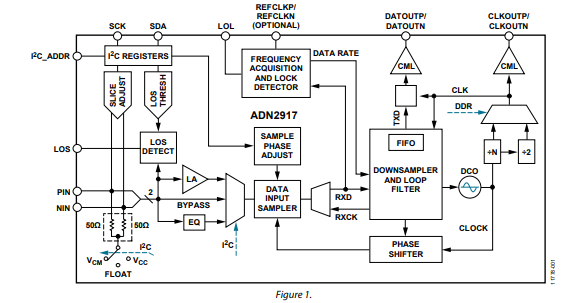

ADN2917連續速率8.5 Gbps至11.3 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器技術手冊

ADN2855:多速率突發模式時鐘與數據恢復IC的技術剖析

ADN2855:多速率突發模式時鐘與數據恢復IC的技術剖析

評論