ADN2807:155/622 Mb/s時鐘和數據恢復IC的技術剖析與應用指南

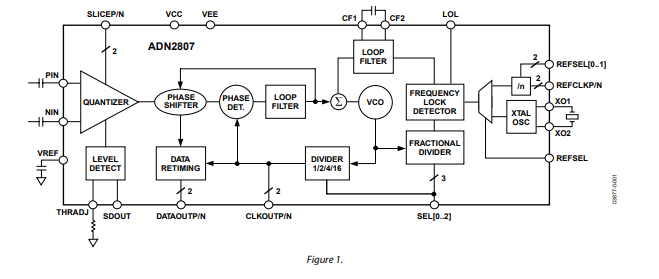

在高速數據傳輸領域,時鐘和數據恢復(CDR)技術對于確保信號的準確傳輸和處理至關重要。今天,我們就來深入探討Analog Devices公司的ADN2807芯片,它是一款集成了限幅放大器的155/622 Mb/s時鐘和數據恢復IC,在SONET和WDM等系統中有著廣泛的應用。

文件下載:ADN2807.pdf

芯片特性概覽

滿足SONET標準

ADN2807完全符合SONET對于抖動傳輸、生成和容限的要求。在-40°C至+85°C的環境溫度下,它能穩定工作,確保在OC - 3、OC - 12和15/14 FEC速率下實現量化、信號電平檢測以及時鐘和數據恢復功能。

高靈敏度與可調性

量化器靈敏度典型值為4 mV,可調切片電平范圍為±100 mV,能夠有效應對不同的信號環境。同時,其專利的時鐘恢復架構保證了時鐘恢復的準確性和穩定性。

信號檢測與參考時鐘

信號丟失檢測范圍為3 mV至15 mV,可及時發現信號異常。該芯片支持多種參考時鐘頻率,如19.44 MHz、38.88 MHz、77.76 MHz或155.52 MHz,并且REFCLK輸入兼容LVPECL/LVDS/LVCMOS/LVTTL(僅在155.52 MHz時支持LVPECL/LVDS),還提供可選的19.44 MHz片上振蕩器,可與外部晶體配合使用。

低功耗與小封裝

采用單電源3.3 V供電,典型功耗僅為540 mW,具有出色的節能性能。其7 mm × 7 mm、48引腳的LFCSP封裝,體積小巧,適合高密度的電路板設計。

技術規格詳解

量化器特性

- 直流特性:輸入電壓范圍為0 - 1.2 V,峰 - 峰差分輸入為2.4 V,輸入共模電平為0.4 V,差分輸入靈敏度典型值為4 mV p - p,輸入過驅動為2 - 5 mV p - p,輸入偏移為500 μV,輸入均方根噪聲在BER = 1 × 10–10時為244 μV rms。

- 交流特性:小信號增益為54 dB,輸入電阻為100 Ω,輸入電容為0.65 pF,脈沖寬度失真為10 ps。

信號檢測與鎖定

- 電平信號檢測:不同的RTHRESH電阻值對應不同的電平檢測范圍和響應時間,并且具有一定的磁滯特性,可防止輸出抖動。

- 失鎖檢測:失鎖響應時間在fVCO誤差 > 1000 ppm時為60 mV。

鎖相環特性

- 抖動傳輸:OC - 12的抖動傳輸帶寬為140 - 200 kHz,OC - 3為48 - 85 kHz。

- 抖動生成:在特定頻率范圍內,OC - 12的抖動生成典型值為0.003 UI rms,OC - 3為0.02 - 0.04 UI p - p。

- 抖動容限:在不同頻率下,OC - 12和OC - 3都有相應的抖動容限要求,ADN2807能夠滿足這些要求。

輸出特性

CML輸出的單端輸出擺幅為400 - 540 mV,差分輸出擺幅為850 - 1100 mV,輸出高電壓和低電壓分別為VCC - 0.60 V和VCC - 0.30 V,上升時間和下降時間均為150 ps,不同速率下的建立時間和保持時間也有明確規定。

功能模塊解析

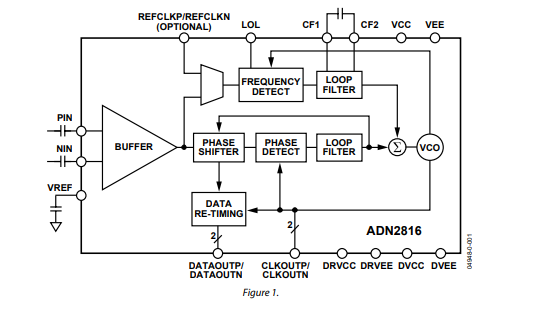

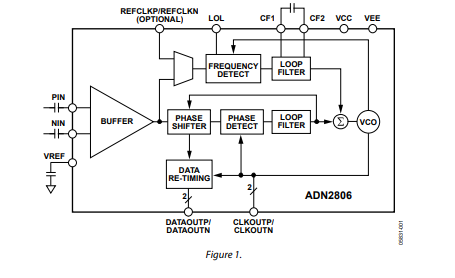

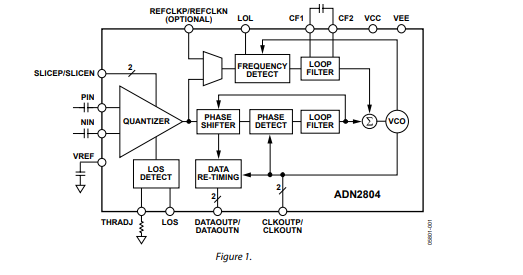

多速率時鐘和數據恢復

ADN2807能夠從OC - 3、OC - 12以及15/14 FEC速率的串行比特流中恢復時鐘和數據。通過SEL[2..0]輸入選擇數據速率,輸出的2.5 GHz VCO經過分頻以支持較低的數據速率。

限幅放大器

限幅放大器具有差分輸入(PIN/NIN),內部以50 Ω端接到片上電壓參考(VREF = 0.6 V典型值)。輸入可采用交流耦合或直流耦合,輸入偏移經過工廠調整,典型靈敏度優于4 mV,且漂移極小。

切片調整

通過向SLICEP/N輸入±0.8 V的差分電壓,可將量化器切片電平偏移±100 mV,以減輕ASE噪聲的影響。若不需要調整切片電平,SLICEP/N必須連接到VCC。

信號丟失(LOS)檢測器

接收器前端的電平信號檢測電路可指示輸入信號電平何時低于用戶可調閾值。閾值通過THRADJ引腳連接到地的單個外部電阻設置。當輸入電平低于編程的LOS閾值時,SDOUT引腳將輸出邏輯1,表示信號丟失。

參考時鐘

ADN2807提供三種參考頻率選項:差分時鐘、單端時鐘或晶體振蕩器。REFCLKN/P輸入可接受多種參考時鐘頻率,通過REFSEL0/1引腳選擇合適的分頻比。此外,還提供片上振蕩器與外部晶體配合使用。

鎖定檢測器操作

鎖定檢測器監控VCO和參考時鐘之間的頻率差,當VCO頻率在中心頻率的500 ppm以內時,失鎖信號被置為無效。若頻率誤差超過0.1%,失鎖信號重新置為有效,控制返回頻率環以重新獲取并保持穩定的時鐘信號。

靜噪模式

當靜噪輸入驅動到TTL高電平時,時鐘和數據輸出均置為零狀態,以抑制下游處理。該引腳可直接由LOS檢測器輸出(SDOUT)驅動。

測試模式 - 旁路和環回

- 旁路模式:當旁路輸入驅動到TTL高電平時,量化器輸出直接連接到驅動數據輸出引腳的緩沖器,繞過時鐘恢復電路,有助于系統處理非標準比特率。

- 環回模式:將LOOPEN引腳驅動到TTL高電平可啟用環回模式,便于系統診斷測試。測試輸入(TDINP/N)具有內部50 Ω端接,不使用時可懸空。旁路和環回模式相互排斥,同一時間只能使用一種模式。

應用設計要點

PCB設計準則

- 電源連接和接地平面:建議使用一個低阻抗接地平面連接模擬和數字接地,VEE引腳直接焊接到接地平面以減少串聯電感。在3.3 V電源進入PCB的位置使用10 μF電解電容器,在IC電源VCC和GND之間靠近ADN2807 VCC引腳處使用0.1 μF和1 nF陶瓷芯片電容器。

- 傳輸線:所有高頻輸入和輸出信號(如PIN、NIN、CLKOUTP、CLKOUTN、DATAOUTP、DATAOUTN等)使用50 Ω傳輸線,以最小化反射。PIN/NIN輸入跡線和CLKOUTP/N、DATAOUTP/N跡線應長度匹配,所有高速CML輸出需要100 Ω背端接芯片電阻連接到VCC。

- 芯片級封裝焊接準則:48引腳LFCSP的引腳為矩形,印刷電路板焊盤應比封裝引腳長0.1 mm、寬0.05 mm,底部的中央暴露焊盤應連接到模擬VCC。

交流耦合電容器選擇

為確保ADN2807在OC - 3和OC - 12數據速率下正常工作,輸入(PIN、NIN)和輸出(DATAOUTP、DATAOUTN)的交流耦合電容器最小應為0.1 μF。

直流耦合應用

ADN2807的輸入也可采用直流耦合,適用于突發模式應用。但需注意不違反輸入范圍和共模電平要求,若TIA輸出電平不符合要求,需進行電平轉換和/或衰減。

輸入數據丟失時的LOL切換

當輸入數據流因光鏈路中斷或其他原因丟失時,只要有有效的參考時鐘,ADN2807的時鐘輸出將保持在VCO中心頻率的1000 ppm以內,LOL引腳將以幾千赫茲的速率切換。

ADN2807是一款功能強大、性能優異的時鐘和數據恢復IC,在高速數據傳輸系統中具有廣泛的應用前景。工程師們在設計時,需充分考慮其各項特性和應用要點,以確保系統的穩定運行。大家在實際應用中是否遇到過類似芯片的設計挑戰呢?歡迎在評論區分享你的經驗和見解。

-

高速數據傳輸

+關注

關注

0文章

272瀏覽量

7213

發布評論請先 登錄

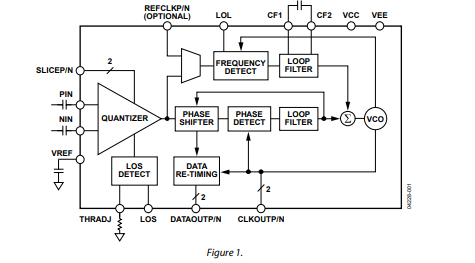

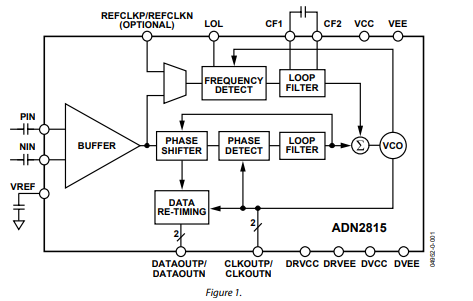

1.25 Gbps時鐘和數據恢復IC ADN2805:特性、原理與應用全解析

ADN2807 155/622 Mbps時鐘和數據恢復IC,集成限幅放大器技術手冊

ADN2812連續速率12.3 Mb/s至2.7 Gb/s時鐘和數據恢復IC,集成限幅放大器技術手冊

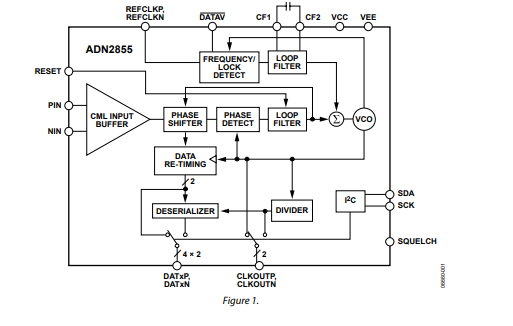

ADN2855多速率155 Mbps/622 Mbps/1244 Mbps/1250 Mbps突發模式時鐘和數據恢復IC技術手冊

ADN2807:155/622 Mb/s時鐘和數據恢復IC的技術剖析與應用指南

ADN2807:155/622 Mb/s時鐘和數據恢復IC的技術剖析與應用指南

評論