解析ADN4670:可編程低電壓1:10 LVDS時鐘驅動器

引言

在電子系統設計中,時鐘信號的精確分配至關重要。ADN4670作為一款可編程低電壓1:10 LVDS時鐘驅動器,為時鐘分配網絡提供了高效、可靠的解決方案。本文將深入解析ADN4670的特性、工作原理、技術參數以及應用場景,幫助電子工程師更好地了解和使用這款產品。

文件下載:ADN4670.pdf

產品特性與優勢

1. 低輸出偏斜

ADN4670具有典型值小于30ps的低輸出偏斜,能夠確保時鐘信號在傳輸過程中的同步性,減少信號延遲差異對系統性能的影響。這對于對時鐘同步要求較高的應用,如高速數據通信、數據采集系統等尤為重要。

2. 靈活的可編程性

通過簡單的串行接口,該器件可以實現從兩個差分時鐘輸入(CLK0、CLK1)中選擇一個,并能單獨啟用或禁用10個差分時鐘輸出。這種靈活性使得工程師可以根據具體應用需求進行定制化配置,提高系統的適應性。

3. 高信號速率

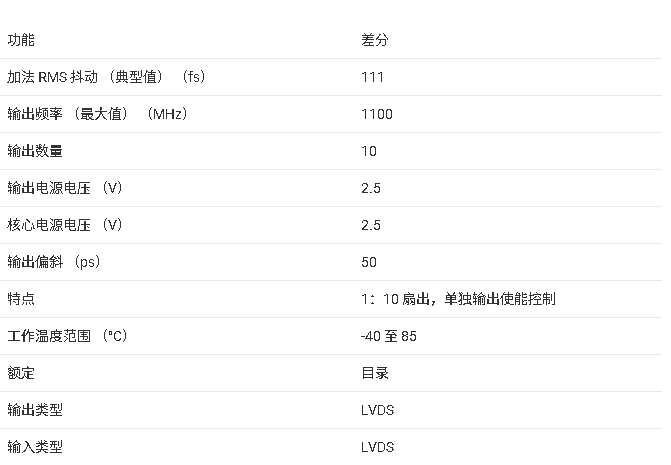

其典型的信號速率高達1.1 GHz,能夠滿足高速時鐘信號的傳輸需求,適用于高速數字電路和通信系統。

4. 寬電源電壓范圍

電源電壓范圍為2.375 V至2.625 V,這使得ADN4670在不同的電源環境下都能穩定工作,增強了其在各種應用場景中的兼容性。

5. 故障安全設計

在電源關閉((V_{DD}=0V))時,I/O引腳具有故障安全功能,確保在異常情況下系統的穩定性。

6. 多種封裝形式

提供32引腳的LFCSP和LQFP封裝,方便工程師根據不同的PCB布局和設計要求進行選擇。

7. 寬工作溫度范圍

工業級的工作溫度范圍為 -40°C至 +85°C,適用于各種惡劣的工業環境。

工作原理

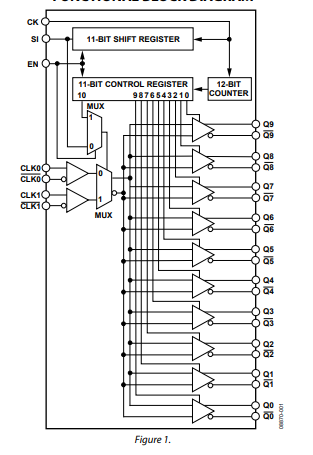

信號處理流程

ADN4670接收來自源(如雙絞線電纜)的差分電流信號,該信號在100 Ω終端電阻上產生典型值為±350 mV的電壓。信號通過差分多路復用器傳輸到10個驅動器,每個驅動器輸出差分電流信號,從而將一個差分時鐘輸入擴展為10個差分時鐘輸出。

可編程控制

通過三個控制輸入(EN、SI、CK)實現可編程功能。EN為使能輸入,高電平時允許編程;SI為串行數據輸入;CK為串行時鐘輸入,在時鐘從低到高的轉換時將數據時鐘輸入到器件中。

技術參數詳解

電氣特性

| 參數 | 符號 | 最小值 | 典型值 | 最大值 | 單位 | 條件/注釋 |

|---|---|---|---|---|---|---|

| 輸入高閾值 | (V_{TH}) | - | - | - | mV | - |

| 輸入低閾值 | (V_{TL}) | - | - | - | mV | - |

| 差分輸入電壓 | (V_{ID}) | -100 | - | +100 | mV | - |

| 輸入共模電壓 | (V_{IC}) | - | - | - | mV | - |

| 輸入電流 | (I{IH}, I{IL}) | - | - | - | μA | - |

| 輸入電容 | (C_{I}) | - | - | 3 | pF | - |

| 差分輸出電壓 | (V_{OD}) | 250 | 450 | 600 | mV | (R_{L}=100Ω), -40°C至 +85°C |

| 差分輸出電壓幅度變化 | (Delta V_{OD}) | - | - | 50 | mV | - |

| 偏移電壓 | (V_{OS}) | 0.95 | 1.2 | 1.45 | V | - |

| 偏移電壓幅度變化 | (Delta V_{OS}) | - | - | - | mV | - |

| 輸出短路電流 | (I_{OS}) | - | - | 350 | mA | - |

| 參考輸出電壓 | (V_{BB}) | - | - | - | V | - |

| 輸出電容 | (C_{O}) | - | - | - | pF | - |

| 電源電流 | (I_{DD}) | - | 100 | 150 | mA | 所有輸出三態,(f = 0Hz) |

| 電源電流 | (I_{DD}) | - | 110 | 160 | mA | 所有輸出啟用并加載,(R_{L}=100Ω),(f = 100MHz) |

| 電源電流 | (I_{DD}) | - | - | - | mA | 所有輸出啟用并加載,(R_{L}=100Ω),(f = 800MHz) |

抖動特性

| 參數 | 符號 | 最小值 | 典型值 | 最大值 | 單位 | 條件/注釋 |

|---|---|---|---|---|---|---|

| 從輸入到LVDS輸出(Q3和Q3)的附加相位抖動 | (t_{JITTER LVDS}) | - | 281 | - | (f_{S} rms) | 12 kHz至5 MHz,(f_{OUT}=30.72MHz) |

| 從輸入到LVDS輸出(Q3和Q3)的附加相位抖動 | (t_{JITTER LVDS}) | 111 | - | - | (f_{S} rms) | 12 kHz至20 MHz,(f_{OUT}=125MHz) |

LVDS開關特性

| 參數 | 符號 | 最小值 | 典型值 | 最大值 | 單位 | 條件/注釋 |

|---|---|---|---|---|---|---|

| 低到高傳播延遲 | (t_{PLHx}) | - | 2 | 3 | ns | 從CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

| 高到低傳播延遲 | (t_{PHLx}) | - | 2 | 3 | ns | 從CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

| 占空比 | (t_{DUTY}) | 45 | - | 55 | % | 從CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

| 輸出偏斜 | (t_{SK(O)}) | - | 30 | - | ps | 任何Qx/Qx |

| 脈沖偏斜 | (t_{SK(P)}) | - | - | 50 | ps | 任何Qx/Qx |

| 器件間輸出偏斜 | (t_{SK(PP)}) | - | - | 600 | ps | 任何Qx/Qx |

| 輸出上升時間 | (t_{r}) | - | - | 350 | ps | 任何Qx/Qx,20%至80%,(R{L}=100Ω),(C{L}=5pF) |

| 輸出下降時間 | (t_{f}) | - | - | 350 | ps | 任何Qx/Qx,80%至20%,(R{L}=100Ω),(C{L}=5pF) |

| 最大輸入頻率 | (f_{CLK}) | 900 | 1100 | - | MHz | 從CLK0/CLK0或CLK1/CLK1到任何Qx/Qx |

編程邏輯交流特性

| 參數 | 符號 | 最小值 | 典型值 | 最大值 | 條件/注釋 |

|---|---|---|---|---|---|

| CK輸入的最大頻率 | (f_{MAX}) | 100 | 150 | - | - |

| SI到CK的建立時間 | (t_{SU}) | - | - | 2 | SI在CK從0到1轉換前必須保持不變的時間 |

| CK到SI的保持時間 | (t_{H}) | - | - | 1.5 | SI在CK從0到1轉換后必須保持不變的時間 |

| EN到CK的移除時間 | (t_{REMOVAL}) | - | - | 1.5 | EN到CK的移除時間 |

| 啟動時間 | (t_{STARTUP}) | - | - | 1 | 通過SI禁用后啟動時間 |

| 最小時鐘脈沖寬度 | (t_{W}) | 3 | - | - | - |

| 邏輯輸入高電平 | (V_{IH}) | 2 | - | - | (V_{DD}=2.5V) |

| 邏輯輸入低電平 | (V_{IL}) | - | - | 0.8 | (V_{DD}=2.5V) |

| 高電平邏輯輸入電流(CK) | (I_{IH}) | -5 | - | +5 | (V{I}=V{DD}) |

| 高電平邏輯輸入電流(SI和EN) | - | +10 | - | -30 | (V{I}=V{DD}) |

| 低電平邏輯輸入電流(CK) | (I_{IL}) | -10 | - | +30 | (V_{I}=GND) |

| 低電平邏輯輸入電流(SI和EN) | - | -5 | - | +5 | (V_{I}=GND) |

應用場景

時鐘分配網絡

ADN4670非常適合用于時鐘分配網絡,能夠將一個時鐘信號精確地分配到多個負載,確保各個部分的時鐘同步,提高系統的穩定性和可靠性。例如,在數據中心的服務器集群中,需要為多個處理器和芯片提供同步的時鐘信號,ADN4670可以滿足這一需求。

編程與配置

編程步驟

- 使能編程:將EN引腳置為高電平,允許編程操作。

- 數據輸入:在CK引腳的每個從0到1的轉換時,將SI引腳上的數據時鐘輸入到器件中。數據必須在時鐘轉換前的建立時間((t{SU}))內保持穩定,并在轉換后的保持時間((t{H}))內保持不變。

- 數據傳輸:需要11位數據進行編程,從第0位開始,依次決定輸出Q9/Q9到Q0/Q0的啟用或禁用,第10位選擇輸入時鐘(0 = CLK0/CLK0,1 = CLK1/CLK1)。然后,需要第12個時鐘脈沖將數據從移位寄存器傳輸到控制寄存器。

控制邏輯真值表

| CK | EN | SI | CLKO | CLKO | CLK1 | CLK1 | Q0 to Q9 | Q0 to Q9 |

|---|---|---|---|---|---|---|---|---|

| L | L | L | L | H | X | X | L | H |

| L | L | L | H | L | X | X | H | L |

| L | L | L | Open | Open | X | X | L | H |

| L | L | H | X | X | L | H | L | H |

| L | L | H | X | X | H | L | H | L |

| L | L | H | X | X | Open | Open | L | H |

注意事項

絕對最大額定值

使用時應注意器件的絕對最大額定值,如電源電壓范圍((V{CC})到GND為 -0.3 V至 +2.8 V)、輸入電壓范圍(輸入電壓到GND為 -0.2 V至 ((V{DD}+0.2) ) V)等。超過這些額定值可能會導致器件永久性損壞。

ESD防護

ADN4670是靜電放電(ESD)敏感器件,盡管產品具有專利或專有保護電路,但在操作過程中仍需采取適當的ESD防護措施,以避免性能下降或功能喪失。

輸入終端匹配

為了確保信號的質量,應在時鐘輸入引腳CLK0到CLK0和CLK1到CLK1之間使用100 Ω電阻進行終端匹配,并盡量靠近輸入引腳放置。

總結

ADN4670作為一款高性能的可編程低電壓1:10 LVDS時鐘驅動器,憑借其低輸出偏斜、靈活的可編程性、高信號速率等特性,為電子工程師在時鐘分配網絡設計中提供了一個優秀的解決方案。在實際應用中,工程師需要根據具體的設計需求,合理配置器件的參數,并注意相關的使用注意事項,以充分發揮其性能優勢。

你在使用ADN4670的過程中遇到過哪些問題呢?或者對于時鐘驅動器的設計,你有什么獨特的見解嗎?歡迎在評論區分享你的經驗和想法。

-

時鐘分配

+關注

關注

0文章

20瀏覽量

8243 -

ADN4670

+關注

關注

0文章

5瀏覽量

7691

發布評論請先 登錄

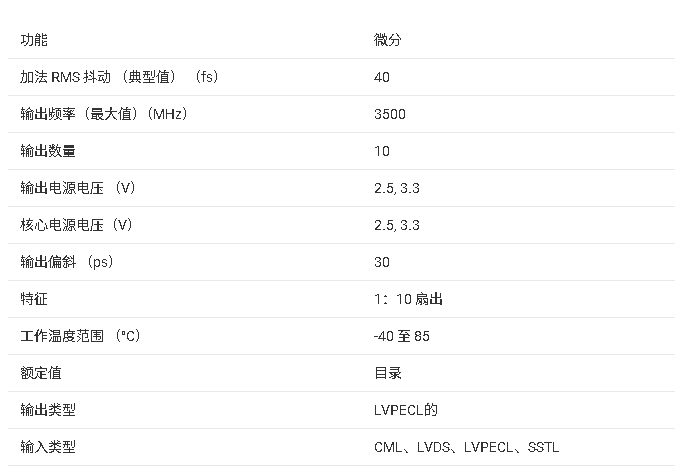

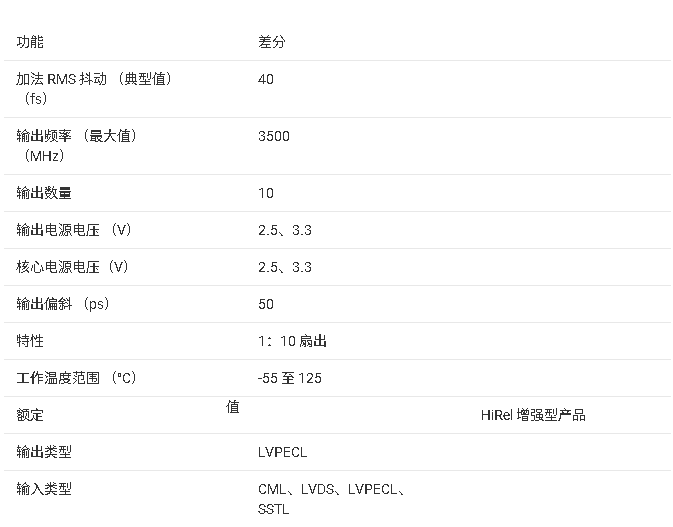

CDC391時鐘驅動器:特性、參數與應用解析

CDC340:高性能1線轉8線時鐘驅動器的深度解析

CDC2516:高性能鎖相環時鐘驅動器的深度解析

CDC319:高性能1線轉10線時鐘驅動器

CDCVF2509:高性能PLL時鐘驅動器的深度解析

CDCLVP110:高性能低電壓時鐘驅動器的卓越之選

CDCLVD110A可編程低壓1:10 LVDS時鐘驅動器詳解

深入剖析 CDCLVP215:低電壓雙差分 1:5 LVPECL 時鐘驅動器

CDCLVP111:高性能低電壓時鐘驅動器的卓越之選

低電壓 1:10 LVPECL 可選擇輸入時鐘驅動器 CDCLVP111-EP 深度解析

深入解析CDCLVP111-SEP:低電壓1:10 LVPECL時鐘驅動器

?CDCLVP111 低電壓1:10 LVPECL時鐘驅動器技術文檔總結

?CDCLVP111-EP 低電壓1:10 LVPECL時鐘驅動器技術文檔總結

ADN4670可編程低壓1:10 LVDS時鐘驅動器技術手冊

解析ADN4670:可編程低電壓1:10 LVDS時鐘驅動器

解析ADN4670:可編程低電壓1:10 LVDS時鐘驅動器

評論