AD9577 時(shí)鐘發(fā)生器:高性能與靈活性的完美結(jié)合

在電子設(shè)計(jì)領(lǐng)域,時(shí)鐘發(fā)生器是確保系統(tǒng)穩(wěn)定運(yùn)行的關(guān)鍵組件。今天,我們將深入探討 Analog Devices 的 AD9577 時(shí)鐘發(fā)生器,它以其卓越的性能和豐富的功能,為數(shù)據(jù)通信等應(yīng)用提供了理想的時(shí)鐘解決方案。

文件下載:AD9577.pdf

一、AD9577 概述

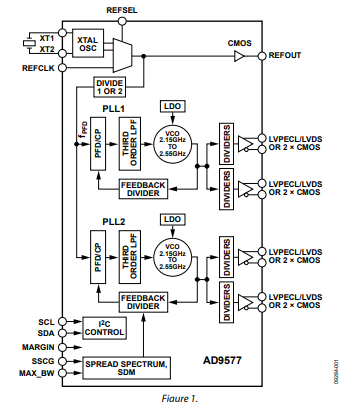

AD9577 是一款高度集成的時(shí)鐘發(fā)生器,具備雙 PLL/VCO 核心,包括一個(gè)整數(shù) - N PLL 和一個(gè)分?jǐn)?shù) - N PLL。它能夠提供連續(xù)的頻率覆蓋,從 11.2 MHz 到 200 MHz,并且在 200 MHz 到 637.5 MHz 的大部分頻率范圍內(nèi)也能正常工作。其低相位抖動(dòng)和低相位噪聲的特性,使其非常適合對(duì)時(shí)鐘精度要求極高的應(yīng)用場(chǎng)景。

二、關(guān)鍵特性剖析

1. 雙 PLL 架構(gòu)

AD9577 的雙 PLL 設(shè)計(jì)為系統(tǒng)提供了強(qiáng)大的時(shí)鐘生成能力。PLL1 是整數(shù) - N PLL,PLL2 則是分?jǐn)?shù) - N PLL,可選擇以整數(shù) - N 模式運(yùn)行以實(shí)現(xiàn)最佳抖動(dòng)性能。這種架構(gòu)使得 AD9577 能夠滿足不同應(yīng)用對(duì)時(shí)鐘頻率的多樣化需求。

2. 低相位抖動(dòng)

PLL1 的相位抖動(dòng)(12 kHz 到 20 MHz)典型值為 460 fs rms,PLL2 在整數(shù) - N 模式下的相位抖動(dòng)典型值為 470 fs rms,分?jǐn)?shù) - N 模式下為 660 fs rms。低相位抖動(dòng)確保了時(shí)鐘信號(hào)的穩(wěn)定性和準(zhǔn)確性,減少了數(shù)據(jù)傳輸中的誤差。

3. 寬頻率覆蓋

能夠覆蓋從 11.2 MHz 到 637.5 MHz 的廣泛頻率范圍,滿足了多種應(yīng)用的需求,如以太網(wǎng)、光纖通道、SONET、SDH 等。

4. 輸出配置靈活

支持多達(dá) 4 個(gè) LVDS/LVPECL 或 8 個(gè) LVCMOS 輸出時(shí)鐘,以及一個(gè) CMOS 緩沖參考時(shí)鐘輸出。用戶可以根據(jù)實(shí)際需求靈活配置輸出格式,提高了設(shè)計(jì)的靈活性。

5. 擴(kuò)頻功能

支持 - 0.5% 的下擴(kuò)頻,通過(guò)擴(kuò)展時(shí)鐘信號(hào)的能量分布,降低了時(shí)鐘源和相關(guān)電路的峰值功率輸出,從而減少了電磁干擾(EMI)輻射。

6. 頻率裕量功能

通過(guò) MARGIN 引腳,AD9577 可以生成第二個(gè)獨(dú)立的頻率映射,用于測(cè)試系統(tǒng)的頻率魯棒性。

三、技術(shù)細(xì)節(jié)解讀

1. 參考輸入與分頻器

參考輸入可以選擇晶體振蕩器輸出或參考輸入時(shí)鐘。當(dāng)選擇晶體振蕩器時(shí),需要一個(gè) 19.44 MHz 到 27 MHz 的外部晶體,總負(fù)載電容為 14 pF。參考分頻器可以將參考輸入頻率分頻 1 或 2,以確保輸入到 PLL 的頻率在 19.44 MHz 到 27 MHz 范圍內(nèi)。

2. 輸出通道分頻器

每個(gè) VCO 和芯片輸出之間有兩個(gè)分頻級(jí):VCO 分頻器(分頻比為 2 到 6)和輸出分頻器(分頻比為 1 到 32)。這種級(jí)聯(lián)分頻器允許最小輸出通道分頻比為 2,最大為 192,使得 AD9577 能夠在廣泛的頻率范圍內(nèi)進(jìn)行編程。

3. 輸出配置

每個(gè)輸出端口可以獨(dú)立配置為差分 LVPECL、差分 LVDS 或兩個(gè)單端 LVCMOS 時(shí)鐘輸出。LVDS 輸出采用電流模式輸出級(jí),LVPECL 輸出需要適當(dāng)?shù)慕K端電阻來(lái)確保信號(hào)質(zhì)量。

4. PLL 設(shè)計(jì)

- PLL1 整數(shù) - N PLL:通過(guò)設(shè)置反饋分頻器值(Na),VCO 輸出頻率可以在 2.15 GHz 到 2.55 GHz 范圍內(nèi)調(diào)整為 PFD 輸入頻率的整數(shù)倍。

- PLL2 分?jǐn)?shù) - N PLL:通過(guò)設(shè)置反饋分頻器值(Nb)、Σ - Δ 調(diào)制器分?jǐn)?shù)(FRAC)和模數(shù)(MOD),VCO 輸出頻率可以調(diào)整為 PFD 輸入頻率的分?jǐn)?shù)倍。

5. 擴(kuò)頻時(shí)鐘生成(SSCG)

通過(guò) SSCG 引腳,PLL2 可以進(jìn)入擴(kuò)頻模式,輸出頻率以三角波輪廓進(jìn)行調(diào)制。通過(guò)控制反饋分頻器的分頻比,實(shí)現(xiàn)頻率調(diào)制,從而降低時(shí)鐘信號(hào)的峰值功率。

四、應(yīng)用案例分析

AD9577 適用于多種數(shù)據(jù)通信應(yīng)用,如以太網(wǎng)、光纖通道、SONET、SDH 等。以下是一個(gè)典型的應(yīng)用示例: 在一個(gè)以太網(wǎng)系統(tǒng)中,AD9577 可以為系統(tǒng)提供穩(wěn)定的時(shí)鐘信號(hào)。通過(guò)合理配置 PLL1 和 PLL2 的參數(shù),可以生成滿足以太網(wǎng)不同速率要求的時(shí)鐘頻率。例如,設(shè)置 PLL1 的輸出頻率為 156.25 MHz,PLL2 的輸出頻率為 100 MHz,以滿足以太網(wǎng)設(shè)備的時(shí)鐘需求。

五、設(shè)計(jì)建議

1. 優(yōu)化 PLL 性能

- 選擇較低的 VCO 頻率,因?yàn)?VCO 相位噪聲在較低頻率下通常更好。

- 確保兩個(gè) VCO 頻率相差至少 2 MHz,以避免抖動(dòng)性能下降。

- 在 PLL2 以分?jǐn)?shù) - N 模式運(yùn)行時(shí),避免使用分母具有 2、3 或 6 因子的分?jǐn)?shù),以及避免低和高分?jǐn)?shù),以減少分?jǐn)?shù)雜散和整數(shù)邊界雜散。

2. 電源和接地考慮

- 每個(gè)電源引腳應(yīng)具有獨(dú)立的去耦和連接到電源平面,以確保電源的穩(wěn)定性。

- 將設(shè)備的暴露焊盤(pán)通過(guò)至少九個(gè)過(guò)孔直接連接到接地平面,以提高接地性能。

- 注意輸出走線與參考或晶體輸入電路的隔離,避免耦合干擾。

六、總結(jié)

AD9577 時(shí)鐘發(fā)生器以其高性能、靈活性和豐富的功能,為電子工程師提供了一個(gè)強(qiáng)大的時(shí)鐘解決方案。無(wú)論是在數(shù)據(jù)通信、數(shù)字視頻還是其他對(duì)時(shí)鐘精度要求較高的應(yīng)用中,AD9577 都能夠滿足需求。通過(guò)合理的設(shè)計(jì)和優(yōu)化,我們可以充分發(fā)揮 AD9577 的優(yōu)勢(shì),實(shí)現(xiàn)系統(tǒng)的穩(wěn)定運(yùn)行。

你在使用 AD9577 過(guò)程中遇到過(guò)哪些問(wèn)題?或者你對(duì)時(shí)鐘發(fā)生器的設(shè)計(jì)有什么獨(dú)特的見(jiàn)解?歡迎在評(píng)論區(qū)分享你的經(jīng)驗(yàn)和想法。

-

數(shù)據(jù)通信

+關(guān)注

關(guān)注

2文章

535瀏覽量

35119 -

時(shí)鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

349瀏覽量

70106 -

AD9577

+關(guān)注

關(guān)注

0文章

5瀏覽量

10390

發(fā)布評(píng)論請(qǐng)先 登錄

AD9522-5:高性能時(shí)鐘發(fā)生器的設(shè)計(jì)與應(yīng)用

AD9522-1:高性能時(shí)鐘發(fā)生器的深度剖析與應(yīng)用指南

AD9522-3:高性能時(shí)鐘發(fā)生器的技術(shù)剖析與應(yīng)用指南

AD9517-0:高性能多輸出時(shí)鐘發(fā)生器的全面解析

CDCM1802時(shí)鐘緩沖器:高性能與靈活性的完美結(jié)合

深入剖析CDCE949與CDCEL949:高性能可編程時(shí)鐘發(fā)生器

CDCE(L)925:靈活低功耗LVCMOS時(shí)鐘發(fā)生器的技術(shù)剖析

TLV320ADC3140音頻ADC:高性能與靈活性的完美結(jié)合

TLV320ADC6120音頻ADC:高性能與靈活性的完美結(jié)合

TLV320ADC5120音頻ADC:高性能與靈活性的完美結(jié)合

TAA3020音頻ADC:高性能與靈活性的完美結(jié)合

深入解析RC22112A FemtoClock時(shí)鐘發(fā)生器:高性能與低功耗的完美結(jié)合

深入解析 RENESAS SLG51003 PMIC:高性能與靈活性的完美結(jié)合

探索XMC7000工業(yè)微控制器:高性能與靈活性的完美結(jié)合

AD9577帶雙路PLL、擴(kuò)頻和余量微調(diào)功能的時(shí)鐘發(fā)生器技術(shù)手冊(cè)

AD9577 時(shí)鐘發(fā)生器:高性能與靈活性的完美結(jié)合

AD9577 時(shí)鐘發(fā)生器:高性能與靈活性的完美結(jié)合

評(píng)論