CDCM1802時鐘緩沖器:高性能與靈活性的完美結合

在電子設計領域,時鐘信號的穩定傳輸和精準分配至關重要。今天,我們要深入探討一款功能強大的時鐘緩沖器——CDCM1802,它以其獨特的特性和廣泛的應用場景,成為眾多工程師的首選。

文件下載:cdcm1802.pdf

1. 產品概述

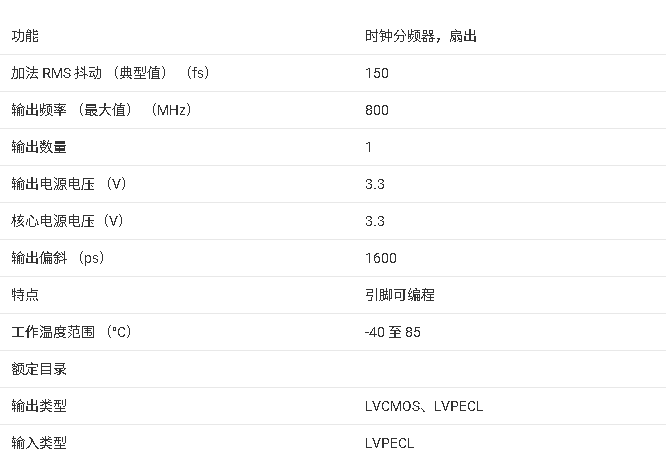

CDCM1802是一款帶有可編程分頻器的時鐘緩沖器,由德州儀器(TI)生產。它能夠將一路差分時鐘輸入分配為一路LVPECL差分時鐘輸出和一路LVCMOS單端輸出,為不同類型的設備提供了靈活的時鐘信號源。該芯片采用16引腳VQFN封裝(3.00 mm × 3.00 mm),體積小巧,適合各種緊湊的設計需求。

2. 關鍵特性

2.1 輸出分配與分頻

- 信號分配:將一路差分時鐘輸入精準分配到LVPECL差分時鐘輸出和LVCMOS單端輸出,滿足不同接口設備的需求。

- 可編程分頻:LVPECL和LVCMOS輸出均具備可編程分頻功能,分頻系數可選擇1、2、4和8,通過三個3級控制引腳(S0、S1和EN)進行設置,為不同的時鐘頻率需求提供了極大的靈活性。

2.2 低噪聲設計

LVCMOS輸出相對于PECL輸出階段延遲1.6 ns,有效減少了信號轉換期間的噪聲影響,確保信號的穩定傳輸。

2.3 寬工作范圍

- 電源電壓:支持3.3V電源供電,同時在2.5V下仍能保持功能正常,適應不同的電源環境。

- 信號速率:LVPECL輸出的信號速率高達800 MHz,LVCMOS輸出的信號速率可達200 MHz,滿足高速數據傳輸的需求。

2.4 差分輸入與偏置電壓輸出

差分輸入級具有較寬的共模范圍,幾乎可以接受任何類型的差分信號(如LVPECL、LVDS、CML、HSTL)。同時,它還提供VBB偏置電壓輸出,可作為單端輸入信號的共模電壓參考,方便設計。

3. 應用領域

CDCM1802的高性能使其在多個領域得到廣泛應用:

- 網絡和數據通信:確保時鐘信號的穩定傳輸,提高數據傳輸的準確性和可靠性。

- 醫療成像:為成像設備提供精確的時鐘信號,保證圖像的高質量。

- 便攜式測試和測量:滿足便攜式設備對小型化和高性能的要求。

- 高端音視頻:為音視頻設備提供穩定的時鐘,保證音視頻的同步和流暢。

4. 詳細規格

4.1 絕對最大額定值

- 最大結溫:125°C

- 存儲溫度范圍: - 65°C至150°C

4.2 ESD評級

- 人體模型(HBM):±3000 V

- 帶電器件模型(CDM):±1500 V

4.3 推薦工作條件

- 電源電壓:3V至3.6V(3.3V為標稱值)

- 工作溫度范圍: - 40°C至85°C

4.4 電氣特性

- LVPECL輸入:輸入頻率可達800 MHz,輸入電壓擺幅為500 mV至1300 mV。

- LVPECL輸出:輸出頻率可達800 MHz,輸出電壓擺幅為500 mV。

- LVCMOS輸出:輸出頻率可達200 MHz,高電平輸出電壓和低電平輸出電壓滿足不同負載要求。

4.5 開關特性

- LVPECL輸出:輸出占空比失真、部分到部分的偏斜、上升和下降時間等指標均表現出色。

- LVCMOS輸出:與LVPECL輸出之間的偏斜為1.6 ns,確保信號的同步性。

4.6 抖動特性

- LVPECL輸出和LVCMOS輸出的附加相位抖動均在極小范圍內,保證了時鐘信號的穩定性。

4.7 電源電流特性

- 滿載時的電源電流為100 mA,無負載時為85 mA,三態時為0.5 mA,功耗較低。

5. 功能模式與控制

5.1 控制引腳設置

CDCM1802通過三個3級控制引腳(S0、S1和EN)來選擇不同的輸出模式。每個引腳有三種配置:接地(邏輯0)、通過60 kΩ下拉電阻拉至VDD/2或浮空(邏輯1)。具體的模式選擇可參考選擇模式表。

5.2 設備行為

- 復位和控制引腳切換:在禁用模式(EN = 0)下,所有輸出驅動器處于高阻態,相關電路關閉,觸發器復位。啟用設備時,參考電壓和電流的建立時間最長為1 μs,輸出信號在建立時間后進入正常狀態。

- 單個輸出級啟用:單個輸出級啟用時,Y0的初始狀態不確定,Y0為Y0的反相信號。隨著第一個正時鐘過渡,未分頻的輸出變為輸入時鐘狀態,分頻輸出根據內部分頻器狀態確定。

6. 應用與實現

6.1 輸入終端匹配

- LVPECL接收器輸入終端匹配:為了優化噪聲性能,建議對PCB走線(傳輸線)進行適當的終端匹配。可參考相關應用筆記(SCAA062和SCAA059)中的AC耦合和DC耦合終端匹配技術。

- LVCMOS接收器輸入終端匹配:對于單端輸入信號,可采用特定的電路設置,如使用AC耦合電容、負載電阻和偏置電壓輸出等。

6.2 典型應用

以一個扇出緩沖器應用為例,CDCM1802可以從背板選擇100 MHz的LVPECL時鐘信號,并將其扇出到所需的設備。通過設置控制引腳(S0、S1和EN),可以實現LVCMOS輸出分頻為4,LVPECL輸出分頻為1。在設計過程中,需要注意輸入和輸出的終端匹配,以及根據實際需求選擇合適的分頻模式。

7. 電源供應與布局建議

7.1 電源供應

高性能時鐘緩沖器對電源噪聲非常敏感,因此需要采取措施降低電源噪聲。建議使用濾波電容消除低頻噪聲,旁路電容提供高頻噪聲的低阻抗路徑,并在板級電源和芯片電源之間插入鐵氧體磁珠,以隔離時鐘驅動器產生的高頻開關噪聲。

7.2 布局

- 布局指南:為了確保良好的熱流,建議在應用中設計四個熱過孔,將VQFN 16引腳封裝的熱量有效地傳導到PCB上。

- 布局示例:通過合理的熱過孔放置和銅平面設計,實現良好的散熱效果。

- 熱考慮:根據封裝熱阻和功率消耗計算結溫,確保設備在安全的溫度范圍內工作。

8. 設備與文檔支持

8.1 設備支持

TI提供設備支持,但對于第三方產品或服務不構成推薦或保證。

8.2 文檔支持

相關文檔包括SCAA062、SCAA059、SCBA017和SLUA271等,可提供更詳細的技術信息。

8.3 社區資源

TI的E2E在線社區為工程師提供了交流和解決問題的平臺,同時還提供設計支持工具和技術支持聯系方式。

8.4 靜電放電注意事項

由于該設備的內置ESD保護有限,在存儲或處理時應將引腳短路或放置在導電泡沫中,以防止MOS柵極受到靜電損壞。

9. 總結

CDCM1802時鐘緩沖器以其豐富的特性、廣泛的應用領域和出色的性能,為電子工程師提供了一個可靠的時鐘信號解決方案。在實際設計中,工程師需要根據具體的應用需求,合理設置控制引腳、優化電源供應和布局,以充分發揮CDCM1802的優勢。你在使用CDCM1802的過程中遇到過哪些問題?你認為它在哪些方面還有改進的空間?歡迎在評論區分享你的經驗和想法。

-

時鐘緩沖器

+關注

關注

2文章

270瀏覽量

51910 -

電子設計

+關注

關注

42文章

1681瀏覽量

49848

發布評論請先 登錄

?CDCM1802時鐘緩沖器技術文檔總結

CDCM1802時鐘緩沖器:高性能與靈活性的完美結合

CDCM1802時鐘緩沖器:高性能與靈活性的完美結合

評論