芯片測試的本質是 “在原子級精度下,驗證每一個晶體管的可靠性”。早年 28nm 及以上成熟制程,測試核心是 “篩選壞片”,流程相對簡單;但隨著制程進入 14nm 及以下,尤其是 3nm、2nm 節點,測試早已不是 “篩選” 那么簡單,而是要應對工藝復雜度、工具一致性、公差極限等多重挑戰,難度呈指數級攀升。

工藝復雜度的飆升,是測試難度增加的核心根源。正如 Onto Innovation 應用工程總監 PeiFen Teh 所說,先進節點需要數百道緊密關聯的工藝步驟,從多重圖案化、高介電常數 / 金屬柵極,到選擇性沉積、埋入式電源軌,每一步的微小缺陷都可能累積成良率災難。一枚晶圓三個月內要經過 600-800 道工序,測試系統必須精準捕捉每一道工序的偏差,這對測試精度的要求已達到亞納米級別 —— 比如 3nm 節點,套刻精度需要控制在 0.3nm 以內,相當于一根頭發絲直徑的百萬分之一,這種極限精度,早已逼近測試設備的物理極限。

更棘手的是工具匹配(TTTM)的難度翻倍。芯片制造需要多臺同型號設備協同工作,測試的前提是 “所有設備的輸出結果一致”,這就是工具匹配的核心意義。但先進制程下,設備的 “個體差異” 被無限放大 —— 每臺設備的腔室磨損、光學元件偏差、環境影響,都會導致測試結果出現非線性偏差。更關鍵的是,工具匹配并非一勞永逸:設備安裝、工藝迭代、維護換件后,都需要重新匹配,先進節點甚至需要每天、每班多次匹配。

更具挑戰的是,供應鏈的分散化讓工具匹配雪上加霜。泰瑞達智能制造產品經理 Eli Roth 提到,如今半導體供應鏈遍布全球,不同晶圓廠、不同生產線的設備,需要實現測試結果的完全一致,這就要求不僅要匹配單廠內的設備,還要跨廠、跨區域匹配。更苛刻的是,先進封裝技術將多顆芯片集成在一起,測試需要兼顧不同芯片的兼容性,誤差來源呈幾何級增加,對測試重復性的要求達到了前所未有的高度。

公差收緊與隨機效應的凸顯,讓測試陷入 “兩難困境”。隨著特征尺寸縮小,芯片的線寬、線邊緣粗糙度等隨機效應,成為影響測試準確性的關鍵。Fractilia 聯合創始人 Chris Mack 坦言,現在的測試很難達到 NIST 標準下的 “絕對準確”,只能追求極致的 “精度”—— 通過多次測量減少變異,但亞納米級的公差的下,哪怕是微小的環境波動,都可能導致測試結果偏差,這也是英特爾 “完全復制” 晶圓廠流程,卻仍出現差異的核心原因。

數據激增與機器學習的局限性,進一步加劇了測試難度。先進節點的測試會產生海量高分辨率數據,包括波形特征、時序測量、連續遙測數據等,傳統的統計方法已無法處理這些高維數據。雖然機器學習能捕捉工具的細微非線性行為,輔助工具指紋識別和異常檢測,但它并非 “萬能解藥”—— 它需要大量標注數據訓練,且無法完全替代人工對復雜缺陷的判斷,更多是傳統測試方法的補充,而非替代。

除此之外,產品生命周期縮短、良率提升速度加快,也給測試帶來了額外壓力。新品導入(NPI)的時間不斷壓縮,工程師需要在更短的時間內完成測試方案驗證、工具匹配和流程穩定,容錯空間被無限壓縮。同時,Chiplet、3D 堆疊等先進封裝技術的普及,讓測試從 “單一芯片測試” 轉向 “系統級測試”,需要兼顧芯片間的互連可靠性、熱穩定性等,測試維度大幅增加。

其實,芯片測試難度的飆升,本質上是半導體產業向 “原子級制造” 邁進的必然代價。測試不再是 “后端輔助”,而是貫穿制造全流程的 “良率守門員”—— 它既要捕捉工藝缺陷,也要保障設備一致性,還要應對供應鏈和技術迭代的挑戰。

-

測試

+關注

關注

9文章

6308瀏覽量

131546 -

晶體管

+關注

關注

78文章

10423瀏覽量

148213 -

芯片測試

+關注

關注

6文章

181瀏覽量

21174

發布評論請先 登錄

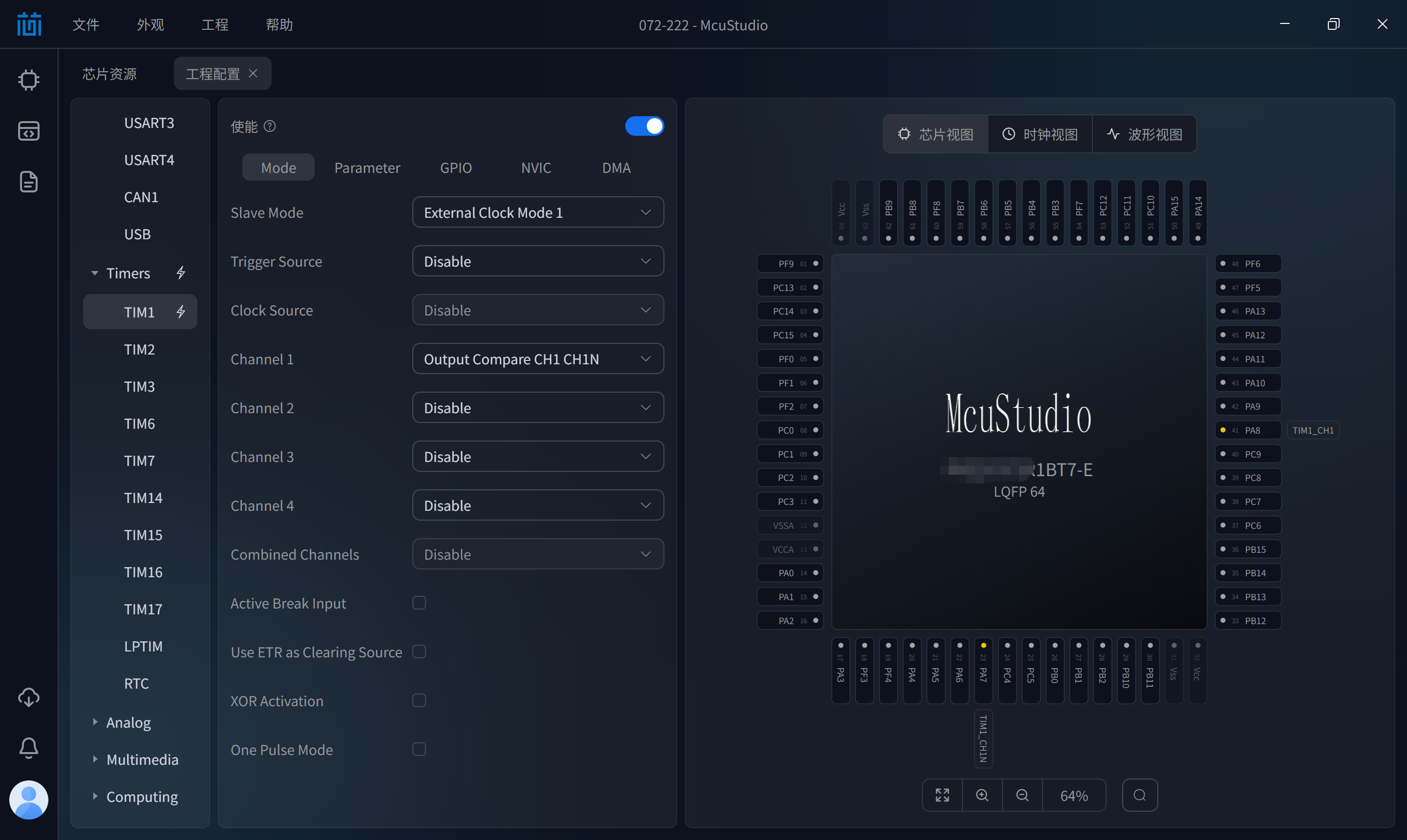

為什么原廠越來越需要一套自己的 Studio

為什么原廠越來越需要一套自己的 Studio

為什么機器人控制器越來越偏愛 RK3588?

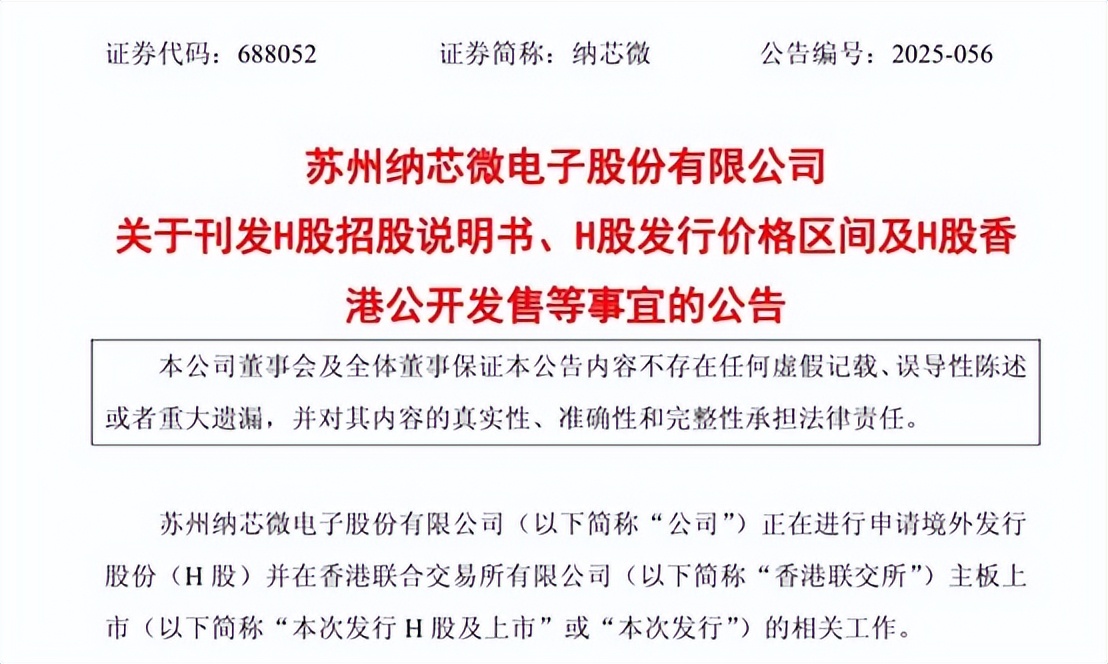

納芯微:不只產品領先,更以體系致勝

后摩爾時代:芯片不是越來越涼,而是越來越燙

全橋LLC的上管驅動芯片14、15總是短路,驅動芯片是那納芯微的NSI6602A,請問各位前輩該怎么解決,感謝!!

芯片的驗證為何越來越難?

納芯微攜新品新系列亮相上海慕展,引領“芯”未來

【微納談芯】芯片測試越來越難的背后

【微納談芯】芯片測試越來越難的背后

評論