CDCM61004:高性能、低抖動時鐘發生器的設計與應用

在電子設計領域,時鐘發生器的性能對于系統的穩定性和可靠性至關重要。今天我們要探討的CDCM61004就是一款備受關注的低抖動時鐘發生器,它在高速數據通信等領域有著廣泛的應用前景。

文件下載:cdcm61004.pdf

一、CDCM61004的特性亮點

1. 輸入輸出特性

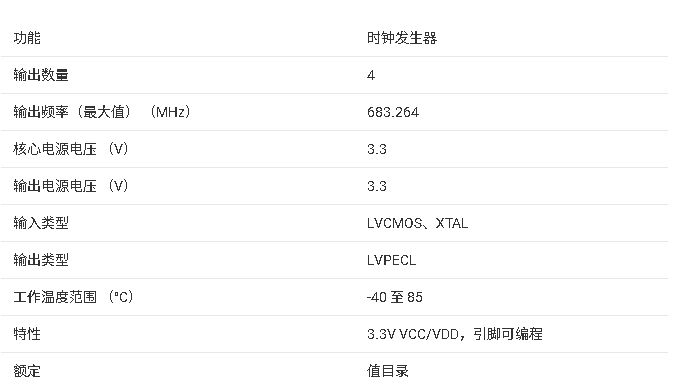

CDCM61004支持多種輸入頻率,包括24.8832 MHz、25 MHz和26.5625 MHz等,輸入頻率范圍為21.875 MHz至28.47 MHz。它擁有4路輸出,可通過引腳選擇LVPECL、LVDS或2-LVCMOS輸出類型,并且工作在3.3 V電壓下。輸出頻率范圍為43.75 MHz至683.264 MHz,還支持常見的輸出頻率,如62.5 MHz、75 MHz、100 MHz等。此外,它還有LVCMOS旁路輸出,方便對輸入晶體的加載情況進行監測。

2. 內部結構特性

芯片內部集成了VCO,工作頻率范圍為1.75 GHz至2.05 GHz。PLL的內部環路帶寬為400 kHz,高性能的PLL核心能夠有效降低抖動。例如,對于625-MHz的LVPECL輸出,相位噪聲典型值為 -146 dBc/Hz(5-MHz偏移),隨機抖動典型值為0.509 ps(RMS,10 kHz至20 MHz)。輸出占空比可校正到50%(± 5%),LVPECL輸出的低輸出偏斜僅為30 ps。

3. 控制與電源特性

通過控制引腳可以對預分頻器、反饋分頻器、輸出分頻器和輸出類型進行編程設置。芯片還具有使能控制引腳,方便進行電源管理。其核心和I/O采用3.3-V電源供電,工作溫度范圍為 -40°C至85°C,采用5-mm × 5-mm、32引腳的VQFN封裝,并且ESD保護超過2 kV(HBM)。

二、CDCM61004的應用場景

CDCM61004適用于高端數據通信應用,如SONET、以太網、光纖通道、串行ATA和HDTV等。它可以作為低成本、高性能的高頻晶體振蕩器的替代方案,為這些系統提供低抖動的時鐘信號,確保數據傳輸的準確性和穩定性。

三、CDCM61004的詳細工作原理

1. 整體架構

CDCM61004是一款高度通用的低抖動頻率合成器,其核心是一個PLL,它能夠將VCO與輸入信號同步。輸入信號可以是低頻晶體或LVCMOS信號,輸出信號共享一個由VCO核心驅動的輸出分頻器。所有的設備設置都可以通過控制引腳進行管理。

2. 關鍵模塊分析

- PLL模塊:PLL由晶體輸入接口、相位頻率檢測器(PFD)、電荷泵、片上環路濾波器以及預分頻器和反饋分頻器組成。PLL由片上的低壓差(LDO)線性穩壓器供電,這些穩壓器能夠有效隔離外部電源噪聲對PLL的影響。

- 晶體輸入接口:推薦使用基模振蕩的晶體,采用并聯諧振電路。在計算離散電容組件的值時,需要考慮所有的電容源,以確保晶體能夠在預期參數內振蕩。同時,良好的布局對于晶體振蕩器的正常工作至關重要,要盡量減少晶體和XIN引腳之間的布線距離,避免信號干擾和噪聲耦合。

- VCO模塊:VCO的校準是確保設備正常工作的關鍵步驟。在設備上電初始化或通過RSTN引腳進行復位后,會啟動VCO校準序列。校準過程需要PLL正確設置并鎖定,并且參考時鐘輸入必須穩定。為了保證參考輸入在VCO校準開始時穩定,建議在RSTN引腳上設置延遲電路。

四、CDCM61004的設計與應用要點

1. 啟動時間估算

CDCM61004的啟動時間可以根據參考時鐘周期、電源上升時間、參考啟動時間、延遲時間、VCO校準時間和PLL鎖定時間等參數進行估算。了解這些參數有助于我們在設計系統時合理安排時鐘信號的生成時間。

2. 輸出端接

不同的輸出類型(LVPECL、LVDS、LVCMOS)需要不同的端接方式。例如,LVPECL輸出需要適當的偏置和端接,以確保設備正常工作和信號完整性;LVDS輸出需要在接收器端使用100 Ω的端接電阻;LVCMOS輸出可以采用串聯端接電阻來維持信號完整性。

3. 電源供應與濾波

PLL對電源噪聲非常敏感,因此需要采取有效的電源濾波措施。使用濾波電容和旁路電容可以減少電源噪聲,旁路電容應靠近電源引腳布局,以降低電感。同時,將模擬電源和輸出/輸入電源分開,并在兩者之間插入鐵氧體磁珠,可以有效隔離高頻開關噪聲。

4. 布局設計

在PCB布局時,要注意CDCM61004的熱管理和信號完整性。芯片的暴露焊盤需要與PCB的接地層良好連接,以提供有效的散熱路徑。同時,要避免信號干擾和噪聲耦合,確保晶體組件靠近XIN引腳布局。

五、總結與思考

CDCM61004憑借其高性能、低抖動的特性,為高速數據通信等領域的設計提供了一個優秀的解決方案。在實際應用中,我們需要充分了解其工作原理和設計要點,合理進行參數設置和布局設計,以確保系統的穩定性和可靠性。大家在使用CDCM61004的過程中,有沒有遇到過一些特殊的問題或者有什么獨特的設計經驗呢?歡迎在評論區分享交流。

-

時鐘發生器

+關注

關注

1文章

352瀏覽量

70130 -

低抖動

+關注

關注

0文章

74瀏覽量

6116

發布評論請先 登錄

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

CDCM61004四路輸出、集成VCO、低抖動時鐘發生器數據表

CDCM61002兩路輸出、集成VCO、低抖動時鐘發生器數據表

CDCM61004:高性能、低抖動時鐘發生器的設計與應用

CDCM61004:高性能、低抖動時鐘發生器的設計與應用

評論