邁向極致效率:SiC MOSFET與LLC諧振變換器的協同設計與優化

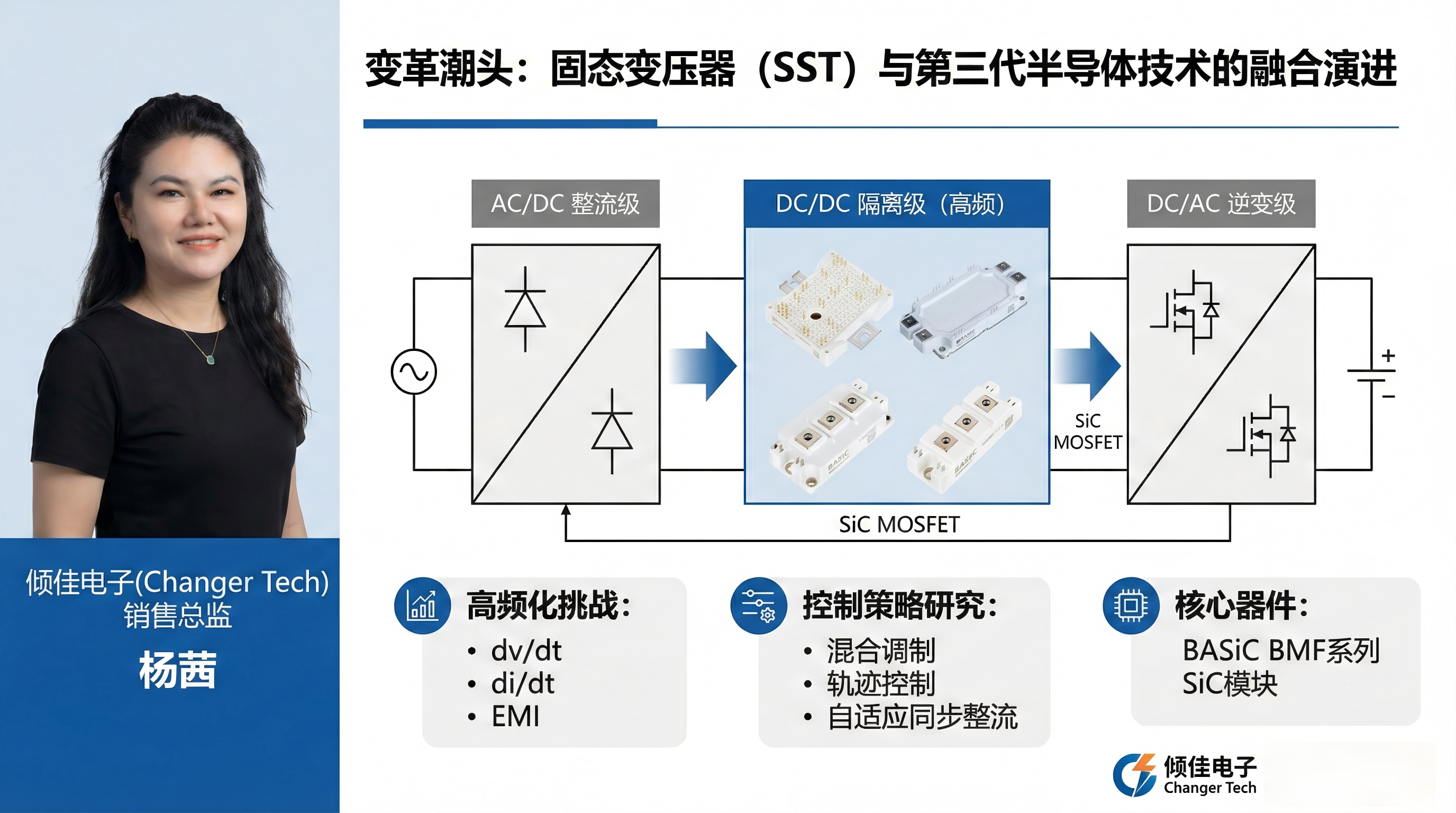

BASiC Semiconductor基本半導體一級代理商傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,代理并力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

第一章 引言:功率變換效率的“鈦金+”時代

在當今電力電子領域,無論是電動汽車(EV)的800V高壓快充架構,還是人工智能(AI)算力中心的高密度供電單元(PSU),對能量轉換效率的追求已經跨越了單純的“節能”范疇,轉而成為解決熱管理瓶頸、提升系統功率密度的核心手段。傳統的硅基(Silicon, Si)超結MOSFET在軟開關拓撲中雖然已將效率推升至96%-97%的水平,但受限于其本征的寄生電容非線性、反向恢復電荷(Qrr?)以及導通電阻(RDS(on)?)的溫度系數,難以進一步突破98%的效率天花板。

碳化硅(Silicon Carbide, SiC)功率器件的出現,憑借其寬禁帶特性帶來的高擊穿場強、低比導通電阻和卓越的熱導率,為突破這一瓶頸提供了物理基礎。然而,工程實踐表明,僅僅將硅器件替換為SiC器件,往往只能獲得有限的性能提升,甚至可能因高頻振蕩和EMI問題導致系統不穩定。要實現98.5%乃至99%以上的“前所未有”的效率,必須采用“協同設計”(Co-Design)的方法論。這種方法論打破了器件選擇、拓撲設計、磁性元件構建和控制策略之間的界限,將其視為一個強耦合的非線性多變量優化問題。

傾佳電子探討LLC諧振變換器與SiC MOSFET的協同設計機制,基于基本半導體(BASiC Semiconductor)和Wolfspeed等行業領軍企業的最新器件數據與參考設計,詳細闡述如何通過精確的參數匹配、磁集成技術以及自適應控制策略,實現轉換效率的極致突破。

第二章 SiC MOSFET在諧振開關中的物理特性與關鍵參數解析

理解SiC MOSFET在LLC拓撲中的行為,是進行協同設計的第一步。在LLC轉換器中,原邊開關管主要運行在零電壓開通(Zero Voltage Switching, ZVS)模式下。雖然ZVS消除了開通損耗,但關斷損耗、導通損耗以及死區時間內的體二極管損耗依然是制約效率提升的關鍵因素。

2.1 輸出電容(Coss?)的非線性與能量特性

在硬開關拓撲中,Coss?儲存的能量(Eoss?)在開通瞬間被耗散在溝道內,產生巨大的開通損耗。而在LLC軟開關拓撲中,這部分能量通過諧振網絡的感性電流在死區時間內被抽取并回饋至直流母線或轉移至對管,從而實現ZVS。然而,SiC MOSFET的Coss?特性與硅器件存在顯著差異,這對諧振參數的設計提出了新的要求。

根據基本半導體(BASiC Semiconductor)B3M025065Z(650V, 25mΩ)的數據手冊分析,其輸出電容在低壓段表現出高度的非線性,但在高壓段的線性度優于傳統硅超結器件 。具體而言,該器件在400V偏置下的典型輸出電容僅為180pF。更關鍵的是其儲存能量Eoss?。對于ZVS的實現,設計者不能僅參考單一電壓點的電容值,而必須關注“能量相關有效電容”(Co(er)?)。

SiC器件的一個顯著優勢在于其Co(er)?相對較小。這意味著在死區時間內,實現ZVS所需的勵磁電流(Magnetizing Current)峰值可以顯著降低。對于傳統硅器件,為了抽走巨大的Qoss?電荷,往往需要設計較小的勵磁電感(Lm?)以產生足夠大的勵磁電流,這直接導致了原邊繞組和開關管中巨大的環流損耗(Irms2?R)。而采用SiC MOSFET,如B3M011C120Z(1200V, 11mΩ),其極低的Coss?允許設計者大幅增加Lm?,從而在保證ZVS的前提下,將原邊環流降至最低,這是提升輕載和滿載效率的物理基礎 。

2.2 體二極管壓降(VSD?)與死區損耗的博弈

這是SiC MOSFET在LLC應用中最為棘手但也最具優化潛力的特性。由于SiC材料的寬禁帶特性(~3.26 eV),其體二極管的開啟電壓(VSD?)通常在3.5V至4.5V之間,遠高于硅MOSFET的0.9V-1.2V 。

在LLC變換器的死區時間內,當Coss?放電完畢后,體二極管會自然續流以箝位電壓。如果死區時間設置過長,負載電流將流經高壓降的體二極管,產生巨大的導通損耗。例如,假設死區時間內體二極管導通50ns,流過20A電流,對于VSD?=4V的SiC器件,單次開關周期的能量損耗為4V×20A×50ns=4μJ。在500kHz的高頻下,這相當于2W的功率損耗。對于一個追求99%效率的3kW變換器(總損耗預算僅30W),2W的額外損耗是不可接受的。

因此,SiC MOSFET的協同設計要求必須配合極高精度的死區控制。設計目標是將死區時間壓縮至剛好完成Coss?放電,且體二極管幾乎不導通的臨界狀態。這需要利用SiC器件“時間相關有效電容”(Co(tr)?)極其穩定的特性,通過精確計算或自適應控制來實現 。

2.3 導通電阻(RDS(on)?)的溫度穩定性與熱協同

在滿載工況下,導通損耗占據主導地位。硅基MOSFET的RDS(on)?隨溫度上升漂移嚴重,通常在150°C時達到25°C時的2.5倍以上。這種正反饋效應限制了器件在高溫下的電流處理能力。

相比之下,基本半導體的SiC MOSFET采用了先進的工藝,其RDS(on)?的溫度系數顯著更低。以B3M025065Z為例,其RDS(on)?從25°C時的25mΩ增加到175°C時的32mΩ,增幅僅為28% [1]。這意味著在同樣的高溫工況下,SiC MOSFET的實際運行電阻遠低于標稱值相近的硅器件。此外,基本半導體在B3M011C120Z等高端型號中引入了**銀燒結(Silver Sintering)**連接技術,將結到殼的熱阻(Rth(j?c)?)降低至0.15 K/W [1]。這種封裝層面的協同設計使得芯片產生的熱量能極快地導出,進一步降低了結溫,從而反過來維持了更低的RDS(on)?,形成良性的熱-電循環。

第三章 協同設計方法論:參數匹配與優化流程

要達到前所未有的效率,必須摒棄傳統的“先選管子,再算變壓器”的串行設計流程,轉而采用以能量平衡為核心的并行協同設計方法。

3.1 基于Eoss?積分的勵磁電感(Lm?)極致優化

傳統設計通常根據經驗設定死區時間,然后計算Lm?以滿足ZVS條件。在追求99%效率的SiC設計中,這一過程必須反轉并精細化。

第一步:非線性電荷積分

首先,必須基于SiC MOSFET datasheet中的Coss??VDS?曲線,通過積分計算出在特定母線電壓(Vin?)下,Coss?從0V充電至Vin?所需的總電荷量Qoss?和總能量Eoss?。

公式如下:

Ereq?=2×∫0Vin??Coss?(v)?vdv+21?Cxformer?Vin2?

這里必須乘以2,因為在半橋或全橋拓撲中,一個管子關斷充電的同時,互補管子正在放電。

第二步:計算最小勵磁電流

為了保證ZVS,勵磁電感提供的能量必須大于Ereq?。但在99%效率目標下,我們不能留有太大的余量,因為過大的勵磁電流會增加導通損耗。因此,目標是設定勵磁電流的峰值(Im,peak?)恰好能在預設的最大死區時間(tdead,max?)內完成充放電。

Im,peak?=tdead,max?2?Qoss?(Vin?)?

此處,Qoss?(Vin?)是關于電壓的積分電荷量,比單純用電容估算更準確 。

第三步:確定Lm?的最大值

一旦確定了最小的Im,peak?,即可推導出允許的最大勵磁電感Lm?。更大的Lm?意味著更小的環流,從而更高的效率。

Lm?=4?Im,peak?n?Vout??Tsw??

通過使用具有極低Coss?的SiC MOSFET(如BASiC B3M系列),設計者可以將Lm?設定為傳統硅基設計的2-3倍,從而大幅削減原邊銅損和開關管導通損耗 。

3.2 自適應死區時間控制策略(Adaptive Dead Time, ADT)

如前所述,SiC的高VSD?要求極高精度的死區控制。固定死區時間無法適應全負載范圍的變化,因為輕載下Coss?放電慢,重載下放電快。

優化設計方法:

引入基于VDS?檢測或模型預測的自適應死區控制。

檢測機制: 通過高壓隔離電容或輔助繞組實時檢測開關節點的電壓斜率(dv/dt)。

閉環控制: 數字控制器(DSP/FPGA)根據上一周期的dv/dt或零電壓跨越點,動態調整下一周期的死區時間,目標是使同步整流(SR)管或原邊主開關管在體二極管導通前的10-20ns內開通。

SiC特定優化: 利用SiC MOSFET開關速度極快(納秒級)的特點,可以將死區時間的調節步長設定得非常精細。研究表明,將死區時間從傳統的250ns縮減至優化的100ns甚至更低(取決于Lm?和負載),可減少體二極管導通損耗,并在輕載下提升0.5%以上的效率 。

3.3 諧振頻率與工作區域選擇

為了發揮SiC的高頻優勢并減小磁性元件體積,通常選擇300kHz至500kHz作為諧振頻率(fr?)。雖然SiC支持MHz級開關,但超過500kHz后,利茲線(Litz wire)的鄰近效應損耗和磁芯損耗會急劇上升,反而導致總效率下降。

設計準則:

將工作頻率設計在諧振頻率(fr?)附近,即fsw?≈fr?。此時,LC諧振槽的阻抗最小,且不僅原邊實現ZVS,副邊整流管也能實現零電流關斷(ZCS),消除了副邊二極管的反向恢復問題(雖然SiC二極管無反向恢復,但在同步整流MOSFET中ZCS依然關鍵以避免體二極管反向恢復損耗)。

利用SiC的寬安全工作區(SOA)和高耐壓特性,設計更高的直流母線電壓(如800V),這在相同功率下減小了電流,顯著降低了I2R損耗。

第四章 磁性元件的革命:矩陣變壓器與PCB繞組

在傳統的LLC設計中,變壓器往往是效率提升的瓶頸。對于大電流輸出應用(如800V轉48V的數據中心電源8),副邊繞組的端接損耗(Termination Loss)和漏感控制至關重要。協同設計要求磁性元件必須與SiC器件的封裝形式相配合。

4.1 矩陣變壓器(Matrix Transformer)結構

為了解決大電流下的繞組損耗問題,采用矩陣變壓器結構是實現99%效率的關鍵技術路線 。

原理: 將一個大變壓器拆分為多個小變壓器單元。例如,原邊繞組串聯,確保伏秒平衡和電流均勻;副邊繞組并聯,將輸出大電流分流。

磁通抵消(Flux Cancellation): 這是協同設計中的精髓。通過巧妙布置多個磁芯單元的位置和繞組方向,使得相鄰磁芯柱中的磁通相互抵消。這允許移除或減薄中間的磁柱,從而將磁芯體積和磁芯損耗降低30%以上 。CPES(弗吉尼亞理工大學電力電子系統中心)的研究表明,這種結構是實現99%效率轉換器的核心要素之一。

4.2 PCB繞組與同步整流集成

在高頻(>300kHz)下,傳統利茲線的端接非常困難且引入巨大的寄生電阻和電感。

PCB繞組: 利用多層PCB作為變壓器繞組,可以精確控制漏感(作為諧振電感Lr?的一部分,實現磁集成),并獲得極好的一致性。

SR器件集成: 為了徹底消除副邊大電流回路的端接損耗,必須將副邊的SiC或GaN同步整流MOSFET直接焊接在變壓器的PCB繞組輸出端。這種“器件埋入磁路”的協同設計消除了傳統設計中約0.5%的銅損。

第五章 效率數據與實證分析

基于上述設計方法,以下結合具體的SiC器件型號和參考設計,給出效率數據分析。

5.1 案例一:6kW戶儲高壓電池電池雙向CLLC

設計規格: 輸入380V-420V,輸出250V-450V電池電壓,雙向流動。

核心器件: 原邊和副邊均采用650V 40mΩ SiC MOSFET(基本半導體同規格B3M040075Z)。

開關頻率: 500kHz。

協同設計點: 利用變壓器漏感作為諧振電感(1μH),省去獨立電感;Lm?優化至30μH以平衡ZVS與環流。

效率數據:

峰值效率: 達到 98.5% (半載點,約3.3kW輸出)。

滿載效率: 保持在 98.0% 以上。

功率密度: 128 W/in3。

對比: 相比傳統硅基方案(約96%),損耗降低了60%以上,使得散熱器體積大幅縮減。

5.2 案例二:數據中心800V轉48V直流變換器

設計目標: 極致效率,無穩壓(DCX模式)。

核心技術: 矩陣變壓器 + 磁通抵消 + PCB繞組集成SR。

器件選擇: 原邊采用高壓SiC,副邊采用低壓高性能硅MOSFET。

效率數據:

峰值效率: 驚人的 99.1% 。

滿載效率: >98.5%。

功率密度: 超過 700 W/in3。

分析: 這一案例證明,通過極致的磁集成和消除端接損耗,配合寬禁帶器件,99%的效率是可實現的。

5.3 案例三:800V總線CLLC變換器(基于基本半導體技術)

應用場景: 下一代高壓EV充電樁。

核心器件: 基本半導體 B3M011C120Z(1200V, 11mΩ, 銀燒結TO-247-4)。

性能優勢: 1200V耐壓直接適配800V總線,無需串聯器件。11mΩ的超低導通電阻使得在11kW滿載下的導通損耗極低。

效率預估: 結合軟開關設計,該配置在滿載下有望達到 98.2% - 98.6% 的效率。TO-247-4封裝中的開爾文源極(Kelvin Source)消除了源極電感對柵極驅動的負反饋,加快了開關速度,進一步降低了關斷損耗(Eoff?)。

第六章 設計實施指南與推薦參數

為了復現上述高效率,建議遵循以下參數選擇與設計步驟:

6.1 器件選型推薦(基本半導體)

| 應用場景 (Power) | 推薦型號 | 關鍵參數 (@25°C) | 封裝技術 | 推薦理由 |

|---|---|---|---|---|

| 3.3kW - 6.6kW (戶儲電池DC/DC) | B3M040075Z | 750V, 40mΩ | TO-247-4 | 750V耐壓適配400V平臺,40mΩ平衡了導通與開關損耗,適合全橋LLC 。 |

| 充電樁 | B3M011C120Z | 1200V, 11mΩ | TO-247-4 | 銀燒結技術提供超低熱阻(0.15K/W);11mΩ極低電阻應對大電流;1200V適配800V平臺 。 |

| 高密度/高頻 | B3M020120ZN | 1200V, 20mΩ | TO-247-4NL | 無引腳封裝大幅降低寄生電感,適合>300kHz的高頻應用 。 |

6.2 關鍵設計公式與準則

勵磁電感設計上限:

Lm,max?=4?Co(er)??Vin??fsw?tdead,max??n?Vout??×MarginFactor

注:使用Co(er)?而非數據手冊中的單一Coss?值。

死區時間設定下限:

tdead,min?=Im,peak?2?Vin??Co(tr)??

注:必須保證tdead?大于此值以實現ZVS,但不可過大以免體二極管導通。

諧振槽品質因數(Q)選擇:

對于追求最高效率的非寬范圍調壓應用(如DCX),應設計極低的Q值(Q < 0.2),這使得增益曲線平坦,且諧振電流有效值最小,接近負載電流折算值。

PCB布局:

使用開爾文連接驅動SiC MOSFET。

最小化諧振回路的環路面積,減少輻射EMI。

在矩陣變壓器中,采用“交錯并聯”(Interleaving)的繞組布局(P-S-P-S),以利用鄰近效應降低交流電阻(Rac?)。

第七章 結論

SiC MOSFET與LLC諧振變換器的協同設計,本質上是一場對損耗的“圍剿戰”。通過選用如基本半導體B3M系列這樣具備低RDS(on)?、低Coss?和銀燒結工藝的先進SiC器件,我們獲得了物理層面的先發優勢。然而,要將這一優勢轉化為99%的系統效率,必須在電路層面實施深度優化:

精確的電荷管理: 依據SiC非線性電容特性,精確計算勵磁電流,在確保ZVS的同時最小化環流。

極致的時序控制: 采用自適應死區技術,消除SiC體二極管的高壓降導通損耗。

創新的磁路架構: 引入矩陣變壓器和磁集成技術,打破大電流下的磁性元件損耗瓶頸。

隨著800V高壓平臺的普及和SiC成本的進一步優化,這種協同設計方法將成為未來幾年高性能電源轉換器的主流設計范式,推動電力電子行業進入一個高效、高密、高可靠性的新紀元。

審核編輯 黃宇

-

LLC

+關注

關注

38文章

635瀏覽量

80840 -

諧振變換器

+關注

關注

1文章

81瀏覽量

16145 -

SiC MOSFET

+關注

關注

1文章

161瀏覽量

6808

發布評論請先 登錄

SiC MOSFET 米勒平臺震蕩的根源分析與 Layout 優化策略

基于 SiC MOSFET 的高頻 LLC 諧振變換器:針對 AI 負載 0%-200% 瞬態切換的軟開關失效預防與可靠性優化

基于SiC MOSFET的雙向 CLLC 諧振變換器的對稱性設計與增益特性分析

傾佳楊茜-方案實踐:對SiC模塊和單管進行LLC最優參數條件調教

LLC諧振變換器:物理本質、演進歷程與SiC碳化硅技術的深度融合

固態變壓器(SST)高頻DC/DC級中基于半橋SiC模塊的LLC變換器控制策略

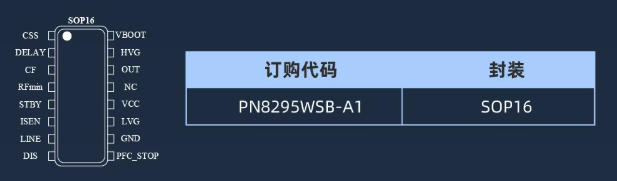

芯朋微工業級電壓控制模式LLC諧振控制器PN8295W解析

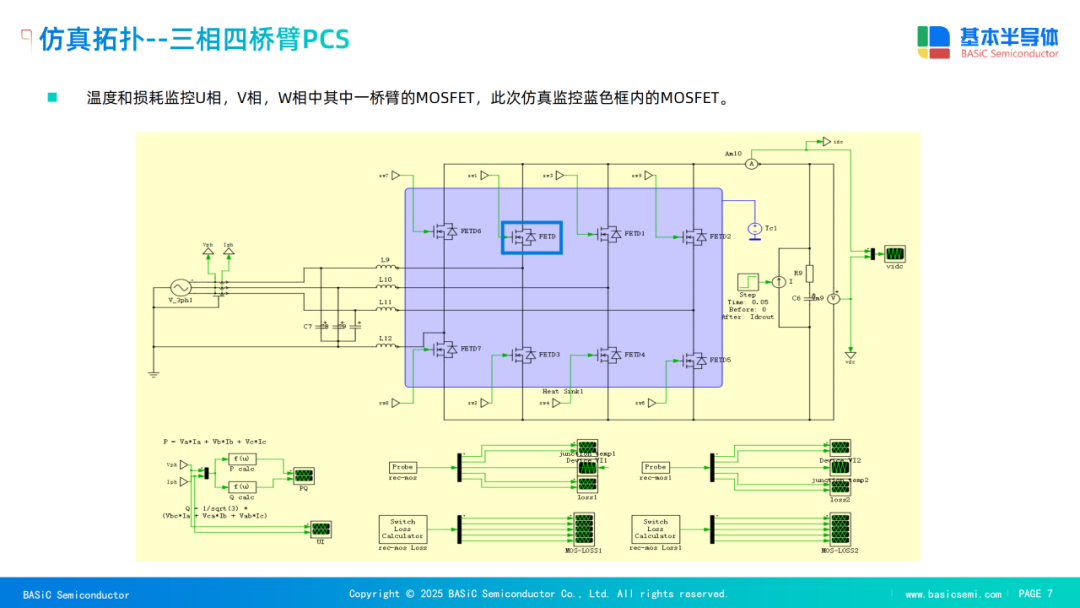

兩款SiC MOSFET模塊在三相四橋臂變換器中的應用優勢分析如下(聚焦工商業儲能PCS場景)

辰達MOSFET在DC-DC變換器中的關鍵作用與優化策略

邁向極致效率:SiC MOSFET與LLC諧振變換器的協同設計與優化

邁向極致效率:SiC MOSFET與LLC諧振變換器的協同設計與優化

評論