解析LMK5C23208A:高性能網絡同步器的卓越之選

在當今無線通信與基礎設施應用領域,對高精度、高性能時鐘解決方案的需求日益增長。LMK5C23208A作為一款領先的網絡同步器,憑借其獨特的特性和強大的功能,為工程師們提供了可靠的選擇。本文將深入剖析LMK5C23208A的各項特性、功能及其應用,為電子工程師在相關設計中提供全面的參考。

文件下載:lmk5c23208a.pdf

特性亮點

超低抖動BAW VCO

LMK5C23208A采用了超低抖動的BAW VCO技術,這使得它在無線基礎設施和以太網時鐘應用中表現卓越。在491.52MHz頻率下,典型RMS抖動僅為40fs,最大RMS抖動為57fs;在245.76MHz頻率下,典型RMS抖動為50fs,最大RMS抖動為62fs。這種超低抖動的特性能夠有效減少信號干擾,提高信號傳輸的準確性和穩定性,適用于對時鐘精度要求極高的應用場景。

雙高性能數字鎖相環與三模擬鎖相環

該設備集成了2個高性能數字鎖相環(DPLL)和3個模擬鎖相環(APLLs),為時鐘信號的處理和同步提供了強大的支持。DPLL的環路濾波器帶寬可編程范圍從1mHz到4kHz,且DCO頻率調整步長小于1ppt,能夠實現高精度的頻率控制。此外,APLL3采用了TI專有的體聲波(BAW)技術,可生成超低抖動的491.52MHz輸出時鐘,不受DPLL參考輸入頻率和抖動特性的影響。

豐富的輸入輸出接口

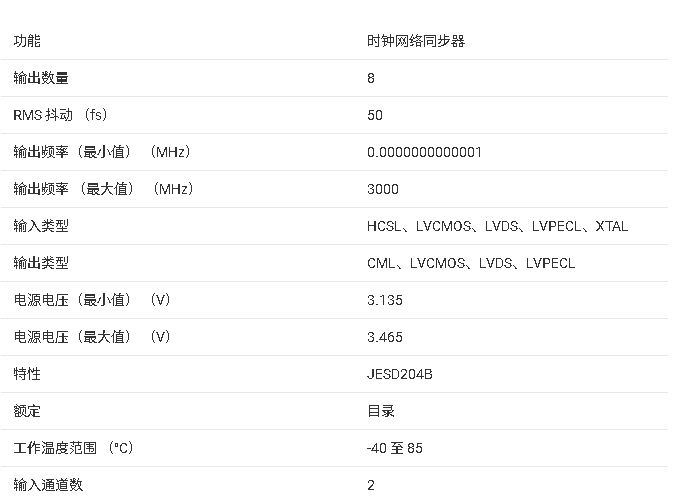

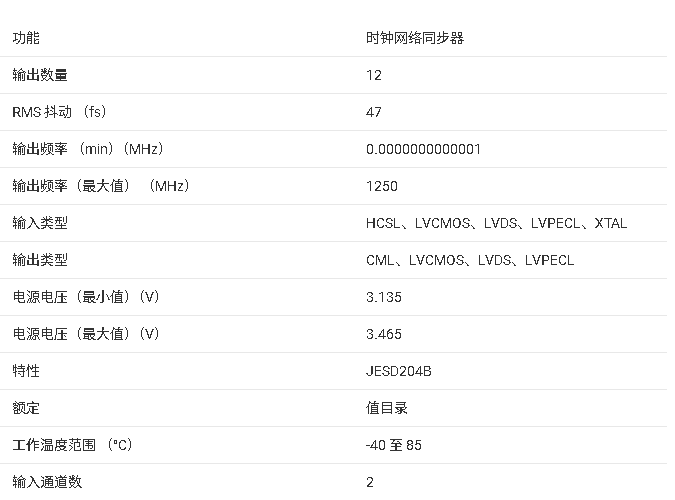

LMK5C23208A具有2個差分或單端DPLL輸入,輸入頻率范圍從1Hz(1PPS)到800MHz,能夠適應多種不同的時鐘信號輸入。同時,它擁有8個差分輸出,輸出格式可編程為HSDS、AC-LVPECL、LVDS和HSCL等,輸出頻率范圍從1Hz(1PPS)到1250MHz,還可配置為多達12個總頻率輸出,滿足了多樣化的應用需求。

功能分析

時鐘輸入與監測

- 振蕩器輸入(XO):XO輸入作為分數N APLL的參考時鐘,其頻率準確性和穩定性直接影響輸出時鐘的性能。對于DPLL功能應用,建議使用TCXO、OCXO或外部可追溯時鐘作為XO輸入,以滿足同步標準的頻率精度和保持穩定性要求。同時,該輸入緩沖器具有可編程的片上終端和交流耦合輸入偏置配置,可根據不同的時鐘接口類型進行靈活調整。

- 參考輸入:參考輸入能夠接受差分或單端時鐘,每個輸入都具備可編程的輸入類型、終端和偏置配置。DPLL輸入復用器可自動或手動選擇參考輸入,支持自動恢復和非恢復模式,以及手動帶自動回退和自動保持模式,確保在不同輸入情況下都能實現穩定的時鐘同步。

- 輸入監測:該設備對時鐘輸入和PLL進行全面監測,包括XO輸入監測、參考輸入監測和PLL鎖定檢測等功能。通過這些監測機制,可以及時發現輸入時鐘的異常情況,如頻率偏差、缺失脈沖等,并采取相應的措施,如自動切換參考輸入或進入保持模式,以保證設備的穩定運行。

鎖相環架構與工作模式

- PLL架構:LMK5C23208A的PLL架構包括一個超低抖動通道(由DPLL3和BAW APLL組成)和兩個可生成低抖動時鐘頻率域的APLL。每個DPLL都有一個參考選擇復用器,可鎖定到另一個VCO域或任何參考輸入;每個APLL也有一個參考選擇復用器,可鎖定到XO輸入或另一個APLL的級聯分頻器輸出。這種靈活的架構設計使得設備能夠在多個時鐘域之間實現精確的頻率和相位控制。

- 工作模式:

- 獨立DPLL操作:在這種模式下,每個DPLL可以獨立選擇參考輸入,不受其他通道的影響。在啟動時,APLL會鎖定到XO輸入并在自由運行模式下工作,當檢測到有效的DPLL參考輸入時,DPLL會開始鎖定操作。為了減少雜散噪聲,建議選擇合適的XO輸入頻率,避免比率接近整數或半整數邊界。

- 級聯DPLL操作:通過級聯DPLL,可提供干凈、低抖動的輸出時鐘,并與主同步DPLL同步。當所有啟用的DPLL和APLL鎖定時,所有啟用的輸出都與主同步DPLL選擇的參考同步。在這種模式下,BAW APLL的鎖定狀態會影響其他級聯DPLL的性能,因此需要密切監測。

- APLL級聯與DPLL配合:將VCBO作為級聯源提供給APLL1或APLL2,可為APLL提供高頻、超低抖動的參考時鐘,改善近端相位噪聲性能。在這種模式下,需要注意DPLL3的鎖定狀態對其他APLL的影響,以及在DPLL禁用時選擇合適的分母以消除頻率誤差。

- APLL-only模式:在該模式下,外部XO輸入源決定了輸出時鐘的自由運行頻率穩定性和準確性,DPLL塊不參與工作。APLL可以在級聯模式或獨立模式下運行,通過控制寄存器可對每個APLL進行DCO調整。為了合成精確的頻率比并保持0ppm頻率誤差,建議在該模式下選擇可編程的24位分母。

輸出時鐘與控制

- 輸出時鐘分布:輸出分頻器支持輸出同步(SYNC)功能,可實現兩個或多個輸出通道的相位同步。同時,還具備可選的內部ZDM同步功能,支持確定性的輸入到輸出相位對齊,通常用于1PPS時鐘。

- 輸出源復用器:設備采用了6個輸出源復用器,將頻率源分配到各個輸出組。不同的輸出組具有不同的復用器選擇選項,用戶可以根據需求靈活配置輸出時鐘源,以減少串擾和滿足不同的應用要求。

- 輸出分頻器:每個輸出源復用器后面都有一個或多個輸出分頻器,用于生成最終的時鐘輸出頻率。不同的輸出通道具有不同的分頻器配置,如OUT3和OUT15通道有一個12位的通道分頻器,而其他一些通道還可級聯一個20位的SYSREF分頻器,以實現更低的時鐘頻率輸出。

- 輸出延遲控制:LMK5C23208A具備輸出時鐘相位調整功能,通過可編程的靜態偏移數字延遲和可選的模擬延遲,可對輸出時鐘的相位進行精確調整,以滿足不同應用對時鐘相位的要求。

- 輸出時鐘驅動器:每個時鐘輸出可以獨立配置為差分輸出驅動器,OUT0或OUT1還可額外配置為兩個1.8V或2.65V的LVCMOS輸出驅動器。差分輸出驅動器具有可編程的單端峰 - 峰值幅度和共模電壓設置,可根據不同的接收機要求進行調整。同時,每個輸出通道都有一個專用的內部LDO穩壓器,可提供良好的PSNR,降低電源噪聲對輸出時鐘的影響。

其他功能

- 無擾動切換:DPLL支持無擾動切換功能,通過TI專有的相位抵消方案和可選的相位 slew 控制方案,可在切換參考輸入時避免相位瞬變對輸出的影響。在切換頻率鎖定的參考輸入時,相位抵消功能可防止相位瞬變立即傳播到輸出,而相位 slew 控制功能則可在切換過程中限制輸出相位瞬變的幅度,確保輸出平滑過渡到新的頻率。

- 時間流逝計數器(TEC):TEC允許用戶精確測量兩個或多個事件之間的時間間隔,事件可以是GPIO引腳的上升或下降沿,也可以是SPI SCS引腳的下降沿。通過選擇不同的PLL作為時鐘源,可在高精度測量和較長的溢出時間之間進行權衡。該計數器的精度優于7.5ns,且總測量時間可超過59分鐘。

應用場景

LMK5C23208A廣泛應用于多個領域,包括:

無線通信網絡

在4G和5G無線網絡中,如有源天線系統(AAS)、大規模多輸入多輸出(mMIMO)、宏遠程無線電單元(RRU)以及CPRI/eCPRI基帶、集中式和分布式單元(BBU、CU、DU)等應用中,該設備能夠提供高精度的時鐘同步和低抖動的時鐘信號,確保通信系統的穩定運行。

小基站系統

小基站系統對時鐘的精度和穩定性要求較高,LMK5C23208A的高性能特性使其成為小基站解決方案的理想選擇,可有效提高小基站的信號質量和通信性能。

同步以太網和光傳輸網絡

在SyncE(G.8262)、SONET/SDH(Stratum 3/3E、G.813、GR-1244、GR-253)以及IEEE-1588 PTP從時鐘等應用中,該設備能夠滿足同步標準的要求,實現精確的時鐘同步和抖動清除功能,保證數據傳輸的準確性和可靠性。

測試與測量

在測試和測量設備中,對時鐘信號的精度和穩定性要求極為嚴格。LMK5C23208A的超低抖動和高精度頻率控制特性,使其能夠為測試和測量設備提供穩定、準確的時鐘源,確保測試結果的準確性。

設計與應用建議

電源設計

- 電源旁路:為了降低電源噪聲對設備性能的影響,建議在PCB上合理放置電源旁路電容。可將電容安裝在PCB的背面或元件面,保持電容與設備電源引腳之間的連接盡可能短,并通過低阻抗連接將電容的另一端接地。

- 電源軌排序和斜坡速率:在電源設計中,需要注意電源軌的排序和斜坡速率。對于單電源軌供電,確保所有VDD和VDDO電源在單調上升且滿足一定時間要求的情況下,可無需在PD#引腳添加電容來延遲設備上電。對于分離電源軌供電,建議在所有電源都上升到3.135V以上后再開始PLL校準,可通過在PD#引腳連接電容或由系統主機驅動PD#引腳來延遲設備上電。對于非單調或慢速的電源上升情況,同樣需要延遲VCO校準,可采用上述方法或在所有核心電源上升后進行設備軟復位來觸發VCO校準。

布局設計

- 信號隔離:在PCB布局中,應將輸入、XO/OCXO/TCXO和輸出時鐘與相鄰的不同頻率時鐘和其他動態信號隔離開來,以減少信號干擾。

- 阻抗匹配:避免時鐘和動態邏輯信號的受控阻抗50Ω單端(或100Ω差分)跡線上出現阻抗不連續的情況,確保信號傳輸的穩定性。

- 電容放置:將旁路電容靠近VDD和VDDO引腳放置在IC同一側或PCB另一側的正下方,較大的去耦電容可放置在稍遠的位置。同時,將外部電容靠近CAP_x和LFx引腳放置。

- 接地設計:使用多個過孔將寬電源跡線連接到相應的電源島或平面,使用至少6×6的通孔過孔圖案將IC接地/散熱墊連接到PCB接地平面,以提高散熱性能和電氣性能。

編程與配置

- 寄存器編程:在使用系統主機通過I2C或SPI對設備進行初始配置時,可按照以下一般步驟進行:首先對設備供電并進入相應通信模式;將所有輸出設置為靜態低電平以避免啟動時出現毛刺;寫入除特定寄存器外的所有寄存器;進行全局、DPLL和APLL軟件復位;等待APLL鎖定后再進行SYNC操作;修改輸出寄存器以設置所需的輸出狀態;最后可選擇清除中斷狀態標志。

- EEPROM編程:可通過三種方法對SRAM進行編程,進而實現EEPROM的編程。寄存器提交方法適用于大多數應用,可自動將活動寄存器映射到SRAM;直接寫入方法適用于在系統中編程EEPROM,可在不中斷設備正常運行的情況下修改SRAM和EEPROM;混合方法適用于只修改SRAM中特定字段的情況。

總結

LMK5C23208A作為一款高性能的網絡同步器和抖動清除器,憑借其超低抖動的BAW VCO技術、靈活的PLL架構、豐富的輸入輸出接口以及強大的功能特性,為無線通信和基礎設施應用提供了可靠的時鐘解決方案。在設計應用過程中,工程師們需要充分考慮電源設計、布局設計和編程配置等方面的因素,以確保設備能夠發揮出最佳性能。相信隨著技術的不斷發展,LMK5C23208A將在更多領域得到廣泛應用,為電子工程師們帶來更多的便利和創新空間。大家在實際應用中遇到過哪些與時鐘同步相關的挑戰呢?又是如何解決的呢?歡迎在評論區分享交流。

-

網絡同步器

+關注

關注

0文章

35瀏覽量

2837

發布評論請先 登錄

解析LMK5C23208A:高性能網絡同步器的卓越之選

解析LMK5C23208A:高性能網絡同步器的卓越之選

評論