DP83848x:高性能單端口以太網收發器的設計與應用

在嵌入式系統的設計中,以太網收發器是實現網絡通信的關鍵組件之一。今天,我們要深入探討的是德州儀器(TI)的DP83848x系列單端口10/100 MB/s以太網收發器,它在性能、可靠性和小型化方面都有著出色的表現,非常適合對空間要求敏感的應用場景。

文件下載:dp83848t.pdf

1. 器件概述

1.1 特性亮點

DP83848x采用低功耗3.3 - V、0.18 - μm CMOS技術,具備多種令人矚目的特性。它支持10/100 Mb/s的Auto - MDIX功能,能自動識別網線類型,無需手動切換交叉線和直連線,大大簡化了布線過程。同時,其能量檢測模式可以在無數據活動時進入低功耗狀態,有效降低能耗。

該器件擁有3.3 - V的MAC接口,支持RMII Rev. 1.2接口(可配置)和MII接口,還配備了MII串行管理接口(MDC和MDIO),方便進行設備管理和配置。此外,它支持IEEE 802.3自動協商和并行檢測,能夠自動選擇最佳的通信模式,確保高效穩定的通信。

在物理層方面,DP83848x集成了符合ANSI X3.263標準的TP - PMD,具備自適應均衡和基線漂移補償功能,能在超過137米的網線長度上實現無差錯運行。同時,它還提供了大于4 kV人體模型的ESD保護,保證了設備的可靠性和穩定性。部分型號(DP83848J/K)還支持可配置的LED指示燈,用于顯示鏈路和活動狀態,方便調試和監控。

1.2 應用場景廣泛

DP83848x的應用場景十分廣泛,涵蓋了外圍設備、移動設備、工廠和樓宇自動化以及基站等領域。在這些場景中,它的高性能和可靠性能夠滿足不同應用的需求,為設備之間的通信提供穩定的保障。

1.3 詳細描述

DP83848x專為嵌入式系統中對空間敏感的應用而設計,不僅滿足了對質量和可靠性的要求,還具備小巧的外形尺寸。它的性能遠遠超過了IEEE標準,在超過137米的Cat - V電纜上仍能保持卓越的互操作性和行業領先的性能。

DP83848J/K型號提供了兩個靈活的LED指示燈,分別用于顯示鏈路和速度,方便用戶直觀了解設備的工作狀態。同時,該器件支持MII和RMII接口,為設計帶來了更大的靈活性和便利性。而DP83848H/M/T型號則集成了25 - MHz時鐘輸出,無需額外的時鐘源組件,節省了空間和成本。

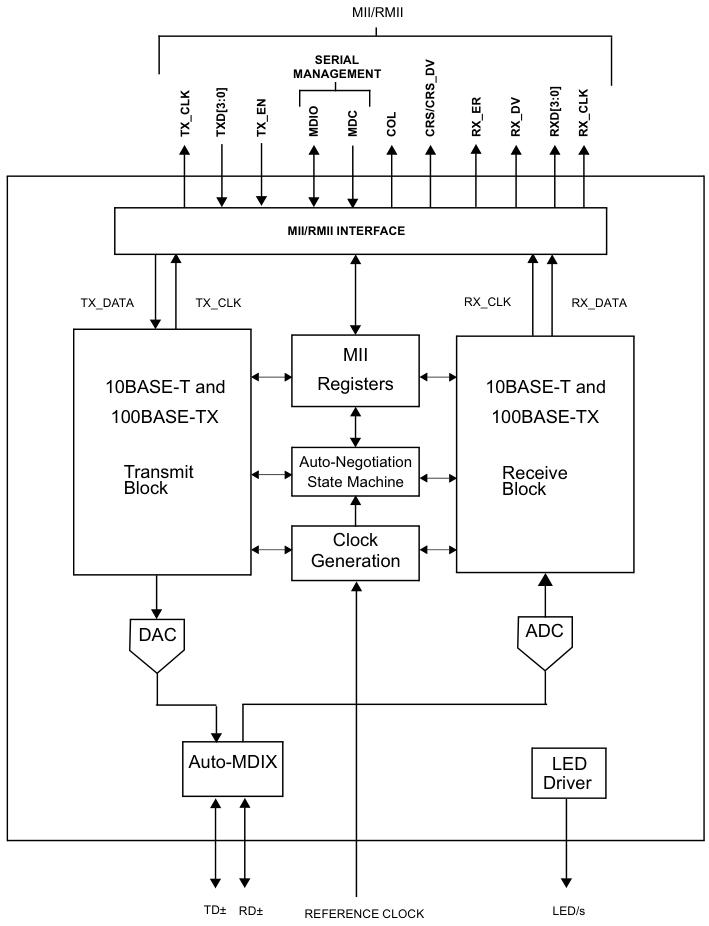

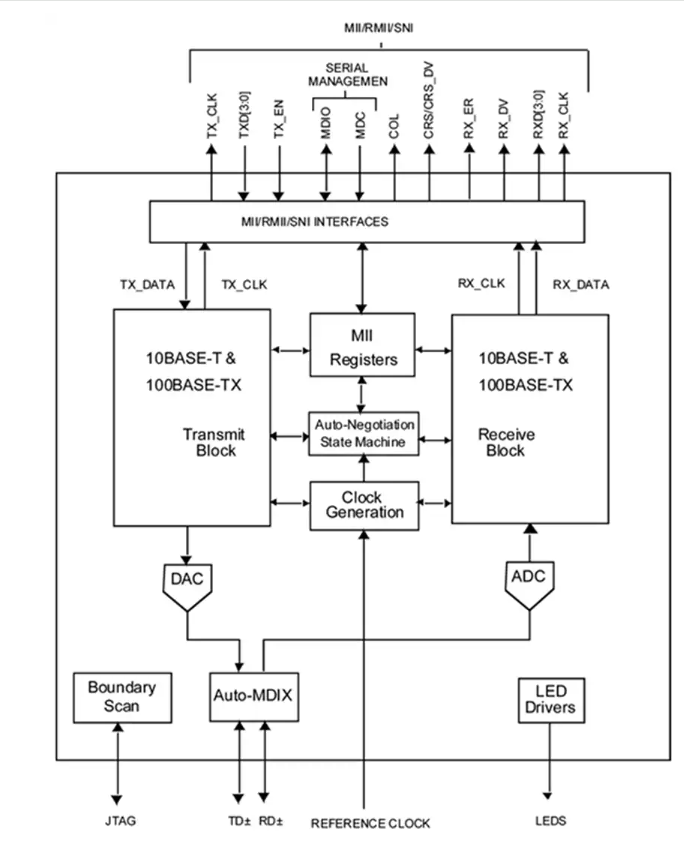

1.4 功能框圖

通過功能框圖,我們可以更清晰地了解DP83848x的內部結構和工作原理,為后續的設計和調試提供參考。

通過功能框圖,我們可以更清晰地了解DP83848x的內部結構和工作原理,為后續的設計和調試提供參考。

2. 器件對比

| 不同型號的DP83848x在溫度范圍上有所差異,以滿足不同應用場景的需求。 | 器件型號 | 溫度范圍 | 溫度等級 |

|---|---|---|---|

| DP83848J/M | 0℃ - 70℃ | 商用級 | |

| DP83848K/T | - 40℃ - 85℃ | 工業級 | |

| DP83848H | - 40℃ - 125℃ | 極端溫度級 |

在選擇器件時,我們需要根據實際應用場景的溫度要求來選擇合適的型號,以確保設備的穩定運行。

3. 引腳配置與功能

DP83848x的引腳分為多個接口類別,包括串行管理接口、MAC數據接口、時鐘接口、LED接口、復位、 strap選項、10/100 Mb/s PMD接口、特殊連接和電源引腳等。下面我們來詳細了解一下各個接口的功能。

3.1 串行管理接口

該接口通過MDC和MDIO引腳實現,MDC為管理數據時鐘,最大時鐘速率為25 MHz,無最小速率要求;MDIO為雙向管理指令/數據信號,需要一個1.5 kΩ的上拉電阻。通過這個接口,我們可以對設備進行配置和管理。

3.2 MAC數據接口

MAC數據接口包括多個信號引腳,如COL(碰撞檢測)、CRS/CRS_DV(載波檢測)、RX_CLK(接收時鐘)等。在不同的工作模式下,這些信號的功能和作用也有所不同。例如,在半雙工模式下,COL信號用于檢測碰撞;而在全雙工模式下,該信號始終為邏輯0。

3.3 時鐘接口

時鐘接口通過X1和X2引腳實現,X1為主要的時鐘參考輸入,支持外部晶體諧振器或外部CMOS級振蕩器源;X2為晶體輸出引腳,當使用外部CMOS振蕩器時鐘源時,該引腳應保持未連接狀態。

3.4 LED接口

DP83848J/K型號支持可配置的LED指示燈,通過LED_LINK和LED_SPEED引腳實現。LED_LINK用于顯示鏈路狀態,LED_SPEED用于顯示數據速率。這些指示燈的狀態可以根據實際需求進行配置,方便調試和監控。

3.5 復位

通過RESET_N引腳實現硬件復位,將該引腳拉低至少1 μs,可使設備復位,所有內部寄存器將重新初始化為默認狀態,strap選項也將重新初始化。此外,還可以通過軟件設置基本模式控制寄存器(BMCR)的復位位來實現軟件復位。

3.6 Strap選項

DP83848x使用多個功能引腳作為strap選項,這些引腳的值在復位時被采樣,并用于將設備設置為特定的工作模式。例如,PHY地址輸入引腳(PHYAD[4:0])可以設置設備的PHY地址,從而實現多設備的管理和通信。

4. 規格參數

4.1 絕對最大額定值

在使用DP83848x時,需要注意其絕對最大額定值,如電源電壓范圍為 - 0.5 V - 4.2 V,最大結溫為150℃等。超過這些額定值可能會導致設備永久性損壞,因此在設計時必須嚴格遵守。

4.2 ESD額定值

該器件具有良好的ESD保護性能,人體模型(HBM)的ESD額定值為 + 4000 V,帶電設備模型(CDM)的ESD額定值為 + 1000 V,能夠有效防止靜電對設備造成損壞。

4.3 推薦工作條件

推薦的電源電壓為3.3 V ± 0.3 V,不同型號的環境溫度范圍也有所不同。在設計時,應確保設備在推薦的工作條件下運行,以保證其性能和可靠性。

4.4 熱信息

了解設備的熱信息對于散熱設計非常重要。DP83848x的熱阻參數包括結到環境熱阻(RθJA)、結到外殼熱阻(RθJC)等,這些參數可以幫助我們合理設計散熱方案,確保設備在高溫環境下也能穩定工作。

4.5 DC和AC規格

DC規格包括輸入高電壓、輸入低電壓、輸出高電壓、輸出低電壓等參數;AC規格包括各種時序要求,如MII串行管理時序、100 Mb/s MII傳輸時序等。在設計電路時,需要根據這些規格參數來選擇合適的元器件和設計合理的時序。

5. 詳細描述

5.1 功能模塊

DP83848x的功能模塊包括100BASE - TX發射器、100BASE - TX接收器和10BASE - T收發器模塊。每個模塊都由多個功能塊組成,實現了數據的編碼、解碼、傳輸和接收等功能。

5.2 可配置特性

該器件具有多種可配置特性,如自動協商、Auto - MDIX、LED接口、內部回環和BIST等。下面我們來詳細了解一下這些特性。

5.2.1 自動協商

自動協商功能允許設備在連接時自動選擇最佳的通信模式,通過快速鏈路脈沖(FLP)突發信號來交換配置信息。DP83848x支持四種不同的以太網協議(10 Mb/s半雙工、10 Mb/s全雙工、100 Mb/s半雙工和100 Mb/s全雙工),確保了在不同鏈路伙伴之間能夠選擇最高性能的協議。

5.2.2 Auto - MDIX

該功能使用自動協商來確定數據傳輸和接收的正確配置,并選擇合適的MDI對進行MDI/MDIX操作。默認情況下,Auto - MDIX功能是啟用的,也可以通過strap或PHYCR寄存器進行配置。

5.2.3 LED接口

DP83848J/K型號的LED接口支持可配置的指示燈,用于顯示鏈路和速度狀態。在不同的模式下,LED的顯示方式也有所不同,方便用戶直觀了解設備的工作狀態。

5.2.4 內部回環

通過設置基本模式控制寄存器(BMCR)的回環位,可以啟用內部回環功能,將MII傳輸數據路由到MII接收輸出,方便進行系統診斷。

5.2.5 BIST

DP83848x集成了內置自測試(BIST)電路,可用于測試發送和接收數據路徑的完整性。用戶可以選擇9位或15位的偽隨機序列進行測試,測試結果存儲在PHYCR寄存器的BIST狀態位中。

5.3 工作模式

DP83848x支持MII和RMII兩種工作模式,可通過strap選項或寄存器控制進行選擇。RMII模式需要連接一個50 - MHz的振蕩器到X1引腳,并且支持可編程的彈性緩沖區,以容忍參考時鐘和恢復時鐘之間的頻率差異。

5.4 編程

了解DP83848x的編程架構對于實現其功能至關重要。每個收發器模塊(100BASE - TX和10BASE - T)都由多個功能塊組成,如100BASE - TX發射器包括代碼組編碼和注入塊、擾碼器塊、NRZ到NRZI編碼器和二進制到MLT - 3轉換器等。通過對這些功能塊的配置和控制,可以實現數據的正確傳輸和接收。

5.5 存儲器

DP83848x的寄存器塊包含多個寄存器,用于配置和監控設備的工作狀態。例如,基本模式控制寄存器(BMCR)用于控制設備的復位、回環、速度選擇、自動協商等功能;基本模式狀態寄存器(BMSR)用于顯示設備的能力和狀態信息。在編程時,我們需要根據實際需求對這些寄存器進行讀寫操作。

6. 應用、實現與布局

6.1 應用信息

在使用DP83848x進行以太網應用時,需要滿足一定的設計要求,如電源電壓為3.3 V,時鐘輸入為25 MHz(MII模式)或50 MHz(RMII模式)等。同時,還需要選擇合適的元器件,如變壓器、晶體振蕩器、磁珠等,以確保設備的性能和穩定性。

6.2 典型應用

典型應用電路包括TPI網絡電路、時鐘輸入電路、電源反饋電路和磁珠電路等。在設計這些電路時,需要注意元器件的選擇和布局,以減少噪聲干擾和提高信號質量。

6.3 布局指南

PCB布局對于DP83848x的性能有著重要影響。在布局時,應遵循以下原則:

- 避免信號路徑上出現過孔和交叉,減少阻抗不連續性和信號干擾。

- 保持差分信號對的長度匹配,減少延遲差異和共模噪聲。

- 避免信號在磁珠下方布線,防止產生不必要的噪聲串擾。

- 采用至少4層的PCB設計,提供良好的信號完整性和電源穩定性。

6.4 電源供應建議

為了確保設備的穩定運行,建議在電源引腳處使用低阻抗的0.1 - μF表面貼裝電容進行旁路,以減少EMI干擾。同時,PCB應至少有一個實心接地平面和一個實心電源平面,為設備提供低阻抗的電源和返回路徑。

7. 設備與文檔支持

7.1 相關文檔

TI提供了豐富的相關文檔,如AN - 1405 DP83848單10/100 Mb/s以太網收發器RMII模式應用報告、AN - 1540以太網物理層產品的功率測量等,這些文檔可以幫助我們更好地了解和使用DP83848x。

7.2 相關鏈接

通過相關鏈接,我們可以快速訪問技術文檔、支持和社區資源、工具和軟件等,獲取更多的技術支持和幫助。

總結

DP83848x系列以太網收發器以其高性能、可靠性和靈活性,為嵌入式系統的以太網通信提供了優秀的解決方案。在設計過程中,我們需要深入了解其特性、規格參數和應用要求,合理選擇元器件和進行PCB布局,以確保設備的穩定運行和良好性能。希望本文能夠為電子工程師們在使用DP83848x時提供一些參考和幫助。

大家在使用DP83848x的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

嵌入式系統

+關注

關注

41文章

3747瀏覽量

133621 -

以太網收發器

+關注

關注

1文章

33瀏覽量

10556

發布評論請先 登錄

DP83848-HT:高性能以太網PHY的技術剖析與設計指南

DP83847 DsPHYTER II:單10/100以太網收發器的全面解析

DP83848C/I/VYB/YB:高效能以太網PHY的卓越之選

DP83848C/I/VYB/YB:高性能 10/100 Mb/s 以太網物理層收發器深度解析

DP83848C/I/VYB/YB:高性能10/100 Mb/s以太網物理層收發器深度解析

深入剖析DP83848x:高性能10/100 MB/s以太網收發器的卓越之選

DP83848x以太網收發器:特性、設計與應用全解析

深入剖析DP83849C:雙端口10/100 Mb/s以太網物理層收發器的卓越之選

DP83848x以太網收發器:小身材大能量

DP83848x系列以太網收發器:技術解析與設計指南

DP83848C/I/VYB/YB:高性能10/100 Mb/s以太網物理層收發器的深度解析

DP83848Q-Q1:高性能10/100-Mbps以太網物理層收發器解析

DP83848-EP:高性能10/100 Mbps以太網PHY的全面解析

DP83848-HT:適用于嚴苛環境的以太網物理層收發器

Texas Instruments DP83848x 10/100Mb/s以太網PHY數據手冊

DP83848x:高性能單端口以太網收發器的設計與應用

DP83848x:高性能單端口以太網收發器的設計與應用

評論