RZ/T2H

本文闡述了RZ/T2H的PCIe外設作為EP,在Windows上做驅動開發、速率測試時,可能會遇到無法被Windows識別的問題。本文總結了一些調試方法和技巧,來排查問題原因和解決方法。

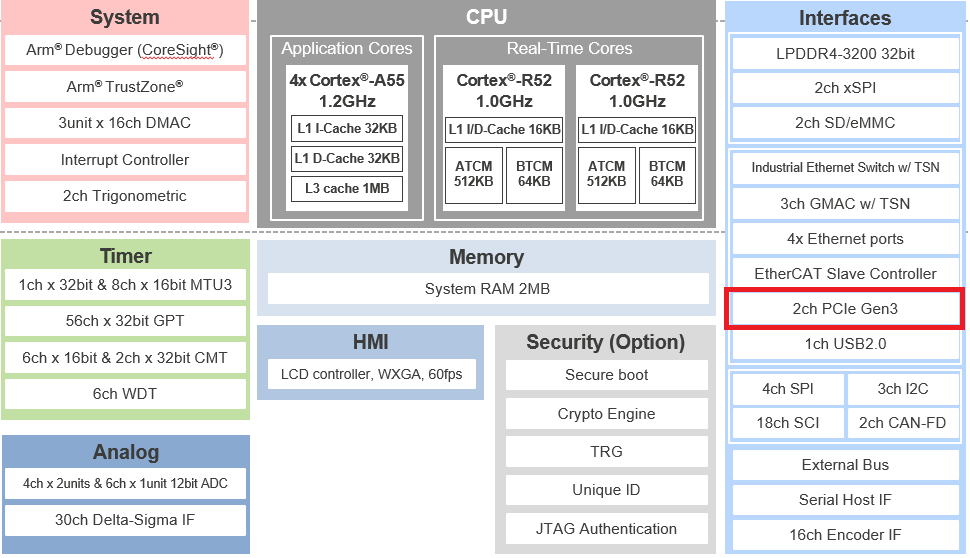

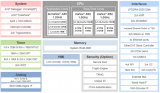

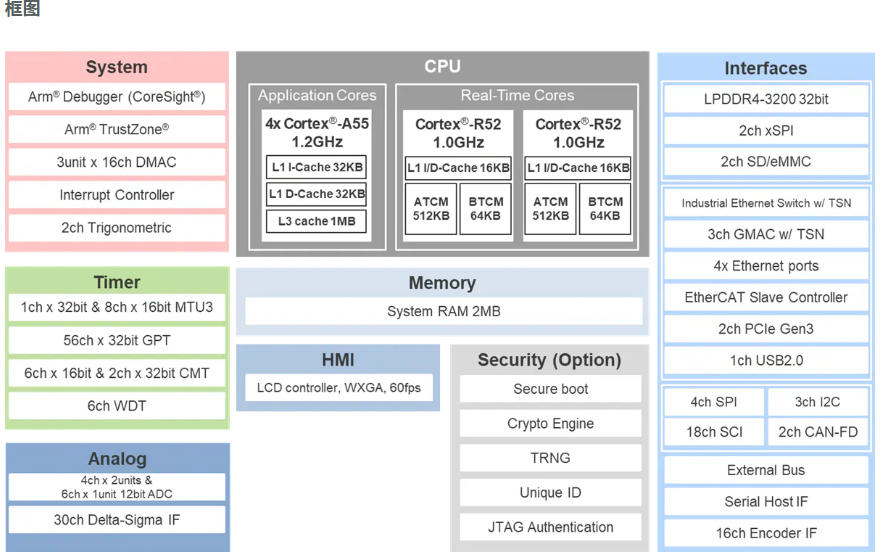

如下圖所示,RZ/T2H有著豐富的外設資源。

圖1:RZ/T2H系統框圖

如紅色方框部分,RZ/T2H有兩路第三代PCIe接口,可以支持到最高8.0 GT/s的傳輸速率。物理連接可以是x1,x2的方式,并且2路接口可以獨立作為RC和EP使用。

在某驅控一體項目中,客戶是將其中1路PCIe作為EP,采用X1配置;Windows PC作為RC,通過PCIe實現快速通信。我們在Windows端基于Windows Driver Framework開發了相關驅動程序。

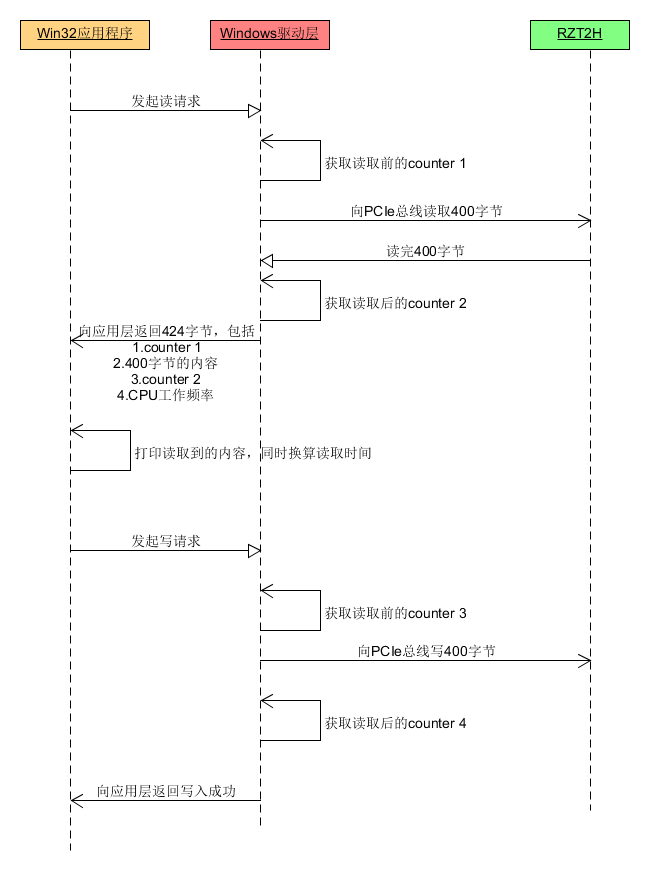

考慮到Windows是非實時性操作系統,所以將所有與PCIe交互的代碼放在了驅動層,以提高通信的實時性。經過測試,Windows PC做RC,RZ/T2H做EP,RC讀取數據的傳輸速率是:33 Bytes/us(考慮到Windows是非實時操作系統,達不到8GT/s的傳輸速率也屬正常)。如果T2H EVK 用作RC端,則速率可以達到PCIe3.0的標準。

PCIe3.0的標準是8.0GT/s的傳輸速率,根據128b/130b的編碼規則,其數據有效率為 128/130=98.46%,從而可以得到有效數據速率為8.0×0.9846=7.877Gbit/s≈0.985GB/s per lane,即985 bytes/us。

T2H默認的MPS(Max Payload Size)最大可以配置成4096B。考慮到加入TLP的header(假如3WD,12B,且MPS配置為256B),則其傳輸有效數據量為(RC連續發 MRd)。

1每us能傳輸的完整completion次數為:985/(256+12)≈3.67次

2對應的有效數據量≈3.67×256≈939B/μs

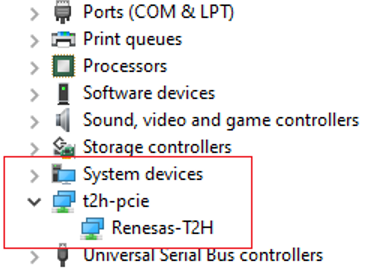

圖2:RZ/T2H驅動程序

圖3:Windows端測量PCIe讀寫速率的消息序列圖

客戶主板設計上通過PCIe金手指與PC主板的PCIe x1接口相接。遇到的問題是:客戶主板燒錄程序,連接到PC,無法被PC識別。

由于沒有高速示波器來分析PCIe總線上的異常,我們只能從以下幾個角度來分析。

1檢查電源是否合理。

依次檢查了5V,3.3V,1.8V,0.8V,均正常。

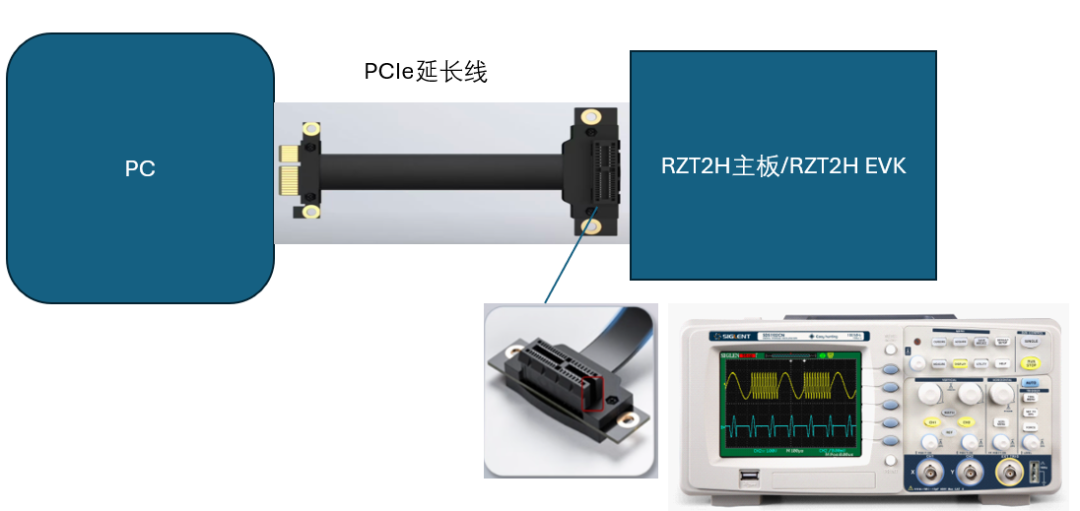

2由于只有500M的示波器,只能抓啟動的波形。通過RZ/T2H EVK的波形與客戶板子的波形作對比。

圖4:加PCIe延長線,便于抓取必要波形

我們通過PCIe的啟動過程了解到,在鏈路還沒有訓練(LTSSM還沒進入L0正常工作狀態)時,允許設備通知對方自己的存在。這種通知被定義為Beacon,它是一種低速、低頻的物理信號,并不是 PCIe 8b/10b或128b/130b編碼的數據流。

鑒于此,我們采用500M的示波器,將TX+(B14),TX-(B15)通過PCIe的延長線接頭處,引到示波器上。C1為TX+,C2為TX-。

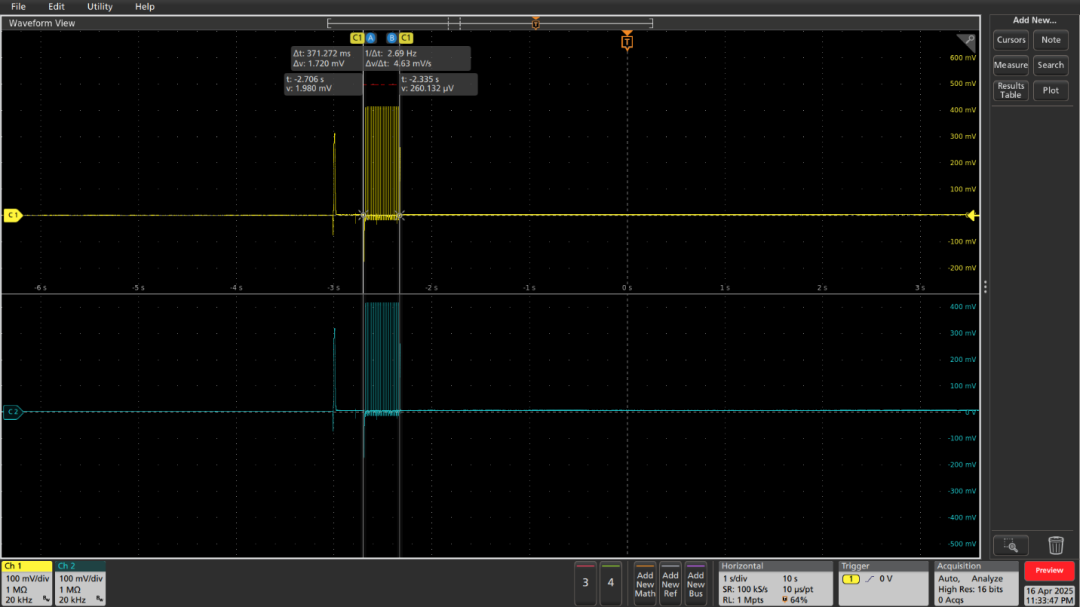

圖5:RZ/T2H EVK Beacon

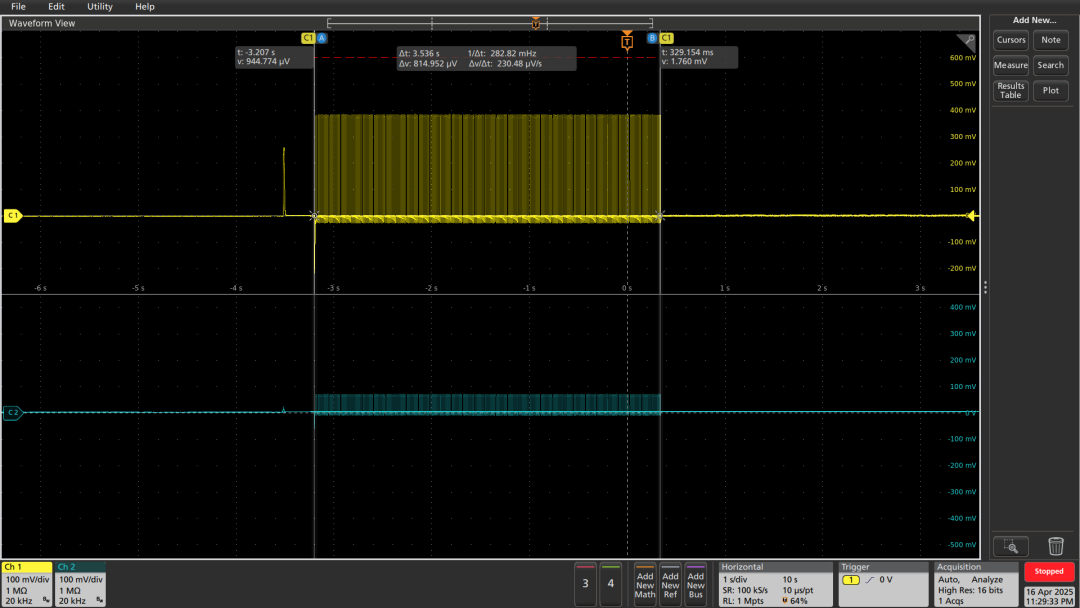

圖6:客戶RZ/T2H主板Beacon

從圖五和圖六可以看到:

RZ/T2H EVK的Beacon持續時間是370ms,TX+和TX-的幅值在400mV左右,且非常對稱。

客戶RZ/T2H主板的Beacon持續時間是3.5s,猜想該Beacon持續時間太久的原因是一直沒有得到EP的應答。且TX+的幅值在400mV左右,而TX-的幅值不到100mV,不對稱。

TX+/TX-是從RC端發起的信號,為何在金手指端的波形發生不對稱現象?于是我們再仔細核對了客戶的PCB,發現客戶的第6,7層沒有鋪地。

由于客戶的電路與EVK有局部的不同,為了防止我們判斷錯誤,將RZ/T2H EVK修改成和客戶板相同的配置(電阻值以及對應信號懸空等),開發板都能正常啟動PCIe,所以基本可以認為是PCB鋪地原因導致的差分信號不均衡,從而RZ/T2H作為EP時沒有正確收到PC的握手信號,而不響應RC,所以沒有下一步動作。

經過客戶重新布板,該主板可以進行正常的PCIe通信了。

從這次debug可以看出,PCIe參考地有非常重要的意義。如果PCIe信號線在沒有參考地平面的情況下布線,將會導致諸如以下問題:

1阻抗不連續與嚴重反射:阻抗在整個走線上劇烈波動,導致信號在每一個阻抗變化點都會發生反射。這會嚴重劣化信號質量。若地平面斷裂/跨分割會導致局部阻抗突變,反射增大,可能引起鏈路訓練失敗。

2信號完整性(SI)問題:

眼圖塌陷:在接收端看到的眼圖會非常“瘦”,甚至完全閉合,眼高和眼寬都不達標。

振鈴(Ringing)和過沖(Overshoot)/下沖(Undershoot):由于阻抗失配和反射,信號會產生嚴重的振蕩。

時序錯誤:邊沿變得緩慢且不確定,建立時間和保持時間無法滿足。

3電磁干擾(EMI)問題:缺少參考平面,信號產生的電磁場無法被有效屏蔽和約束,會向外輻射,導致EMI測試失敗,也可能干擾板上的其他電路。

4系統不穩定與高誤碼率:最終結果是PCIe鏈路訓練失敗、速率協商不上去、或者在運行中出現大量的數據錯誤(誤碼率BER飆升),導致系統頻繁藍屏、卡頓、設備無法識別。

對于PCIe 3.0及以上速率,layout要求較為苛刻, PCB設計者需要足夠重視,沒有完整的參考地平面,項目失敗的風險極高,也會為后期帶來不必要的debug工作。PCB一定要遵守RZ/T2H的硬件設計指導書。

-

通信

+關注

關注

18文章

6304瀏覽量

139475 -

WINDOWS

+關注

關注

4文章

3668瀏覽量

93132 -

瑞薩

+關注

關注

36文章

22426瀏覽量

89623 -

PCIe

+關注

關注

16文章

1416瀏覽量

87437

原文標題:從小白到精通調試瑞薩RZ/T2H PCIe通信

文章出處:【微信號:瑞薩嵌入式小百科,微信公眾號:瑞薩嵌入式小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RZ T2H PCIe裸機程序開發和Linux下的配置介紹

【米爾瑞薩RZ/G2L開發板-試用體驗】認識一下米爾瑞薩RZ/G2L開發板的核心板

瑞薩電子推出面向高性能機器人應用的RZ/V2H微處理器

工業MPU新標桿,多協議工業以太網+運動控制 - 瑞薩RZ/T2H 新產品

瑞薩電子量產高性能工業設備MPU RZ/T2H

瑞薩交流日進行中,米爾演講-RZ/T2H高性能模組賦能工業產品創新

RZ/T2H MPU數據手冊和產品介紹#集成了強大的應用處理能力和精確的實時控制功能

瑞薩RZ/T2H PCIe通信的調試方法

瑞薩RZ/T2H PCIe通信的調試方法

評論