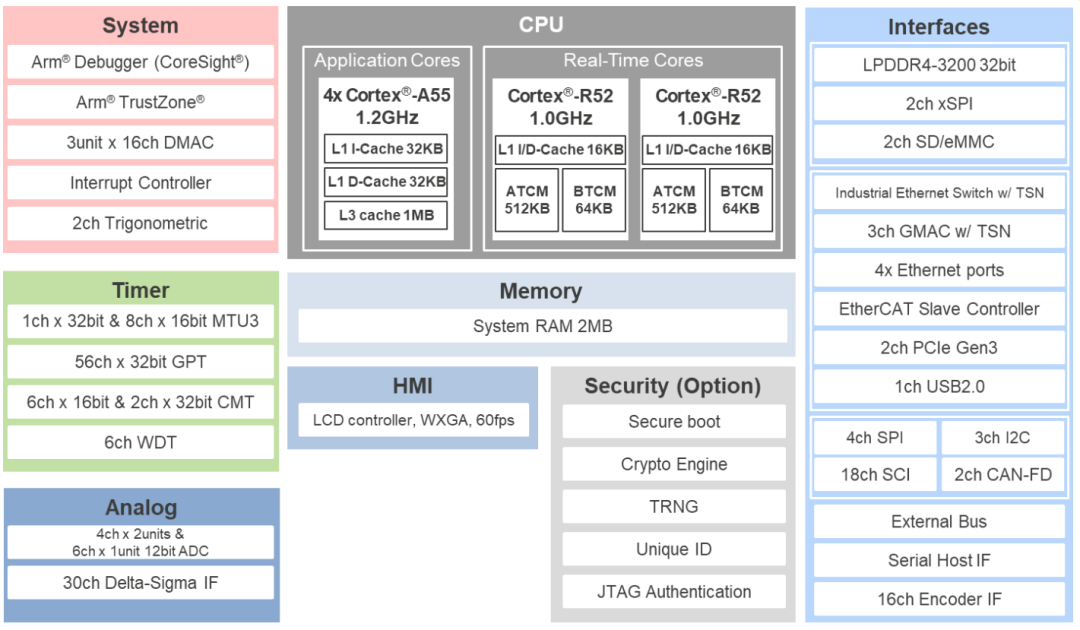

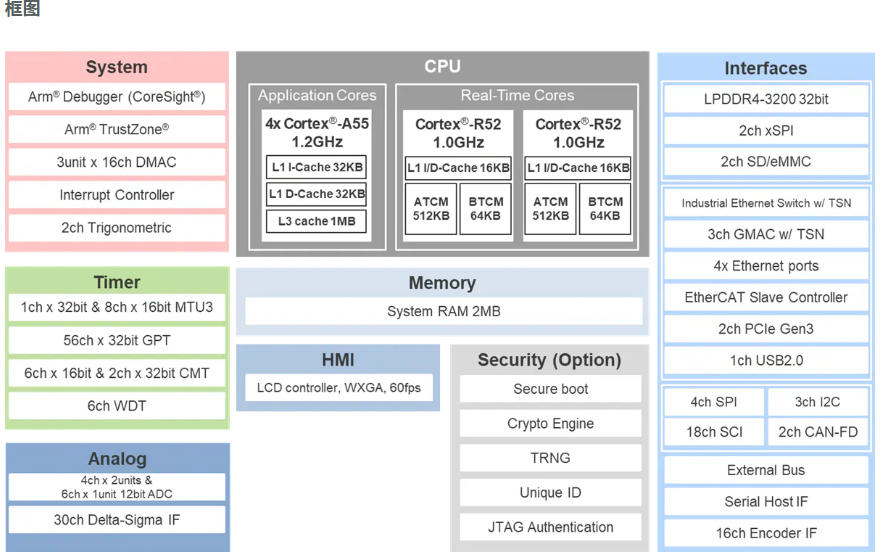

瑞薩RZ T2H是由2個(gè)R52核和4個(gè)A55核構(gòu)成。支持LPDDR4,其傳輸可以達(dá)到3.2Gbps(1600 MHZ),總線寬度為32位,兩個(gè)rank,最大支持64Gb容量。

圖RZ T2H框圖

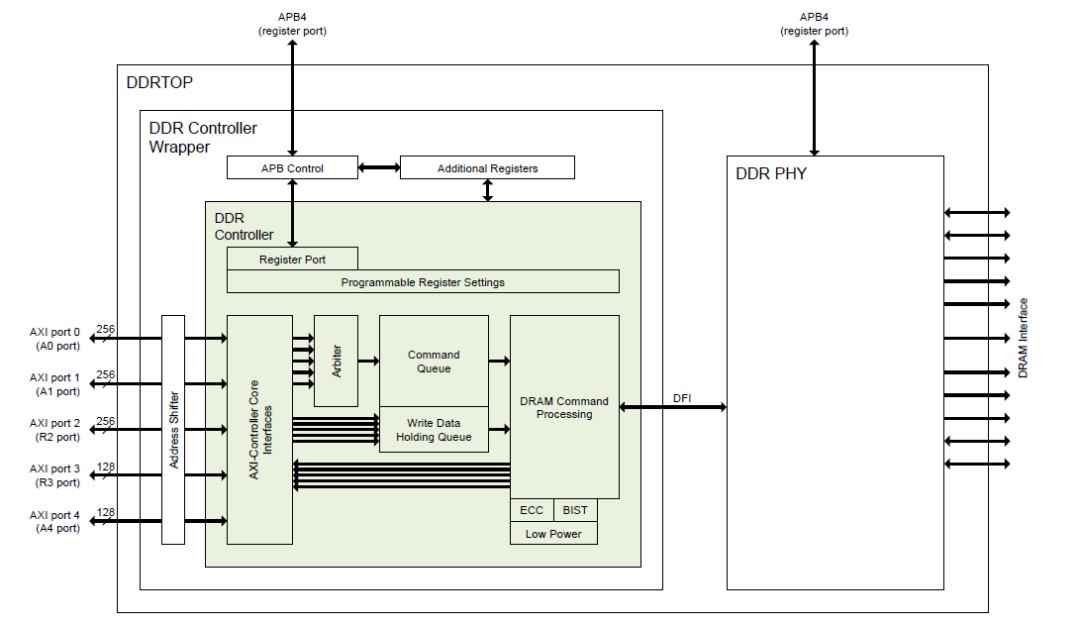

DDR的系統(tǒng)框圖

RZ T2H LPDDR4子系統(tǒng)是由MC (Memory Controller)和PHY構(gòu)成,支持JEDEC標(biāo)準(zhǔn) JESD209-4D。

其MC功能為:

完全流水線化的指令、讀數(shù)據(jù)和寫(xiě)數(shù)據(jù)接口,用于連接內(nèi)存控制器。

高級(jí)Bank預(yù)取功能,以提高內(nèi)存吞吐量。

可編程寄存器接口,用于控制內(nèi)存參數(shù)和協(xié)議,包括自動(dòng)預(yù)充電(Auto Pre-Charge)。

控制器復(fù)位時(shí)可對(duì)內(nèi)存進(jìn)行完全初始化。

支持加權(quán)輪詢(Weighted Round-Robin)仲裁機(jī)制,用于仲裁來(lái)自多個(gè)端口的請(qǐng)求。

支持ECC(錯(cuò)誤校正碼)功能,包括單比特和雙比特錯(cuò)誤報(bào)告、單比特錯(cuò)誤校正,并支持通過(guò)編程方式去除ECC存儲(chǔ)。

支持外部DRAM的內(nèi)建自測(cè)試(BIST,Built-In Self Test)。

PHY的功能:

指令總線眼圖(Bus Eye)訓(xùn)練,相對(duì)于時(shí)鐘信號(hào)CK進(jìn)行校準(zhǔn)。

寫(xiě)入調(diào)平(Write Leveling),用于補(bǔ)償CK-DQS之間的時(shí)序偏差(Timing Skew)。

寫(xiě)入訓(xùn)練(Write Training),用于對(duì)DQs、DM和DQS進(jìn)行去偏(Deskew):

基于指令的FIFO讀/寫(xiě)(WR/RD),支持用戶自定義模式(User Patterns)。

內(nèi)部DQS時(shí)鐘樹(shù)振蕩器,用于確定是否需要周期性訓(xùn)練以及所需的訓(xùn)練幅度。

數(shù)據(jù)總線VREFDQ訓(xùn)練,用于優(yōu)化寫(xiě)入信號(hào)質(zhì)量。

讀取訓(xùn)練(Read Training),用于對(duì)DQs、DM和DQS進(jìn)行去偏:

通過(guò)DRAM模式寄存器(Mode Registers)進(jìn)行DQ位(Bit)去偏訓(xùn)練。

通過(guò)DRAM陣列進(jìn)行DQS對(duì)DQ眼中心(Eye Centering)訓(xùn)練。

通過(guò)PHY主接口自動(dòng)執(zhí)行周期性再訓(xùn)練。

LVSTL(低電壓擺幅差分信號(hào))I/O校準(zhǔn) 及ODT(終端電阻)校準(zhǔn)。

支持軟件可控的DQ位和AC位交錯(cuò)(Swizzling),以優(yōu)化數(shù)據(jù)傳輸。

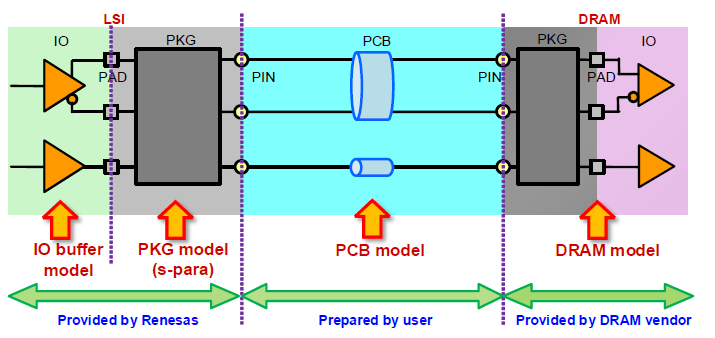

瑞薩提供了一整套的工具,方便客戶根據(jù)自己的情況選擇LPDDR4的物料。

這一套工具,包括PCB設(shè)計(jì)指導(dǎo)、PCB驗(yàn)證指導(dǎo)、硬件原理圖用戶指導(dǎo)手冊(cè)等。瑞薩官網(wǎng)上可以下載到IBIS文件和PKG Model文件,用于客戶更換DDR后的仿真工作。

信號(hào)完整性模型

瑞薩提供I/O緩沖模型(IO Buffer Model)和封裝模型(PKG Model)。用戶需要準(zhǔn)備PCB模型(PCB Model)。DRAM模型(DRAM Model) 由DRAM廠商提供。

同時(shí),瑞薩提供了非常易用的gen_tool,幫助客戶生成新的swizzle文件。

用以生成支持客戶選擇DDR型號(hào)的flash loader,u-boot和Linux內(nèi)核程序。

以下以某客戶將RZ T2H EVB上的美光MT53E2G32D4DE-046WT更換成海力士H54G36AYRVX246為例說(shuō)明軟件適配過(guò)程(前提是PCB硬件Layout已經(jīng)通過(guò)了SI/PI測(cè)試)

客戶將DDR顆粒大小從64Gb換成了8Gb,DQA/DQB的線序也做了調(diào)整。

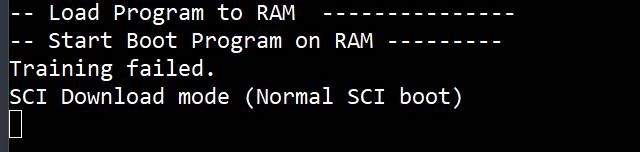

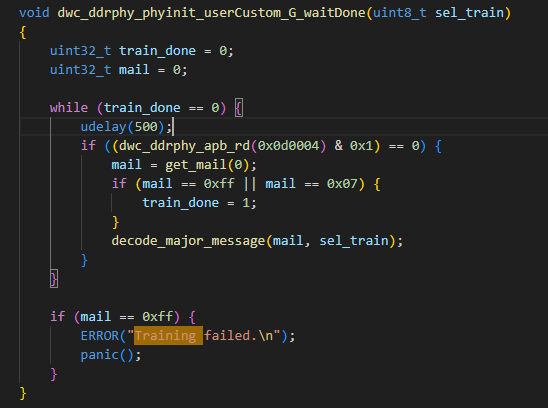

使用默認(rèn)Flash Loader程序,通過(guò)Log可以看出,Training Failed:

從Flash Loader源代碼中發(fā)現(xiàn)這個(gè)Fail的原因是DDR初始化失敗:

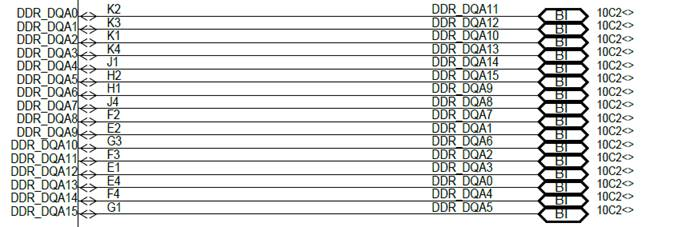

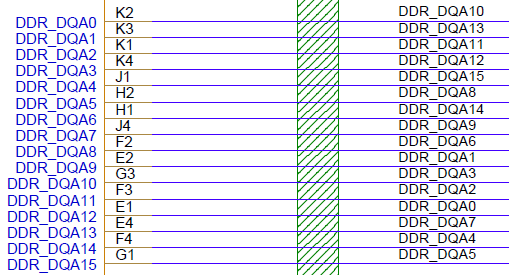

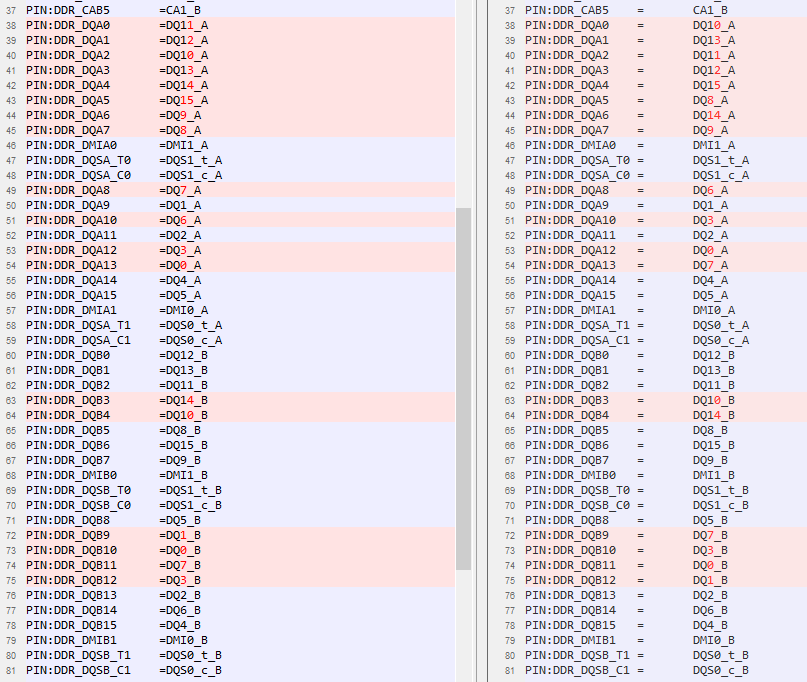

原理圖方面,T2H EVB的DQA是:

而客戶的DQA線序做了調(diào)整:

需要使用Renesas的DDR適配工具重新生成適配修改的代碼;

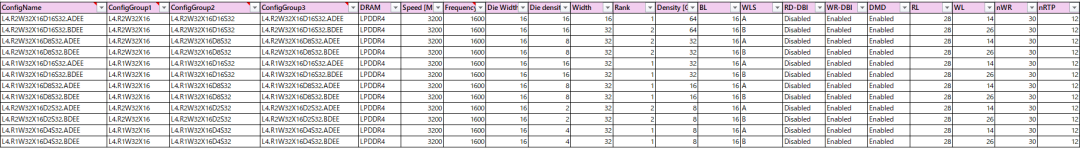

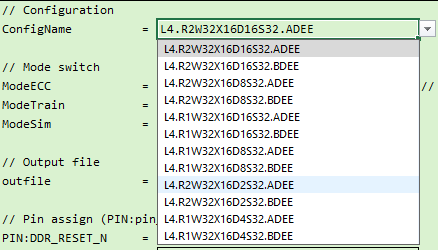

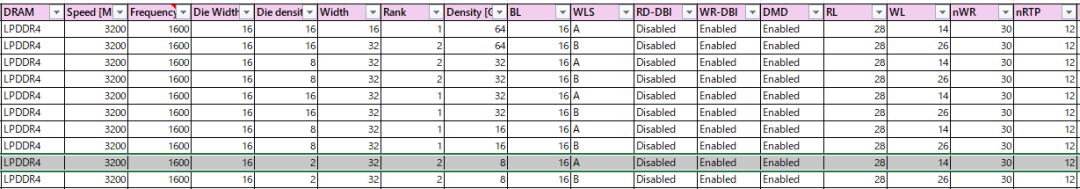

我們?cè)趃en_tool中,選擇L4.R2W32X16D2S32.ADEE,

即各個(gè)參數(shù)如下表(淺色的一行):

調(diào)整后,更換LPDDR4的差異主要集中在:DQA/DQB,以及DDR的顆粒密度上:

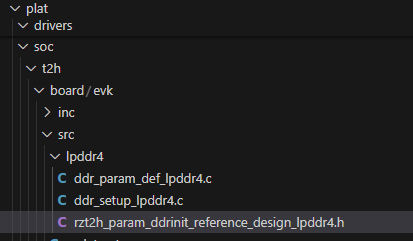

再運(yùn)行g(shù)en_tool,生成rzt2h_param_ddrinit_reference_design_lpddr4.h文件。

將該文件拷貝到/flash_programmer/plat/soc/t2h/board/evk/src/lpddr4/,替換rzt2h_param_ddrinit_reference_design_lpddr4.h文件。

重新編譯,得到新的flash loader文件:

*./rzt2_flash_programmer/project/flash-programmer/src/output/HDR NM

*./rzt2_flash_programmer/project/flash-programmer/src/output/Flash_Programmer_SCIF_CR52_RZT2H_EVK.mot

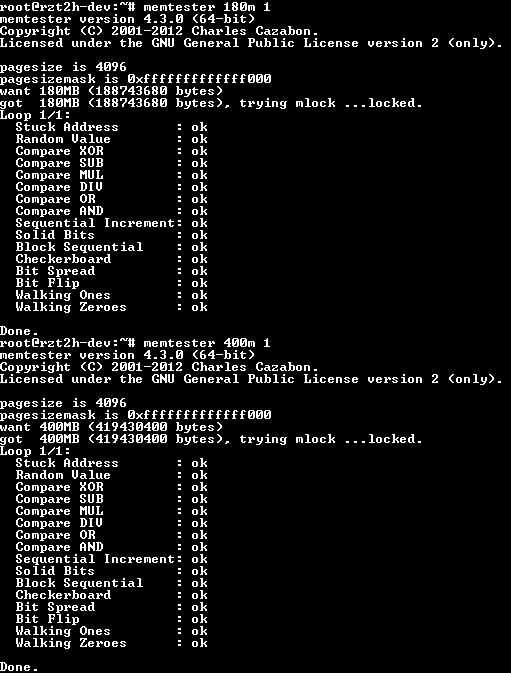

同時(shí),需要在BL2,F(xiàn)IP(trust-firmware-a和uboot)和設(shè)備樹(shù)文件處,修改LPDDR4的驅(qū)動(dòng),重新用YOCTO構(gòu)建uboot和內(nèi)核、dtb文件。運(yùn)行memtester 180m和memtester 400m驗(yàn)證DDR更換是否成功:

驗(yàn)證完畢,說(shuō)明DDR更換的軟件和硬件都已成功。

簡(jiǎn)要總結(jié)一下更換DDR流程:

1.硬件設(shè)計(jì)PCB階段,必須做SI/PI仿真。

2.通過(guò)瑞薩提供的工具生成DDR頭文件。

3.根據(jù)頭文件生成flash programmer。

4.生成FIP(包含uboot)文件。如果大小不同,需要修改設(shè)備樹(shù)文件。

RZ T2H完整的軟硬件設(shè)計(jì)規(guī)范、參考例程、工具等,請(qǐng)點(diǎn)擊下方鏈接獲取更多資料。

-

寄存器

+關(guān)注

關(guān)注

31文章

5611瀏覽量

130124 -

DDR

+關(guān)注

關(guān)注

11文章

756瀏覽量

69226 -

內(nèi)存

+關(guān)注

關(guān)注

9文章

3215瀏覽量

76407 -

瑞薩

+關(guān)注

關(guān)注

37文章

22492瀏覽量

90958

發(fā)布評(píng)論請(qǐng)先 登錄

瑞薩RZ/T2H PCIe通信的調(diào)試方法

RZ T2H PCIe裸機(jī)程序開(kāi)發(fā)和Linux下的配置介紹

瑞薩RZ/T2H平臺(tái)多核異構(gòu)的應(yīng)用場(chǎng)景分析

【米爾瑞薩RZ/G2L開(kāi)發(fā)板-試用體驗(yàn)】認(rèn)識(shí)一下米爾瑞薩RZ/G2L開(kāi)發(fā)板的核心板

瑞薩RZ/T2H新產(chǎn)品量產(chǎn)上市

工業(yè)MPU新標(biāo)桿,多協(xié)議工業(yè)以太網(wǎng)+運(yùn)動(dòng)控制 - 瑞薩RZ/T2H 新產(chǎn)品

瑞薩電子量產(chǎn)高性能工業(yè)設(shè)備MPU RZ/T2H

瑞薩電子RZ MPU家族精品RZ/N2L產(chǎn)品介紹

瑞薩交流日進(jìn)行中,米爾演講-RZ/T2H高性能模組賦能工業(yè)產(chǎn)品創(chuàng)新

RZ/T2H MPU數(shù)據(jù)手冊(cè)和產(chǎn)品介紹#集成了強(qiáng)大的應(yīng)用處理能力和精確的實(shí)時(shí)控制功能

Renesas RZ/T2H 評(píng)估板:功能特性與使用指南

新品!瑞薩RZ/T2H驅(qū)控一體單芯、多軸實(shí)時(shí)控制,助力工業(yè)以太網(wǎng)

瑞薩RZ T2H更換DDR流程和工具介紹

瑞薩RZ T2H更換DDR流程和工具介紹

評(píng)論