ADS58B18/B19屬于超低功耗ADS4xxx模數轉換器(ADC)系列,該系列集成模擬緩沖器和SNRBoost技術。ADS58B18和ADS58B19分別是11位和9位ADC,采樣率分別高達200MSPS和250MSPS。采用創新設計技術,在極低功耗的同時實現高動態性能。模擬輸入引腳具有穩定性能和輸入阻抗的緩沖器,覆蓋寬頻范圍。該架構使這些部件非常適合多載波寬帶寬通信應用,如PA線性化。

*附件:ads58b19.pdf

該 ADS58B18 采用 TI 專有的 SNRBoost 技術,可用于克服因量化噪聲而導致的 SNR 限制,適用于帶寬低于奈奎斯特(f S /2).

兩款設備均有增益選項,可用于提升SFDR在較低全刻度輸入范圍,尤其是極高輸入頻率下的性能。它們還包括一個直流偏移校正環路,可以用來取消ADC偏移。在較低采樣率下,ADC自動以降低功率運行,且性能不損耗。

這些設備支持雙倍數據速率(DDR)低電壓差分信號(LVDS)和并行CMOS數字輸出接口。DDR LVDS接口的低數據率(最高500Mbps)使得使用基于FPGA的低成本現場可編程門陣列(FPGA)接收成為可能。它們具有低擺幅的LVDS模式,可用于進一步降低功耗。LVDS輸出緩沖器的強度也可以提高,以支持50Ω差分終端。

ADS58B18/B19均采用緊湊型QFN-48封裝,并規范工業溫度范圍(–40°C至+85°C)。

特性

- ADS58B18:11位,200MSPS

- ADS58B19:9位,250MSPS

- 集成高阻抗模擬輸入緩沖器

- 超低功率:

- 模擬功率:258mW,200MSPS

- 輸入輸出功率:69mW(DDR低頻,低LVDS擺幅)

- 高動態性能:

- ADS58B18:66dBFS 信噪比和 81dBc SFDR,150MHz

- ADS58B19:150MHz時,信噪比55.7dBFS和SFDR76dBc

- 利用TI專有SNRBoost技術增強信噪比(僅限于ADS58B18)

- –20MHz帶寬下的77.7dBFS信噪比

- 采樣率動態功率縮放

- 輸出接口:

- 雙倍數據率(DDR)LVDS,具備可編程擺幅和強度

- 標準擺幅:350mV

- 低擺幅:200mV

- 默認強度:100Ω 終端

- 2倍強度:50Ω終端

- 還支持 1.8V 并行 CMOS 接口

- 雙倍數據率(DDR)LVDS,具備可編程擺幅和強度

- 可編程增益用于信噪比/SFDR權衡

- 直流偏移校正

- 支持低輸入時鐘幅度

- 包裝:QFN-48(7毫米×7毫米)

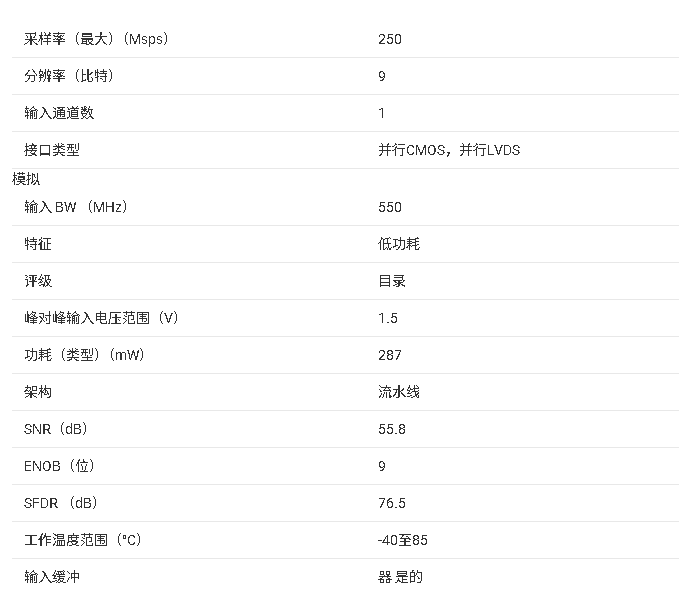

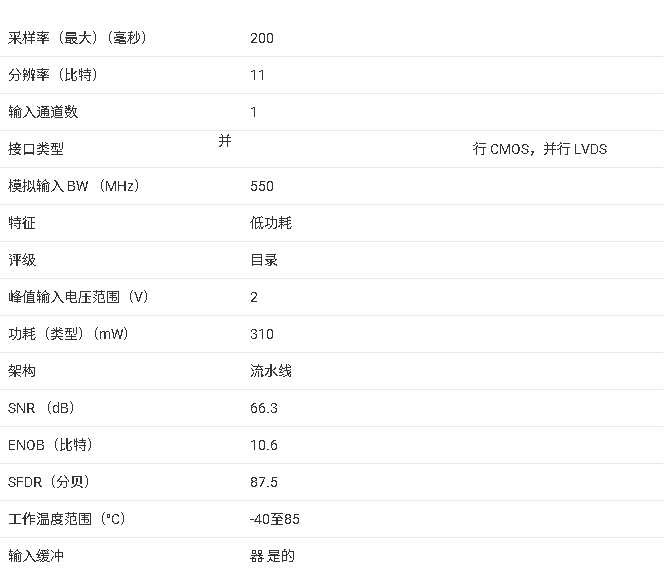

參數

方框圖

ADS58B18 與 ADS58B19 是德州儀器(TI)推出的高速低功耗模數轉換器(ADC),核心優勢為高采樣率、超低功耗與靈活輸出接口,適配多載波通信、功率放大器線性化等寬帶信號處理場景,二者引腳兼容,僅分辨率與采樣率存在差異。

一、核心產品參數

1. 基礎性能指標

- 分辨率與采樣率 :ADS58B18 為 11 位分辨率,最高 200 MSPS 采樣率;ADS58B19 為 9 位分辨率,最高 250 MSPS 采樣率;均支持 30~80 MSPS 低速模式,自動降低功耗。

- 動態性能 :150MHz 輸入時,ADS58B18 SNR 典型值 66 dBFS、SFDR 81 dBc,支持 SNRBoost 技術(20MHz 帶寬下 SNR 可達 77.7 dBFS);ADS58B19 SNR 典型值 55.7 dBFS、SFDR 76 dBc;二者總諧波失真(THD)均優于 70 dBc。

- 輸入特性 :集成高阻抗模擬輸入緩沖器,差分輸入范圍 1.5 VPP,輸入帶寬 550 MHz;共模電壓 1.7V,輸入電阻 4 kΩ,輸入電容 2.1 pF,抗干擾能力強。

- 功耗與供電 :模擬功耗典型值 258 mW(ADS58B18,200 MSPS)、287 mW(ADS58B19,250 MSPS);數字功耗(DDR LVDS 低擺幅)69 mW;模擬電源(AVDD)與數字電源(DRVDD)均為 1.7

1.9V,緩沖器電源(AVDD_BUF)33.6V。

2. 環境與封裝

- 工作溫度:工業級范圍(-40°C 至 85°C),結溫最高 125°C;

- 封裝形式:48 引腳 QFN 封裝(7mm×7mm),帶 PowerPAD 熱增強結構,符合 RoHS 標準,引腳鍍層為 NIPDAUAG,MSL 等級 3,峰值回流溫度 260°C;

- ESD 防護:人體模型(HBM)2 kV,滿足工業設備防護需求。

二、關鍵功能特性

1. 信號處理與增強

- SNRBoost 技術(僅 ADS58B18):可優化特定帶寬內 SNR,通過寄存器配置系數調整目標頻段(0~fS/2),適配窄帶高信噪比需求;

- 可編程增益:支持 0~3.5 dB 步進(0.5 dB / 步),通過降低滿量程輸入范圍提升 SFDR,實現 SNR 與 SFDR 靈活權衡;

- 偏移校正:內置直流偏移校正環路,支持 ±10mV 偏移補償,校正時間常數可通過寄存器配置(1M~2G 時鐘周期)。

2. 輸出接口與控制

- 雙輸出模式:支持 DDR LVDS(默認 100Ω 終端,可配置 50Ω)與 1.8V 并行 CMOS 接口,LVDS 擺幅可編程(200mV 低擺幅 / 350mV 標準擺幅);

- 數據格式:兼容二進制補碼與偏移二進制,支持位序(bit-wise)與字節序(byte-wise)輸出,適配不同 FPGA/ASIC 接收邏輯;

- 串行接口:通過 SCLK/SDATA/SEN 引腳配置寄存器,支持測試模式、功耗控制、輸出參數調整,OVR_SDOUT 引腳兼具過載指示與寄存器讀回功能。

3. 低功耗設計

- 動態功耗縮放:采樣率降低時自動縮減功耗,無性能損失;

- 多功耗模式:支持全局掉電(10 mW)、待機(185 mW)、輸出緩沖器禁用三種低功耗模式,喚醒時間最短 50 ns。

三、應用與設計要點

1. 典型應用場景

2. 硬件設計建議

- 供電與去耦 :AVDD、DRVDD、AVDD_BUF 需獨立供電,就近放置 0.1 μF 陶瓷電容 + 1 μF 鉭電容去耦,減少電源噪聲耦合;

- 布局規范:PowerPAD 需焊接至 PCB 接地平面,搭配熱過孔優化散熱;模擬輸入(INP/INM)與時鐘輸入(CLKP/CLKM)需差分對稱布線,遠離數字電路;LVDS 輸出軌跡阻抗匹配(100Ω 差分)。

- 輸入驅動:低頻率輸入采用單變壓器驅動,高頻率(>奈奎斯特頻率)推薦雙變壓器背對背配置,輸入串接 5~10Ω 電阻抑制振鈴。

3. 編程與配置

- 模式配置:通過 DFS 引腳或寄存器選擇輸出接口(LVDS/CMOS)與數據格式;SNRBoost、增益、偏移校正等功能通過串行寄存器啟用與參數配置;

- 時鐘適配:支持差分(正弦波、LVPECL、LVDS)或單端(LVCMOS)時鐘輸入,差分時鐘振幅最低 0.2 VPP,時鐘占空比 35%~65% 均可穩定工作。

四、產品差異與選型適配

- 核心差異:ADS58B18 分辨率更高(11 位)、SNR 性能更優,支持 SNRBoost 技術,適合對精度要求高的場景;ADS58B19 采樣率更高(250 MSPS)、成本更低,適合對分辨率要求不高的高速采集場景;

- 選型建議:優先根據分辨率與采樣率需求選型,需 11 位精度且采樣率≤200 MSPS 選 ADS58B18,需更高采樣率(≤250 MSPS)且預算敏感選 ADS58B19,二者硬件設計可復用。

-

緩沖器

+關注

關注

6文章

2234瀏覽量

48944 -

adc

+關注

關注

100文章

7566瀏覽量

556490 -

模數轉換器

+關注

關注

26文章

4028瀏覽量

130183 -

寬帶寬

+關注

關注

0文章

46瀏覽量

1369

發布評論請先 登錄

請問ADS58B19如何采樣直流信號?

ADS58b19模擬信號輸入范圍是多少?

ADS58b19模擬信號輸入范圍怎么理解

如何在ADS58B19上采樣直流信號?

ADS58B18和ADS58B19的英文原版數據手冊免費下載

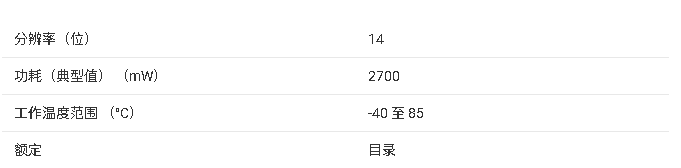

ADS58J89 ADS58J89 和 ADS58J88 數據表

ADS7056超低功耗、超小尺寸14位高速SAR ADC數據表

ADS58J64 技術文檔核心總結

ADS58J63 產品核心信息總結

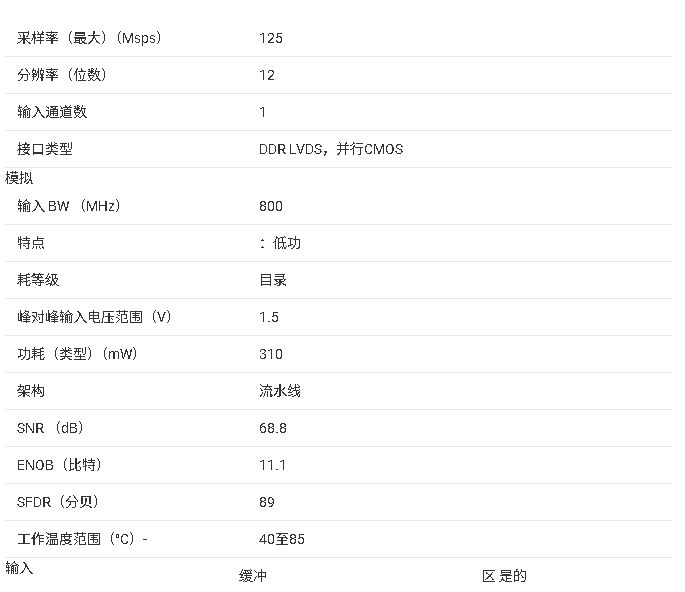

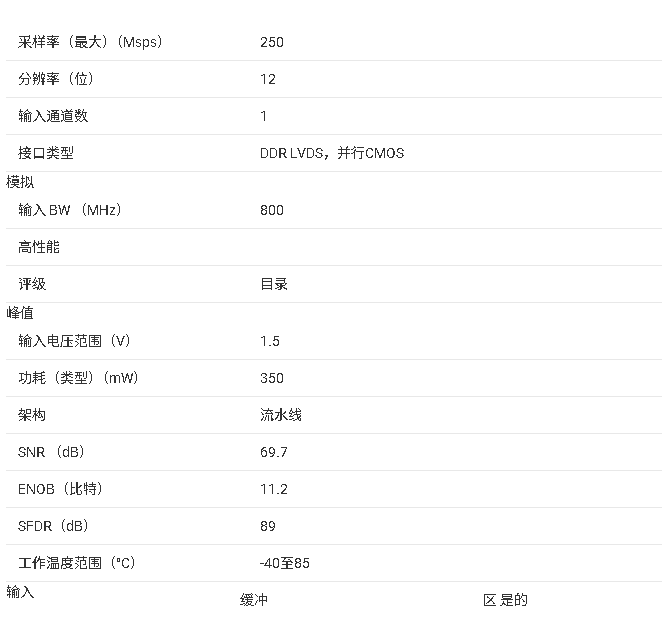

ADS41B25 12 位超低功耗 ADC 產品總結

ADS58C20/ADS58C23 雙 IF 接收器產品總結

ADS41B29/ADS41B49 高速低功耗模數轉換器產品總結

ADS58B18/ADS58B19 超低功耗高速 ADC 產品總結

ADS58B18/ADS58B19 超低功耗高速 ADC 產品總結

評論