該ADS42B49是一款超低功耗雙通道、14位模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)集成了模擬輸入緩沖器。它采用創(chuàng)新設計技術實現(xiàn)高動態(tài)性能,同時消耗極低功耗。模擬輸入緩沖器的存在使該設備易于驅(qū)動,并有助于在寬頻范圍內(nèi)實現(xiàn)高性能。 這 ADS42B49非常適合多載波寬帶寬通信應用。

ADS42B49具有增益選項,可用于在較低全功度輸入下提升SFDR性能 范圍。 該設備還包含一個直流偏移校正環(huán)路,可用于取消ADC偏移。 雙 DDR LVDS和并行CMOS數(shù)字輸出接口集成在緊湊型VQFN-64 PowerPAD?中 包。

*附件:ads42b49.pdf

該器件包含內(nèi)部參考,而傳統(tǒng)的參考引腳和相關的解耦電容器已被取消。ADS42B49在工業(yè)溫度范圍內(nèi)(–40°C至8°C)內(nèi)被指定。

特性

- 最大采樣率:250 MSPS

- 超低功率:

- 850毫瓦總功率,250 MSPS

- 集成模擬輸入緩沖器:

- 高動態(tài)性能:

- 85 dBc SFDR,頻率為170 MHz

- 170 MHz 時 70.7 dBFS 信噪比

- 串擾:> 85 dB,頻率為185 MHz

- 可編程增益最高可編程6 dB,用于信

噪比和SFDR權衡 - 直流偏移校正

- 輸出接口選項:

- 1.8伏并行CMOS接口

- 雙倍數(shù)據(jù)率(DDR)LVDS帶可編程擺動:

- 標準擺動:350 mV

- 低擺幅:200 mV

- 支持低輸入時鐘幅度,最低可達200 mV

PP - 封裝:9.00 毫米 × 9.00 毫米,64針四針扁平

無引腳(VQFN)封裝

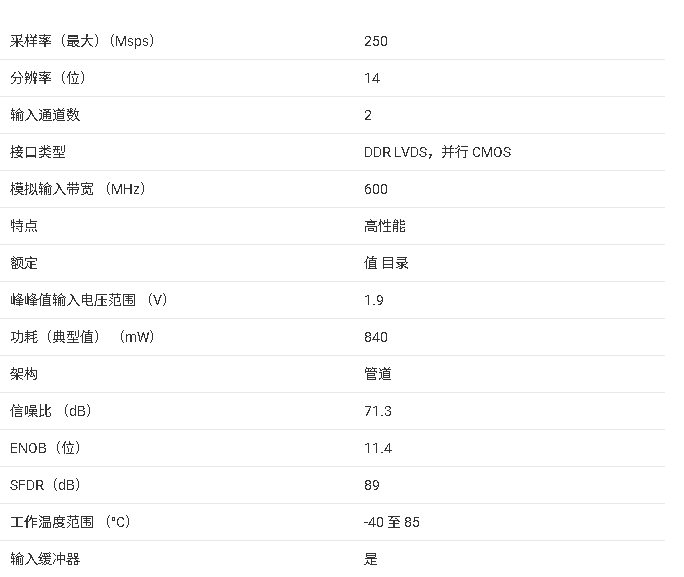

參數(shù)

方框圖

一、產(chǎn)品概述

ADS42B49 是德州儀器(TI)推出的雙通道 14 位超高速低功耗模數(shù)轉(zhuǎn)換器(ADC),核心優(yōu)勢為集成模擬輸入緩沖器、動態(tài)性能優(yōu)異、功耗控制出色,支持 DDR LVDS 和并行 CMOS 雙輸出接口,適用于無線通信基礎設施、軟件無線電、功率放大器線性化等對速率和功耗均敏感的高速信號采集場景。文檔版本為 SBAS558C,最初發(fā)布于 2012 年 12 月,2015 年 12 月修訂,器件采用 64 引腳 VQFN 封裝(9.00 mm×9.00 mm),工作溫度范圍 - 40°C 至 85°C。

二、核心參數(shù)與性能特性

1. 基礎規(guī)格

- 分辨率與采樣率 :14 位分辨率(無失碼),最高采樣率 250 Msps,支持低速模式(1 Msps-80 Msps),適配不同速率需求。

- 動態(tài)性能 :170 MHz 輸入時,SFDR 達 85 dBc,SNR 達 70.7 dBFS,ENOB 達 11.4 LSB;通道間串擾>85 dB,雙路同步性能優(yōu)異;輸入帶寬(3 dB)達 700 MHz,支持寬頻率信號采集。

- 輸入特性 :差分輸入滿量程 2 Vpp,輸入共模電壓 1.9 V(內(nèi)部自偏置,無需外部偏置),170 MHz 時輸入阻抗 1.1 kΩ、輸入電容 2.2 pF,驅(qū)動難度低。

2. 供電與功耗

- 供電范圍 :需三組電源供電,AVDD(模擬)1.8 V-2.0 V(標稱 1.9 V),AVDD_BUF(模擬緩沖)3.15 V-3.45 V(標稱 3.3 V),DRVDD(數(shù)字)1.7 V-2.0 V(標稱 1.8 V)。

- 功耗表現(xiàn) :250 Msps 時總功耗僅 850 mW(每通道 425 mW),超低功耗優(yōu)勢顯著;支持全局掉電(典型功耗 20 mW)和通道待機模式(典型功耗 240 mW),適配低功耗場景。

3. 封裝與環(huán)境適應性

- 封裝類型 :64 引腳 VQFN 封裝,帶裸露熱焊盤,散熱性能優(yōu)異,結(jié)到環(huán)境熱阻(θJA)23.9 °C/W,結(jié)到板熱阻(θJB)4.3 °C/W。

- 可靠性 :ESD 防護電壓 ±2000 V(人體模型 HBM)、±500 V(充電器件模型 CDM);結(jié)溫最高 125°C,長期工作穩(wěn)定性良好。

4. 接口特性

- 數(shù)據(jù)輸出 :支持 DDR LVDS(標準擺幅 350 mV、低擺幅 200 mV,可編程)和 1.8 V 并行 CMOS 雙接口,LVDS 模式下數(shù)據(jù)速率 500 Mbps,CMOS 模式支持單獨引腳輸出。

- 控制接口 :支持 SPI 串行接口(最高 20 MHz)和并行控制引腳,可配置工作模式、增益、輸出格式等參數(shù),靈活適配不同系統(tǒng)設計。

三、工作模式與功能原理

1. 核心架構(gòu)

雙通道獨立設計,每通道集成模擬輸入緩沖器、14 位 ADC 采樣電路、數(shù)字校正邏輯及輸出序列化器;采用流水線架構(gòu),默認數(shù)據(jù)延遲 11 個時鐘周期,支持數(shù)字功能(增益 / 偏移校正、測試模式)啟用(延遲 19 個時鐘周期)。

2. 主要工作模式

- 高速模式 :采樣率 80 Msps-250 Msps,時鐘占空比 45%-55%,適配高速信號采集。

- 低速模式 :采樣率 1 Msps-80 Msps,時鐘占空比 40%-60%,降低功耗的同時保證基礎性能。

- 掉電與待機模式 :全局掉電模式關閉所有模塊,喚醒時間 100 μs;通道待機模式僅關閉 ADC 通道,喚醒時間 50 μs,平衡功耗與響應速度。

- 復用模式 :雙路數(shù)據(jù)復用至單總線輸出(DB [13:0]),適配低采樣率下的接口簡化需求(建議<125 Msps)。

3. 關鍵功能細節(jié)

- 可編程增益 :支持 0 dB-6 dB 增益調(diào)節(jié)(0.5 dB 步進),可權衡 SFDR 與 SNR 性能,高頻率輸入時 SFDR 提升顯著。

- 偏移校正 :內(nèi)置 DC 偏移校正算法,可校正 ±10 mV 偏移,校正時間常數(shù)可編程(1 M-2 G 時鐘周期),支持凍結(jié)校正結(jié)果。

- 靈活輸出格式 :支持二進制補碼和偏移二進制兩種數(shù)據(jù)格式,LVDS 模式下每對差分引腳復用兩位數(shù)據(jù),提升接口效率。

四、應用場景與設計建議

1. 典型應用領域

- 無線通信基礎設施、軟件無線電(SDR)、功率放大器(PA)線性化、寬帶信號采集系統(tǒng)等。

2. 設計關鍵要點

- 電源設計 :模擬電源(AVDD、AVDD_BUF)對噪聲敏感,建議使用低噪聲電源或添加濾波電路;所有電源引腳需就近并聯(lián) 0.1 μF 去耦電容,降低電源噪聲串擾。

- 輸入與時鐘設計 :模擬輸入需差分驅(qū)動,建議串聯(lián) 5 Ω-10 Ω 電阻抑制振鈴;時鐘支持差分(正弦波、LVPECL、LVDS)或單端(LVCMOS)輸入,高速采樣時推薦低抖動時鐘源,時鐘幅度最低可至 200 Vpp。

- 布線與散熱 :PCB 需劃分模擬區(qū)、數(shù)字區(qū)和時鐘區(qū),差分信號線成對緊密布線;裸露熱焊盤需焊接至地平面,確保散熱效率,避免結(jié)溫過高。

-

緩沖器

+關注

關注

6文章

2227瀏覽量

48879 -

adc

+關注

關注

100文章

7511瀏覽量

555903 -

模數(shù)轉(zhuǎn)換器

關注

26文章

4013瀏覽量

130100 -

數(shù)字轉(zhuǎn)換器

關注

0文章

347瀏覽量

28761 -

寬帶寬

+關注

關注

0文章

46瀏覽量

1356

發(fā)布評論請先 登錄

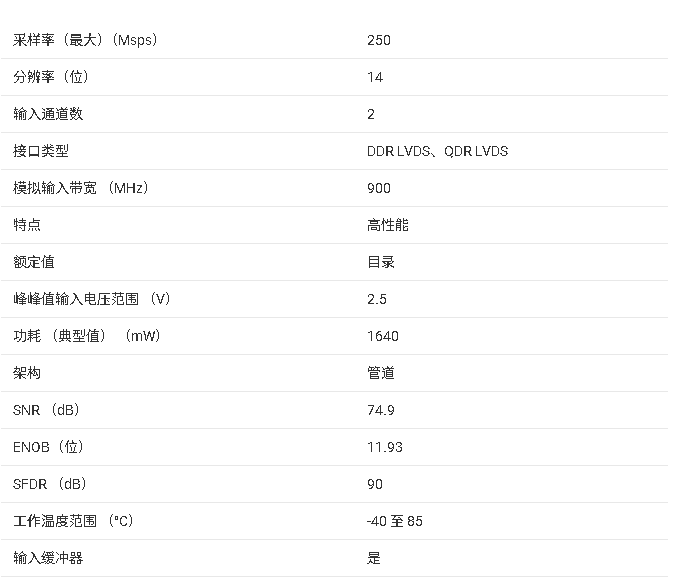

ADI推出雙通道14位250 MSPS模數(shù)轉(zhuǎn)換器AD9250

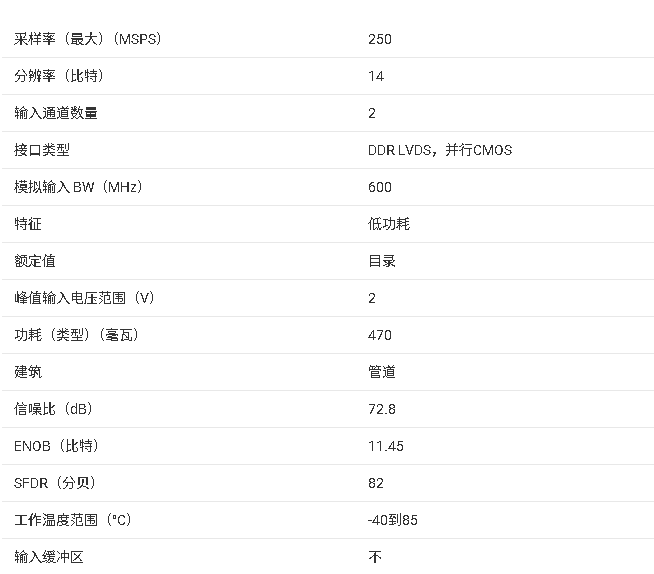

ADS4149:一款超低功耗14位的250-MSPS的數(shù)模轉(zhuǎn)換器

ADS42LB49/69雙通道模數(shù)轉(zhuǎn)換器的功能特點及應用范圍

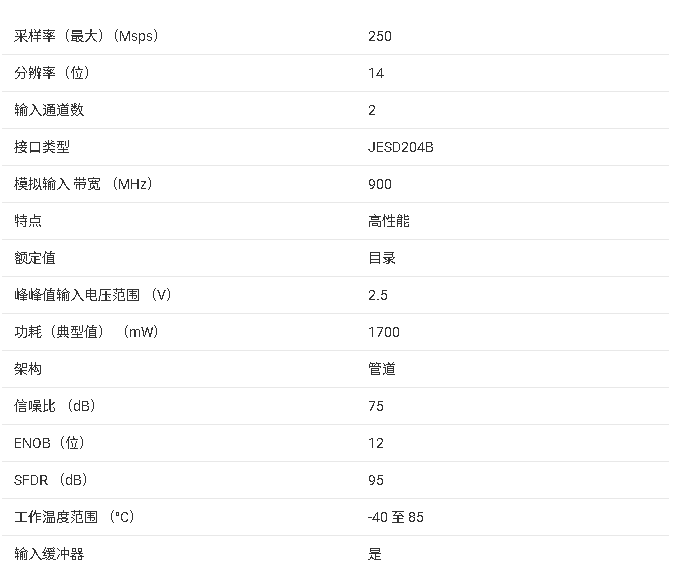

AD9680: 14位、1000 MSPS JESD204B雙通道模數(shù)轉(zhuǎn)換器

ADS42B49具有模擬輸入緩沖器的雙通道、14位、250MSPS超低功耗ADC數(shù)據(jù)表

ADS4249雙通道、14位、250MSPS超低功耗ADC數(shù)據(jù)表

ADS4245-EP雙通道,14位,125MSPS超低功率模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS54J42雙通道、14位、625MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS42JBx9雙通道、14和16位、250MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS42JBx9 14位和16位250MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS42JB46雙通道、14位、160MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

?ADS61B29/ADS61B49 14位/12位250MSPS模數(shù)轉(zhuǎn)換器技術文檔總結(jié)

ADS42B49 雙通道 14 位 250-Msps 超低功耗模數(shù)轉(zhuǎn)換器技術規(guī)格與應用總結(jié)

ADS42B49 雙通道 14 位 250-Msps 超低功耗模數(shù)轉(zhuǎn)換器技術規(guī)格與應用總結(jié)

評論