該ADS4249屬于ADS42xx超低功耗系列,包括雙通道、12位和 14位模數轉換器(ADC)。采用創新設計技術以實現高水平 動態性能,同時在1.8伏電源下功耗極低。該拓撲使得 該ADS4249非常適合多載波寬通信應用。

ADS4249具有增益選項,可用于在較低時提升SFDR性能 全尺寸輸入范圍。該設備還包含一個直流偏移校正環路,可用于 取消ADC偏移。DDR LVDS和并行CMOS數字輸出接口均可采用 緊湊型QFN-64 PowerPAD封裝。

*附件:ads4249.pdf

該器件包含內部參考,而傳統的參考引腳和 相關的解耦電容已被取消。ADS4249在工業層面上被指定 溫度范圍(–40°C至85°C)。

特性

- 最大采樣率:250 MSPS

- 超低功率,單1.8伏電源:

- 560毫瓦總功率,功率250 MSPS

- 高動態性能:

- 170 MHz 80 dBc SFDR

- 170 MHz 時 71.7 dBFS 信噪比

- 串擾:> 90 dB,頻率為185 MHz

- 可編程增益最高可達6 dB,用于信

噪比/SFDR 權衡 - 直流偏移校正

- 輸出接口選項:

- 1.8伏并行CMOS接口

- 雙倍數據率(DDR)LVDS帶可編程擺動:

- 標準擺動:350 mV

- 低擺幅:200 mV

- 支持低輸入時鐘幅度,最低可達200 mV

PP - 封裝:9毫米 × 9毫米,64針四針扁平無

引腳(QFN)封裝

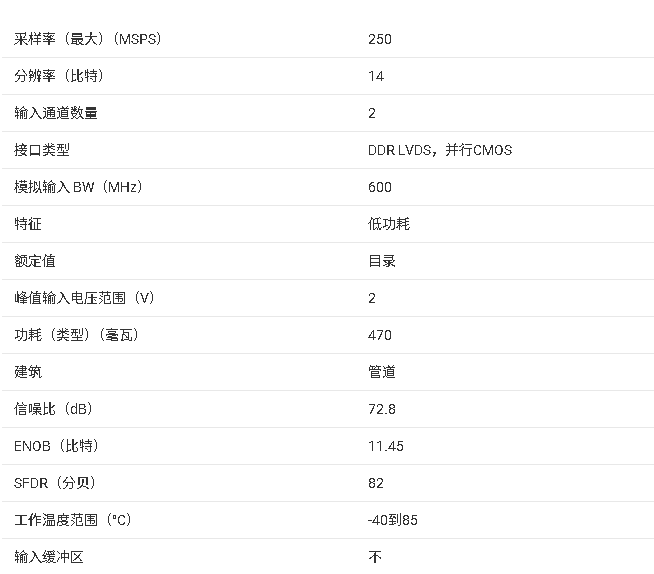

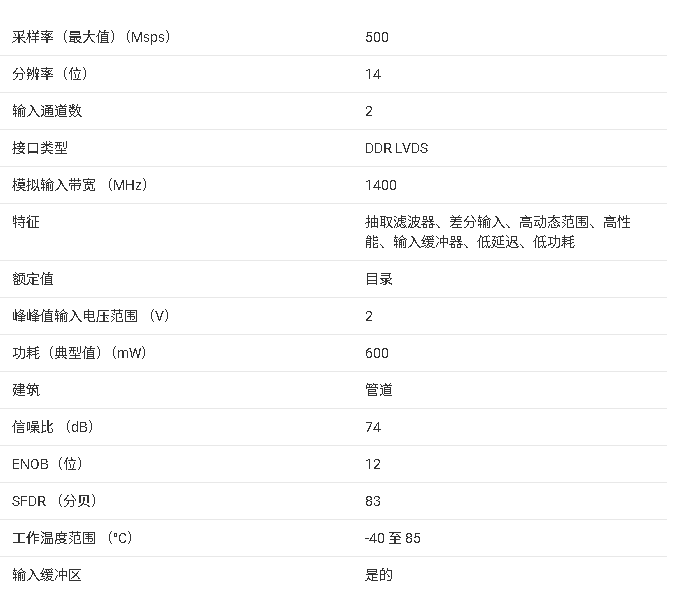

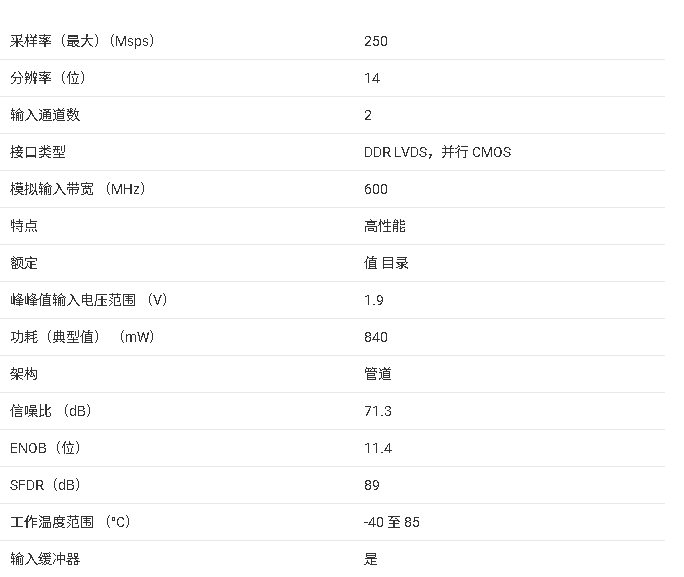

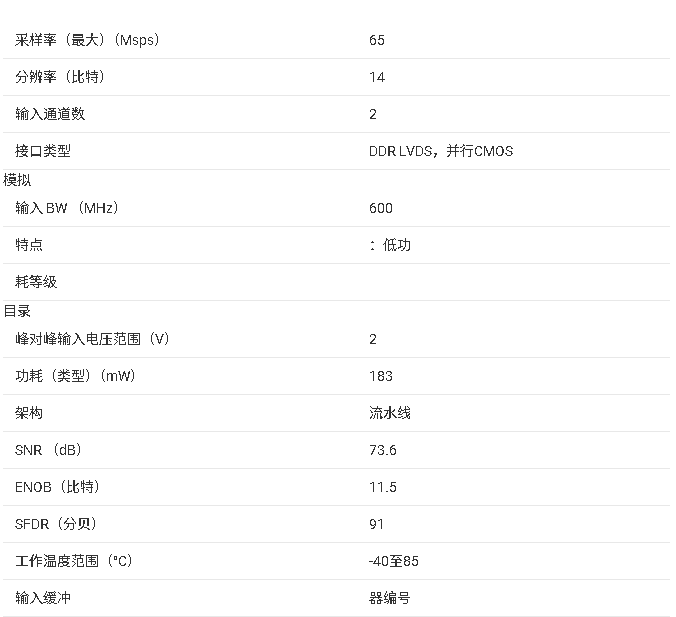

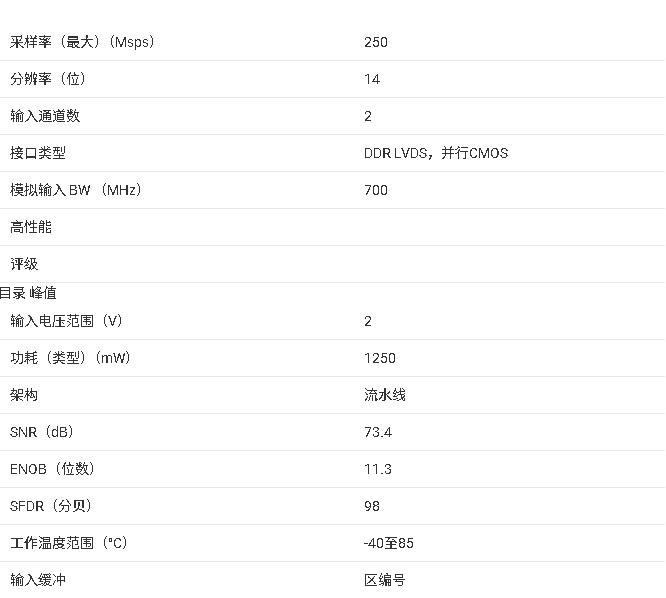

參數

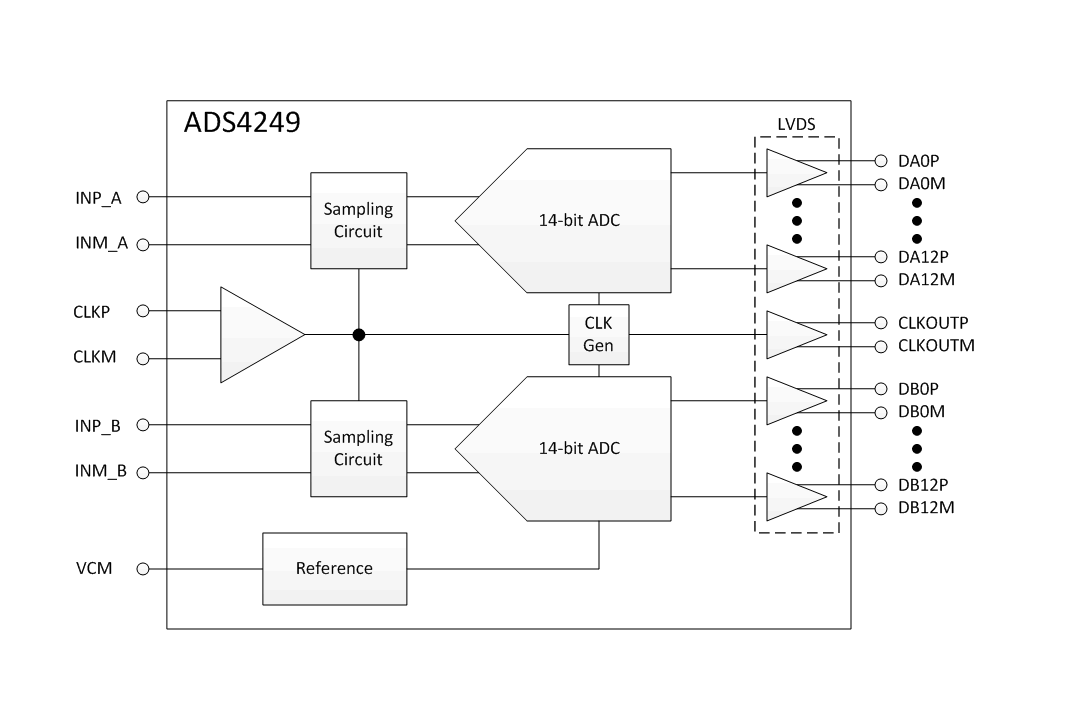

方框圖

ADS4249 是德州儀器(TI)推出的雙通道 14 位高速 ADC,采樣率高達 250 MSPS,采用單 1.8V 供電,總功耗僅 560 mW,支持 DDR LVDS 與并行 CMOS 雙輸出接口,具備可編程增益、直流偏移校正等功能,專為無線通信基礎設施、軟件無線電、功率放大器線性化等高速信號采集場景設計。

一、芯片基礎信息與核心特性

1. 基礎規格

- 文檔與型號 :文檔編號 SBAS534E,2011 年 7 月發布、2016 年 1 月修訂,與 ADS42xx 系列其他產品架構兼容,引腳兼容前代 ADS62P49。

- 供電與溫度 :模擬電源(AVDD)與數字電源(DRVDD)均為 1.7V-1.9V(標稱 1.8V);工作溫度 - 40°C 至 85°C,結溫最高 125°C,存儲溫度 - 65°C 至 150°C。

- 封裝與散熱 :9mm×9mm 64 引腳 VQFN 封裝,底部帶 PowerPAD 熱焊盤(連接 DRGND),結到環境熱阻 23.9°C/W,熱焊盤需焊接至 PCB 接地平面以保障散熱。

2. 核心性能指標

- 采樣與分辨率 :14 位分辨率,無失碼;最大采樣率 250 MSPS,支持低速模式(≤80 MSPS);孔徑抖動 140 fs rms,通道間串擾 > 90 dB(185 MHz 時)。

- AC 性能 :170 MHz 輸入時,SNR 達 71.7 dBFS,SFDR 80 dBc,THD -76 dBc;輸入帶寬 550 MHz(50Ω 源阻抗 + 50Ω 終端),支持最高 400 MHz(2 VPP)/600 MHz(1 VPP)輸入頻率。

- 功耗與靈活性 :250 MSPS 時總功耗 560 mW(每通道 280 mW),支持全局掉電(功耗 20 mW)與通道 Standby 模式(喚醒時間 50 μs);輸入共模電壓 0.95 V(高性能模式下 0.87 V),差分輸入范圍 2 VPP。

- 接口特性 :DDR LVDS 輸出支持 350 mV(標準)/200 mV(低擺幅)可編程,并行 CMOS 接口支持 1.8V 邏輯;支持二進制補碼 / 偏移二進制數據格式,內置測試圖案生成功能。

二、關鍵功能模塊與工作原理

1. 核心功能模塊

- 雙通道同步采樣架構 :

- 兩個獨立 14 位 ADC 通道,支持同步采樣,通道間隔離度高,確保高速信號相位一致性。

- 采樣電路采用開關電容差分結構,輸入帶寬 550 MHz,適配高頻信號采集;內置 RC 濾波器抑制采樣毛刺,外部可擴展 R-C-R 濾波進一步優化性能。

- 靈活數字功能 :

- 可編程增益:0-6 dB 步進 0.5 dB 可調,通過降低滿量程輸入范圍提升 SFDR,適配不同幅度信號采集。

- 偏移校正:支持 ±10 mV 直流偏移自動校正,校正時間常數可通過寄存器配置(1M-2G 時鐘周期),可凍結校正結果。

- 低功耗模式:支持全局掉電(喚醒時間 100 μs)、通道 Standby(喚醒時間 50 μs)、時鐘停止低功耗模式(采樣率 < 1 MSPS 時自動觸發)。

- 雙輸出接口 :

- DDR LVDS 模式:每對差分線復用 2 位數據,支持 100Ω/50Ω 終端,擺幅可編程,適合長距離高速傳輸。

- 并行 CMOS 模式:14 位數據獨立輸出,CLKOUT 同步時鐘,建議負載電容≤5 pF,適合短距離高帶寬傳輸。

- 多路復用模式:雙通道數據復用至單通道輸出總線,適合低采樣率(<80 MSPS)場景。

2. 工作原理

- 模擬信號經差分輸入通道(INP_A/INM_A、INP_B/INM_B)輸入,由采樣電路同步捕獲后,經 14 位 ADC 轉換為數字信號;通過 DDR 序列化或并行輸出模塊輸出,支持增益調節、偏移校正等數字處理功能。

- 時鐘信號經差分輸入(CLKP/CLKM)送入內部時鐘發生器,生成采樣時鐘與輸出同步時鐘;支持正弦波、LVPECL、LVDS、LVCMOS 等多種時鐘輸入類型,最小輸入幅度低至 200 VPP。

三、應用場景與設計建議

1. 典型應用

- 無線通信基礎設施 :適配 LTE、W-CDMA 等多載波信號接收,雙通道支持分集接收架構,高速采樣滿足寬帶寬信號采集需求。

- 軟件無線電(SDR) :高帶寬與低功耗平衡,支持多頻段信號同步采集,可編程增益適配不同強度信號。

- 功率放大器線性化 :高速采樣配合低延遲特性,實時采集放大器輸出信號用于線性化校正。

2. 設計注意事項

- 電源與接地 :AVDD 對噪聲敏感,建議使用低噪聲 LDO 供電,與 DRVDD 通過鐵氧體磁珠 + 電容隔離;各電源引腳就近并聯 0.1 μF 陶瓷去耦電容,PowerPAD 需可靠接地。

- 輸入與時鐘設計 :

- 模擬輸入需差分驅動,建議串聯 5-15Ω 電阻抑制寄生振蕩,輸入共模電壓需匹配 VCM 引腳輸出(0.95 V)。

- 時鐘輸入優先采用差分驅動(如 LVDS/LVPECL),降低共模噪聲干擾;高速采樣時需選用低抖動時鐘源(建議抖動 < 100 fs rms)。

- 接口匹配 :LVDS 輸出需匹配 100Ω 差分負載,走線長度差異控制在 3 mm 內;CMOS 輸出建議串聯 22Ω 電阻抑制反射,負載電容≤5 pF。

- ESD 防護 :芯片 ESD 額定值為人體放電模型(HBM)±2000 V,存儲和操作時需采取防靜電措施,引腳避免懸空。

四、關鍵配置與操作要點

1. 核心功能配置

- 增益與偏移校正 :

- 增益通過寄存器 25h(通道 A)/2Bh(通道 B)配置,0-6 dB 步進 0.5 dB,增益提升時滿量程輸入范圍按比例縮小(0 dB 時 2 VPP,6 dB 時 1 VPP)。

- 偏移校正通過 3Dh 寄存器啟用,校正時間常數由 CFh 寄存器配置,支持添加 - 32 至 + 31 LSB 的偏移基座。

- 輸出接口選擇 :

- 硬件模式:通過 SEN 引腳電平選擇 LVDS/CMOS 接口及數據格式。

- 軟件模式:通過 41h 寄存器配置接口類型,LVDS 擺幅由 01h 寄存器調節(125 mV-570 mV)。

- 功耗管理 :

- 全局掉電:通過 CTRL1 = 高、CTRL2 = 低、CTRL3 = 低觸發,或 45h 寄存器 PDN_GLOBAL 位設置。

- 通道 Standby:通過 CTRL1 = 高、CTRL2 = 低、CTRL3 = 高觸發,僅關閉指定通道 ADC。

2. 操作流程

- 上電與復位 :上電后需等待 AVDD/DRVDD 穩定,通過 RESET 引腳施加≥10 ns 高脈沖復位(串行模式),并行模式需將 RESET 永久接高。

- 寄存器配置 :支持串行(SEN/SCLK/SDATA)與并行兩種配置方式,串行模式可配置增益、偏移校正、接口模式等所有功能,寄存器寫入后需等待 1 個時鐘周期生效。

- 采樣觸發 :無需額外觸發信號,ADC 隨輸入時鐘自動連續采樣,輸出數據與 CLKOUT 同步,默認延遲 16 個時鐘周期(啟用數字功能后延遲 24 個時鐘周期)。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

MSPS

+關注

關注

0文章

574瀏覽量

29006 -

adc

+關注

關注

100文章

7623瀏覽量

556547 -

模數轉換器

+關注

關注

26文章

4044瀏覽量

130201 -

多載波

+關注

關注

0文章

37瀏覽量

12935

發布評論請先 登錄

相關推薦

熱點推薦

ADS4149:一款超低功耗14位的250-MSPS的數模轉換器

本視頻由 TI 工程師和大家一起討論TI最新的高速、低功耗ADC – ADS4149 – 14位, 25

單通道 / 雙通道、14 位 250Msps ADC 系列提供高 SFDR 欠采樣性能

單通道 / 雙通道、14 位 250Msps ADC 系列提供高 SFDR 欠采樣性能

發表于 03-19 07:34

?10次下載

ADS42B49具有模擬輸入緩沖器的雙通道、14位、250MSPS超低功耗ADC數據表

電子發燒友網站提供《ADS42B49具有模擬輸入緩沖器的雙通道、14位、250MSPS超低功耗

發表于 07-17 09:32

?0次下載

ADS4229雙通道、12位、250MSPS超低功耗ADC數據表

電子發燒友網站提供《ADS4229雙通道、12位、250MSPS超低功耗ADC數據表.pdf》資

發表于 07-17 09:34

?1次下載

ADS42xx雙通道、14位/12位、160MSPS/125MSPS/65MSPS、超低功耗ADC數據表

電子發燒友網站提供《ADS42xx雙通道、14位/12位、160MSPS/125

發表于 07-17 09:35

?0次下載

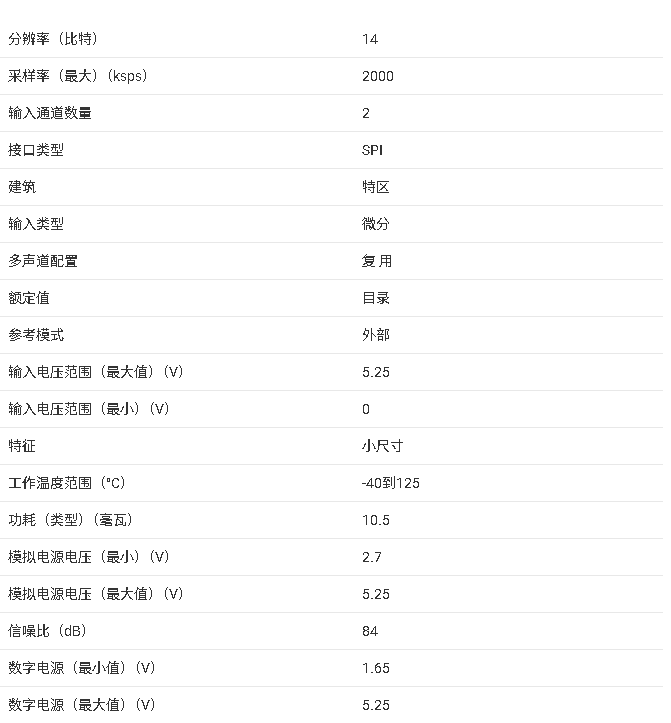

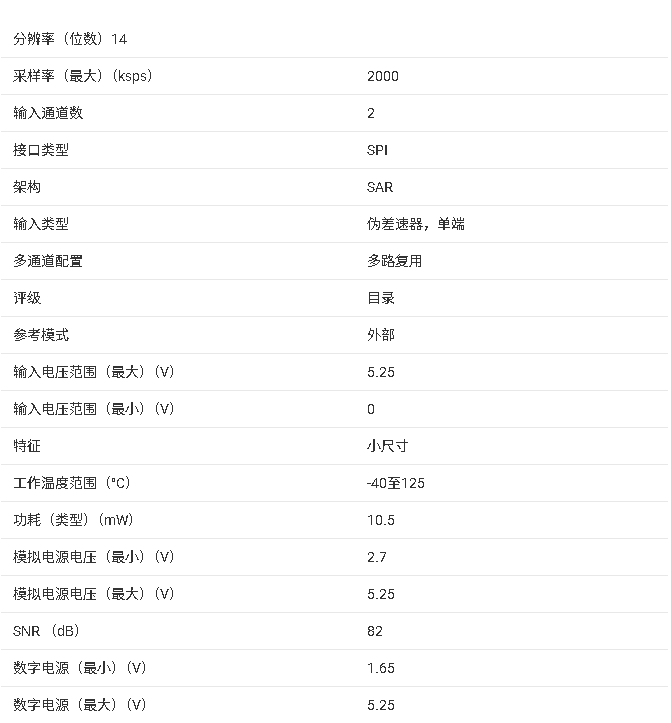

ADS7945/ADS7946 14位、2MSPS、雙通道、差動/單端、超低功耗ADC數據表

電子發燒友網站提供《ADS7945/ADS7946 14位、2MSPS、雙通道、差動/單端、

發表于 07-25 11:47

?0次下載

ADS7945/6 雙通道 14 位 2 MSPS 超低功耗 ADC 技術文檔總結

;該ADS7946與8/10/12位ADS7947/8/9設備在引腳上兼容。這些設備包括一個雙通道輸入復用器和一個低功耗連續逼近寄存器(SA

ADS7946 雙通道 14 位 2 MSPS 超低功耗 ADC 技術文檔總結

;該ADS7946與8/10/12位ADS7947/8/9設備在引腳上兼容。這些設備包括一個雙通道輸入復用器和一個低功耗連續逼近寄存器(SA

ADS4249 雙通道 14 位 250 MSPS 超低功耗 ADC 技術文檔總結

ADS4249 雙通道 14 位 250 MSPS 超低功耗 ADC 技術文檔總結

評論