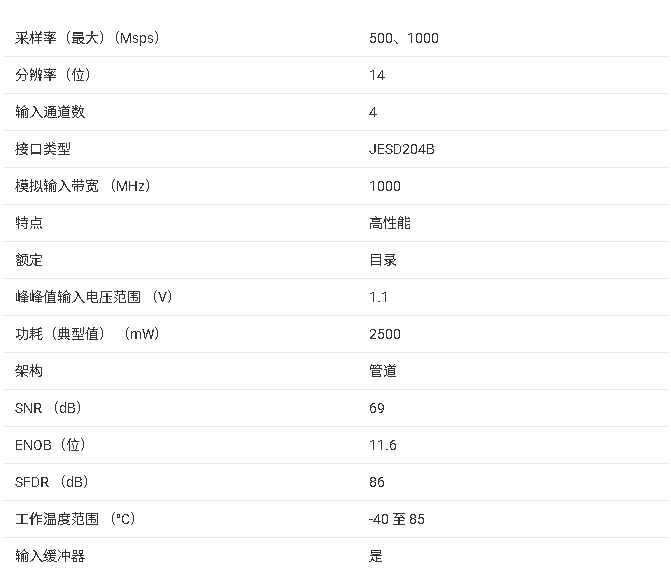

ADS54J64器件是一款四通道、14位、

1GSPS、模數轉換器(ADC),提供寬帶寬、2倍過采樣和高信噪比。該ADS54J64支持數據速率高達 10 Gbps 的JESD204B串行接口,每個通道一個通道。緩沖模擬輸入在寬頻率范圍內提供均勻的阻抗,并最大限度地減少采樣和保持毛刺能量。該ADS54J64在較大的輸入頻率范圍內以極低的功耗提供出色的無雜散動態范圍 (SFDR)。數字信號處理模塊包括復雜的混頻器,然后是低通濾波器,具有2倍和-4倍的射擊選項,支持高達200 MHz的接收帶寬。該ADS54J64還支持DDC旁路模式下的14位、500MSPS輸出。

四通道JESD204B接口簡化了連接,實現了高系統集成密度。內部鎖相環(PLL)將輸入ADC采樣時鐘相乘,以得出用于序列化每個通道的14位數據的位時鐘。

*附件:ads54j64.pdf

特性

- 四通道,14 位分辨率

- 最大采樣率:1 GSPS

- 最大輸出采樣率:500 MSPS

- 高阻抗模擬輸入緩沖器

- 模擬輸入帶寬 (–3 dB):1 GHz

- 輸出選項:

- 使用16位NCO的數字下變頻(DDC)

- DDC 旁路,全速率輸出高達 500 MSPS

- 差分滿量程輸入:1.1 V

聚丙烯 - JESD204B接口:

- 子類 1 支持

- 每個 ADC 1 通道,高達 10 Gbps

- 用于一對通道的專用 SYNC 引腳

- 支持多芯片同步

- 光譜性能:

- f

在= 190 MHz IF,–1 dBFS:- 信噪比:69 dBFS

- NSD:–153 dBFS/Hz

- SFDR:86 dBc(HD2、HD3)、

95 dBFS(非 HD2、HD3)

- f

在= 370 MHz IF,–3 dBFS:- 信噪比:68.5 dBFS

- NSD:–152.5 dBFS/Hz

- SFDR:80 dBc(HD2、HD3)、

86 dBFS(非 HD2、HD3)

- f

- 72引腳VQFN封裝(10 mm×10 mm)

- 功耗:625 mW/通道,總功率 2.5 W

- 電源:1.15 V、1.15 V、1.9 V

參數

ADS54J64 是一款四通道 14 位 1-GSPS 高速模數轉換器(ADC),具備 2 倍過采樣能力與復雜數字下變頻器(DDC),支持 JESD204B 高速串行接口,專為寬帶接收機設計,適用于蜂窩基站、雷達、軟件無線電(SDR)、醫療成像等對動態范圍和采樣速率要求嚴苛的場景。

核心參數與特性

- 性能規格 :單通道功耗 625 mW,總功耗 2.5 W;信噪比(SNR)最高 69.9 dBFS,無雜散動態范圍(SFDR)最高 100.99 dBc,總諧波失真(THD)低至 -115 dB,共模抑制比(CMRR)110 dB。

- 采樣與輸入 :最大采樣率 1 GSPS,輸出采樣率最高 500 MSPS(DDC 旁路模式);模擬輸入帶寬 1 GHz,差分滿量程輸入 1.1 VPP,輸入阻抗 4 kΩ,支持 LVDS/LVPECL 時鐘輸入。

- 信號處理 :內置 16 位數控振蕩器(NCO)與兩級抽取濾波器(抽取比 2/4),支持線性 / 最小相位響應,可編程高通 / 低通濾波,提供 8 種工作模式適配不同帶寬與輸出格式需求。

- 接口與同步 :JESD204B 接口支持 1 通道 / 1 lane 配置,單 lane 速率高達 10 Gbps;支持多芯片同步,提供 SYNCb 引腳實現通道對同步,SYSREF 信號用于時鐘相位對齊。

- 封裝與環境 :72 引腳 VQFN 封裝(10.00mm×10.00mm),工作溫度范圍 -40°C 至 +85°C,ESD 防護等級 HBM ±2000V。

關鍵功能說明

- 多模式信號處理 :支持 DDC 旁路、IQ 輸出、實數輸出、雙 ADC 交織平均等模式,最高可實現 200 MHz 接收帶寬,滿足不同信號解調需求。

- 高速接口傳輸 :JESD204B 接口支持子類 1 同步,內置 8b/10b 編碼與擾碼功能,支持通道交叉切換與 lane 對齊,簡化多芯片互聯布局。

- 過范圍與校準 :具備快速過范圍指示(FOVR)功能,可通過寄存器配置閾值;支持 ADC 自校準與 trim 加載,保障寬溫范圍內的精度穩定性。

- 靈活供電與功耗控制 :采用 1.15 V(AVDD/DVDD)和 1.9 V(AVDD19)多電源供電,支持全局 / 通道級電源管理,快速掉電模式響應時間僅 5 μs。

典型應用場景

主要用于多載波多模式蜂窩基站、電信接收機、雷達與天線陣列、DOCSIS 3.1 電纜調制解調器終端系統(CMTS)、通信測試設備、微波接收機、軟件無線電(SDR)及醫療成像與診斷設備。

應用設計要點

- 電源配置 :模擬電源(AVDD/AVDD19)與數字電源(DVDD)需獨立供電,每個電源引腳就近配置 0.1 μF 去耦電容,電源軌需添加 10 μF 大電容增強濾波。

- 時鐘與同步 :選用低抖動時鐘源(推薦外部時鐘抖動 < 100 fs rms),時鐘輸入需 AC 耦合,支持 LVDS/LVPECL 標準;多芯片同步時需統一 SYSREF 信號,確保 lane 間時序對齊。

- 布局與布線 :模擬輸入與數字輸出走線分離,避免平行布線;模擬輸入采用差分走線并匹配長度,JESD204B 高速信號線需控制阻抗(50 Ω 單端 / 100 Ω 差分),減少反射。

- 配置與校準 :上電后需執行硬件復位與軟件初始化,按應用場景選擇工作模式與抽取比;啟用 ADC 校準功能(校準時間約 2 ms),加載對應速率的 trim 參數以優化線性度。

-

濾波器

+關注

關注

162文章

8421瀏覽量

185984 -

adc

+關注

關注

100文章

7567瀏覽量

556493 -

串行接口

+關注

關注

3文章

520瀏覽量

45285 -

模數轉換器

+關注

關注

26文章

4028瀏覽量

130183

發布評論請先 登錄

貿澤電子備貨TI四通道1 GSPSADS54J64模數轉換器,高信噪比、高帶寬和500 MSPS

ADS54J64EVM如何設置才能實現983.04M的采集速率?

請問ADS54J64器件手冊給出的最大輸出采樣率500MSPS,最大采樣率1GSPS,是什么意思?

請問ADS54J64 datasheet中給出的最大采樣率(1GSPS)與最大輸出采樣率(500MSPS)之間的區別是什么?

ADS54J64EVM開發板可以配套使用哪些Xilinx FPGA開發板呢?

ADS54J54IRGCT用示波器觀測SYNC信號一直為低,為什么?

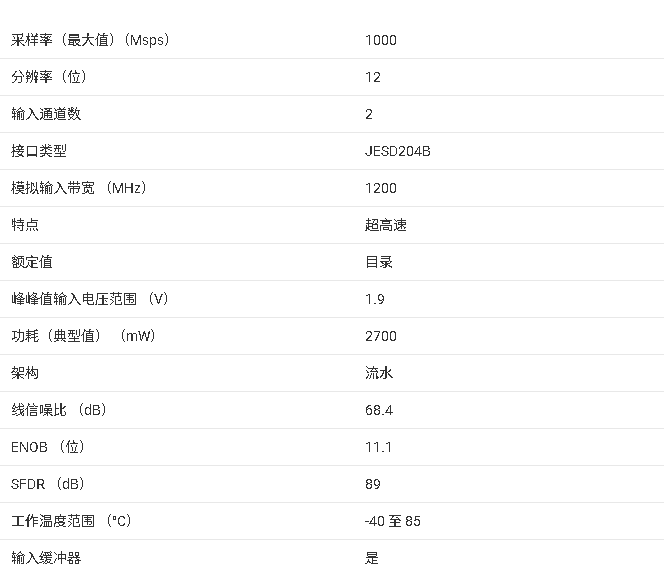

ADS54J60IRMP產品介紹

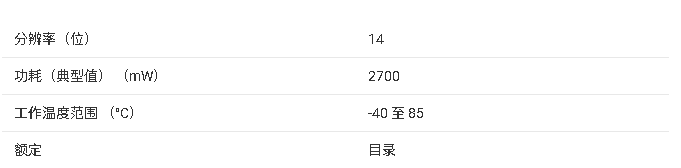

ADS58J64 四通道 14 位 1GSPS 電信接收器和反饋 IC

ADS54J54四通道14位500MSPS ADC數據表

ADS54J64四通道、14位、1GSPS、2倍過采樣模數轉換器數據表

ADS58J64 技術文檔核心總結

ADS54J20 雙通道 12 位 1.0-GSPS ADC 核心信息總結

ADS58J63 產品核心信息總結

ADS52J90 產品核心信息總結

ADS54T02 產品核心信息總結

ADS54J64 產品核心信息總結

ADS54J64 產品核心信息總結

評論